Một chiều với nhiều đầu vào hơn

Các mạch cổng lấy mẫu đơn hướng mà chúng ta đã thảo luận cho đến nay có một đầu vào duy nhất. Trong chương này, chúng ta hãy thảo luận thêm một vài mạch cổng lấy mẫu đơn hướng có thể xử lý nhiều hơn một tín hiệu đầu vào.

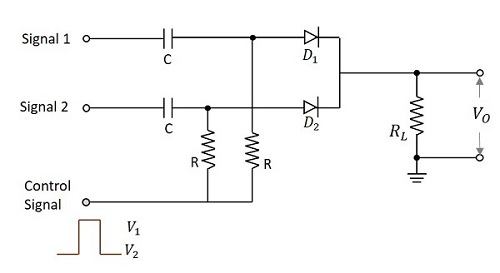

Mạch cổng lấy mẫu một chiều bao gồm các tụ điện và điện trở có cùng giá trị. Ở đây, hai cổng lấy mẫu diode một chiều đầu vào với hai đầu vào được xem xét. Trong đoạn mạch này ta có hai tụ điện và hai điện trở cùng giá trị. Chúng được kết nối với hai điốt mỗi.

Tín hiệu điều khiển được áp dụng tại các điện trở. Đầu ra được đưa qua điện trở tải. Hình dưới đây cho thấy sơ đồ mạch cho cổng lấy mẫu diode một chiều với nhiều hơn một tín hiệu đầu vào.

Khi đầu vào điều khiển được đưa ra,

Tại V C = V 1 trong thời gian truyền sóng, cả điốt D 1 và D 2 đều phân cực thuận. Bây giờ, đầu ra sẽ là tổng của cả ba đầu vào.

$$ V_O = V_ {S1} + V_ {S2} + V_C $$

Với V 1 = 0v là giá trị lý tưởng,

$$ V_O = V_ {S1} + V_ {S2} $$

Ở đây chúng tôi có một hạn chế lớn là tại bất kỳ thời điểm nào, trong suốt thời gian truyền tải, chỉ nên áp dụng một đầu vào. Đây là một nhược điểm của mạch này.

Trong thời gian không truyền,

$$ V_C = V_2 $$

Cả hai điốt sẽ bị phân cực ngược có nghĩa là bị hở mạch.

Điều này làm cho đầu ra

$$ V_O = 0V $$

Nhược điểm chính của mạch này là loading of the circuittăng khi số lượng đầu vào tăng lên. Hạn chế này có thể tránh được bằng một mạch khác trong đó đầu vào điều khiển được đưa ra sau điốt tín hiệu đầu vào.

Giảm bệ

Trong khi đi qua các loại cổng lấy mẫu khác nhau và đầu ra mà chúng tạo ra, chúng tôi đã bắt gặp một mức điện áp bổ sung trong các dạng sóng đầu ra được gọi là Pedestal. Điều này là không mong muốn và tạo ra một số tiếng ồn.

Giảm bệ trong mạch Cổng

Sự khác biệt về tín hiệu đầu ra trong thời gian truyền và thời gian không truyền mặc dù tín hiệu đầu vào không được áp dụng, được gọi là Pedestal. Nó có thể là một bệ tích cực hoặc một bệ tiêu cực.

Do đó nó là đầu ra được quan sát vì điện áp gating mặc dù tín hiệu đầu vào không có. Điều này là không mong muốn và phải được giảm bớt. Mạch bên dưới được thiết kế để giảm bệ trong mạch cổng.

Khi tín hiệu điều khiển được đưa vào, trong khoảng thời gian truyền tức là tại V 1 , Q 1 BẬT và Q 2 TẮT và V CC được đưa qua R C đến Q 1 . Trong khi trong khoảng thời gian không truyền, tức là tại V 2 , Q 2 BẬT và Q 1 TẮT và V CC được đưa qua R C đến Q 2 . Các điện áp cơ bản –V BB1 và –V BB2 và biên độ của tín hiệu cổng được điều chỉnh để hai dòng điện bán dẫn giống hệt nhau và kết quả là mức điện áp đầu ra tĩnh sẽ không đổi.

Nếu điện áp xung cổng lớn hơn so với V BE của các bóng bán dẫn, thì mỗi bóng bán dẫn bị phân cực thấp hơn nhiều so với cắt, khi nó không dẫn điện. Vì vậy, khi điện áp cổng xuất hiện, Q 2 sẽ bị cắt trước khi Q 1 bắt đầu dẫn, trong khi ở cuối cổng, Q 1 sẽ bị cắt trước khi Q 2 bắt đầu dẫn.

Hình dưới đây giải thích điều này theo cách tốt hơn.

Do đó các tín hiệu cổng xuất hiện như trong hình trên. Điện áp tín hiệu gated sẽ xuất hiện chồng lên dạng sóng này. Các xung đột này sẽ có giá trị không đáng kể nếu thời gian tăng dạng sóng cổng nhỏ so với thời gian cổng.

Có ít drawbacks của mạch này chẳng hạn như

Thời gian tăng và giảm xác định, dẫn đến tăng đột biến

Dòng điện liên tục qua RC tản nhiệt rất nhiều

Hai điện áp phân cực và hai nguồn tín hiệu điều khiển (bổ sung cho nhau) làm cho mạch phức tạp.

Ngoài những nhược điểm này, mạch này rất hữu ích trong việc giảm bệ đỡ trong mạch cổng.