Eingebettete Systeme - Architekturtypen

Die 8051-Mikrocontroller arbeiten mit einem 8-Bit-Datenbus. Sie können also einen externen Datenspeicher von bis zu 64 KB und einen externen Programmspeicher von höchstens 64 KB unterstützen. Insgesamt können 8051-Mikrocontroller 128 KB externen Speicher adressieren.

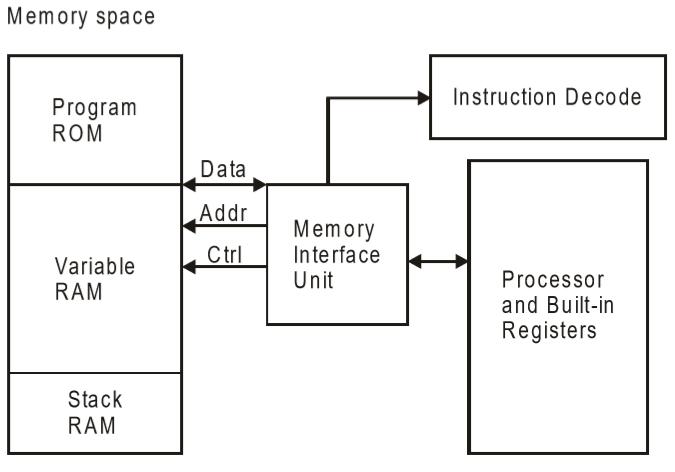

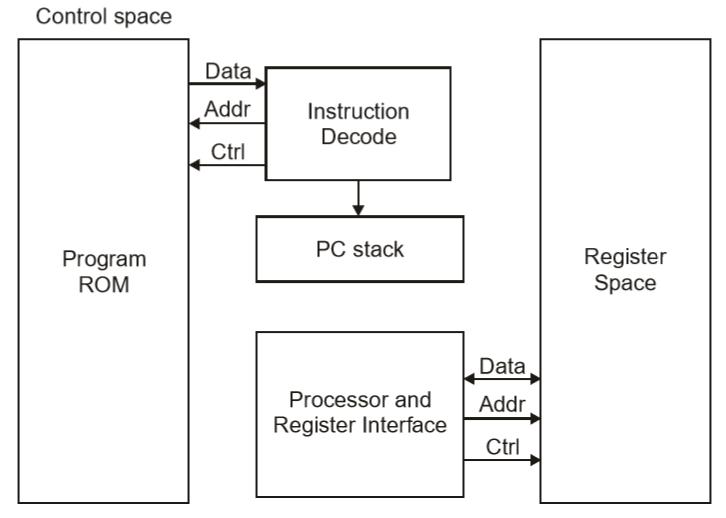

Wenn Daten und Code in unterschiedlichen Speicherblöcken liegen, wird die Architektur als bezeichnet Harvard architecture. Wenn Daten und Code im selben Speicherblock liegen, wird die Architektur als bezeichnetVon Neumann architecture.

Von Neumann Architektur

Die Von Neumann-Architektur wurde zuerst von einem Informatiker John von Neumann vorgeschlagen. In dieser Architektur existiert ein Datenpfad oder Bus sowohl für Befehl als auch für Daten. Infolgedessen führt die CPU jeweils eine Operation aus. Es ruft entweder einen Befehl aus dem Speicher ab oder führt eine Lese- / Schreiboperation für Daten durch. Ein Befehlsabruf und eine Datenoperation können also nicht gleichzeitig erfolgen, wenn ein gemeinsamer Bus gemeinsam genutzt wird.

Die Von-Neumann-Architektur unterstützt einfache Hardware. Es ermöglicht die Verwendung eines einzelnen sequentiellen Speichers. Die heutige Verarbeitungsgeschwindigkeit übertrifft die Speicherzugriffszeiten erheblich, und wir verwenden eine sehr schnelle, aber kleine Menge an Speicher (Cache) lokal im Prozessor.

Harvard-Architektur

Die Harvard-Architektur bietet separate Speicher- und Signalbusse für Anweisungen und Daten. Diese Architektur enthält einen Datenspeicher, der vollständig in der CPU enthalten ist, und es gibt keinen Zugriff auf den Befehlsspeicher als Daten. Computer verfügen über separate Speicherbereiche für Programmanweisungen und Daten mithilfe interner Datenbusse, die den gleichzeitigen Zugriff auf Anweisungen und Daten ermöglichen.

Programme mussten von einem Bediener geladen werden; Der Prozessor konnte sich nicht selbst booten. In einer Harvard-Architektur müssen die beiden Speicher keine gemeinsamen Eigenschaften aufweisen.

Von-Neumann-Architektur gegen Harvard-Architektur

Die folgenden Punkte unterscheiden die Von Neumann-Architektur von der Harvard-Architektur.

| Von-Neumann-Architektur | Harvard-Architektur |

|---|---|

| Einzelner Speicher, der von Code und Daten gemeinsam genutzt werden kann. | Separate Speicher für Code und Daten. |

| Der Prozessor muss Code in einem separaten Taktzyklus und Daten in einem anderen Taktzyklus abrufen. Es sind also zwei Taktzyklen erforderlich. | Ein einziger Taktzyklus ist ausreichend, da separate Busse für den Zugriff auf Code und Daten verwendet werden. |

| Höhere Geschwindigkeit und damit weniger Zeitaufwand. | Langsamer in der Geschwindigkeit und damit zeitaufwändiger. |

| Einfach im Design. | Komplex im Design. |

CISC und RISC

CISC ist ein komplexer Befehlssatzcomputer. Es ist ein Computer, der eine große Anzahl von Anweisungen adressieren kann.

In den frühen 1980er Jahren empfahlen Computerdesigner, dass Computer mit einfachen Konstrukten weniger Anweisungen verwenden sollten, damit sie innerhalb der CPU viel schneller ausgeführt werden können, ohne Speicher verwenden zu müssen. Solche Computer werden als Reduced Instruction Set Computer oder RISC klassifiziert.

CISC gegen RISC

Die folgenden Punkte unterscheiden ein CISC von einem RISC -

| CISC | RISC |

|---|---|

| Größere Anweisungen. Einfach zu programmieren | Kleinere Anweisungen. Schwer zu programmieren. |

| Einfacheres Design des Compilers unter Berücksichtigung größerer Anweisungen. | Komplexes Design des Compilers. |

| Viele Adressierungsmodi verursachen komplexe Befehlsformate. | Nur wenige Adressierungsmodi, Befehlsformat korrigieren. |

| Die Befehlslänge ist variabel. | Die Befehlslänge variiert. |

| Höhere Taktzyklen pro Sekunde. | Niedriger Taktzyklus pro Sekunde. |

| Der Schwerpunkt liegt auf Hardware. | Der Schwerpunkt liegt auf Software. |

| Die Steuereinheit implementiert einen großen Befehlssatz unter Verwendung einer Mikroprogrammeinheit. | Jeder Befehl ist von der Hardware auszuführen. |

| Langsamere Ausführung, da Anweisungen aus dem Speicher gelesen und von der Decodereinheit decodiert werden sollen. | Schnellere Ausführung, da jeder Befehl von der Hardware ausgeführt werden soll. |

| Pipelining ist nicht möglich. | Das Pipelining von Anweisungen ist unter Berücksichtigung eines einzelnen Taktzyklus möglich. |