Multiprocesseurs et multi-ordinateurs

Nous aborderons les multiprocesseurs et les multi-ordinateurs dans ce chapitre.

Interconnexions système multiprocesseur

Le traitement parallèle nécessite l'utilisation d'interconnexions système efficaces pour une communication rapide entre les périphériques d'entrée / sortie et les périphériques, les multiprocesseurs et la mémoire partagée.

Systèmes de bus hiérarchiques

Un système de bus hiérarchique consiste en une hiérarchie de bus reliant divers systèmes et sous-systèmes / composants dans un ordinateur. Chaque bus est composé d'un certain nombre de lignes de signal, de commande et d'alimentation. Différents bus tels que les bus locaux, les bus de fond de panier et les bus d'E / S sont utilisés pour exécuter différentes fonctions d'interconnexion.

Les bus locaux sont les bus implémentés sur les cartes de circuits imprimés. Un bus de fond de panier est un circuit imprimé sur lequel de nombreux connecteurs sont utilisés pour brancher des cartes fonctionnelles. Les bus qui connectent des périphériques d'entrée / sortie à un système informatique sont appelés bus d'E / S.

Commutateur crossbar et mémoire multiport

Les réseaux commutés fournissent des interconnexions dynamiques entre les entrées et les sorties. Les systèmes de petite ou moyenne taille utilisent principalement des réseaux crossbar. Les réseaux à plusieurs étages peuvent être étendus aux systèmes plus grands, si le problème de latence accrue peut être résolu.

L'organisation du commutateur crossbar et de la mémoire multiport est un réseau à une seule étape. Bien qu'un réseau à une seule étape soit moins coûteux à construire, plusieurs passes peuvent être nécessaires pour établir certaines connexions. Un réseau à plusieurs étages a plus d'un étage de boîtiers de commutation. Ces réseaux devraient pouvoir connecter n'importe quelle entrée à n'importe quelle sortie.

Réseaux à plusieurs étages et combinés

Les réseaux à plusieurs étages ou réseaux d'interconnexion à plusieurs étages sont une classe de réseaux informatiques à haut débit qui se compose principalement d'éléments de traitement à une extrémité du réseau et d'éléments de mémoire à l'autre extrémité, connectés par des éléments de commutation.

Ces réseaux sont appliqués pour construire de plus grands systèmes multiprocesseurs. Cela comprend Omega Network, Butterfly Network et bien d'autres.

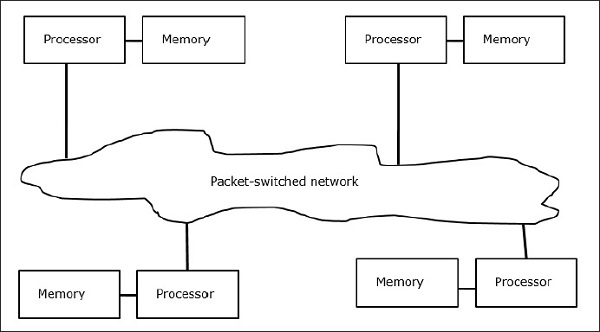

Multicomputers

Les multi-ordinateurs sont des architectures MIMD à mémoire distribuée. Le diagramme suivant montre un modèle conceptuel d'un multi-ordinateur -

Les multi-ordinateurs sont des machines de transmission de messages qui appliquent une méthode de commutation de paquets pour échanger des données. Ici, chaque processeur dispose d'une mémoire privée, mais pas d'espace d'adressage global car un processeur ne peut accéder qu'à sa propre mémoire locale. La communication n'est donc pas transparente: ici les programmeurs doivent mettre explicitement des primitives de communication dans leur code.

Ne pas avoir de mémoire accessible globalement est un inconvénient des multi-ordinateurs. Cela peut être résolu en utilisant les deux schémas suivants -

- Mémoire partagée virtuelle (VSM)

- Mémoire virtuelle partagée (SVM)

Dans ces schémas, le programmeur d'application suppose une grande mémoire partagée qui est globalement adressable. Si nécessaire, les références mémoire faites par les applications sont traduites dans le paradigme de transmission de messages.

Mémoire partagée virtuelle (VSM)

VSM est une implémentation matérielle. Ainsi, le système de mémoire virtuelle du système d'exploitation est implémenté de manière transparente au-dessus de VSM. Ainsi, le système d'exploitation pense qu'il fonctionne sur une machine avec une mémoire partagée.

Mémoire virtuelle partagée (SVM)

SVM est une implémentation logicielle au niveau du système d'exploitation avec prise en charge matérielle de l'unité de gestion de la mémoire (MMU) du processeur. Ici, l'unité de partage est constituée des pages de mémoire du système d'exploitation.

Si un processeur adresse un emplacement mémoire particulier, la MMU détermine si la page mémoire associée à l'accès mémoire se trouve ou non dans la mémoire locale. Si la page n'est pas dans la mémoire, dans un système informatique normal, elle est permutée à partir du disque par le système d'exploitation. Mais, dans SVM, le système d'exploitation récupère la page du nœud distant qui possède cette page particulière.

Trois générations de multi-ordinateurs

Dans cette section, nous aborderons trois générations de multi-ordinateurs.

Choix de conception dans le passé

Lors de la sélection d'une technologie de processeur, un concepteur multi-ordinateurs choisit des processeurs à grain moyen à faible coût comme éléments de base. La majorité des ordinateurs parallèles sont construits avec des microprocesseurs standard du commerce. La mémoire distribuée a été choisie pour les ordinateurs multiples plutôt que l'utilisation de la mémoire partagée, ce qui limiterait l'évolutivité. Chaque processeur possède sa propre unité de mémoire locale.

Pour le schéma d'interconnexion, les multi-ordinateurs ont des réseaux directs point à point de passage de messages plutôt que des réseaux de commutation d'adresses. Pour la stratégie de contrôle, le concepteur de multi-ordinateurs choisit les opérations asynchrones MIMD, MPMD et SMPD. Le Cosmic Cube de Caltech (Seitz, 1983) est le premier multi-ordinateurs de première génération.

Développement présent et futur

Les ordinateurs de nouvelle génération ont évolué de multi-ordinateurs à grain moyen à fin en utilisant une mémoire virtuelle partagée à l'échelle mondiale. Les multi-ordinateurs de deuxième génération sont encore utilisés à l'heure actuelle. Mais en utilisant un meilleur processeur comme i386, i860, etc., les ordinateurs de deuxième génération se sont beaucoup développés.

Les ordinateurs de troisième génération sont les ordinateurs de prochaine génération sur lesquels les nœuds implémentés VLSI seront utilisés. Chaque nœud peut avoir un processeur 14-MIPS, des canaux de routage à 20 Mo / s et 16 Ko de RAM intégrés sur une seule puce.

Le système Intel Paragon

Auparavant, des nœuds homogènes étaient utilisés pour créer des multi-ordinateurs hypercube, car toutes les fonctions étaient données à l'hôte. Donc, cela a limité la bande passante d'E / S. Ainsi, pour résoudre des problèmes à grande échelle de manière efficace ou à haut débit, ces ordinateurs ne pouvaient pas être utilisés. Le système Intel Paragon a été conçu pour surmonter cette difficulté. Il a transformé le multi-ordinateur en un serveur d'applications avec un accès multi-utilisateur dans un environnement réseau.

Mécanismes de transmission de messages

Les mécanismes de transmission de messages dans un réseau multi-ordinateurs nécessitent une prise en charge matérielle et logicielle spéciale. Dans cette section, nous discuterons de certains schémas.

Schémas de routage des messages

Dans le multi-ordinateur avec schéma de routage de stockage et de transfert, les paquets sont la plus petite unité de transmission d'informations. Dans les réseaux routés par trou de ver, les paquets sont ensuite divisés en flits. La longueur du paquet est déterminée par le schéma de routage et l'implémentation du réseau, tandis que la longueur du flit est affectée par la taille du réseau.

Dans Store and forward routing, les paquets sont l'unité de base de la transmission d'informations. Dans ce cas, chaque nœud utilise un tampon de paquets. Un paquet est transmis d'un nœud source à un nœud de destination via une séquence de nœuds intermédiaires. La latence est directement proportionnelle à la distance entre la source et la destination.

Dans wormhole routing, la transmission du nœud source au nœud de destination se fait via une séquence de routeurs. Tous les flits d'un même paquet sont transmis de manière inséparable en pipeline. Dans ce cas, seul le flit d'en-tête sait où va le paquet.

Blocage et canaux virtuels

Un canal virtuel est un lien logique entre deux nœuds. Il est formé par un tampon flit dans le nœud source et le nœud récepteur, et un canal physique entre eux. Lorsqu'un canal physique est alloué pour une paire, un tampon source est couplé avec un tampon récepteur pour former un canal virtuel.

Lorsque tous les canaux sont occupés par des messages et qu'aucun des canaux du cycle n'est libéré, une situation de blocage se produit. Pour éviter cela, un schéma de contournement des blocages doit être suivi.