Design VLSI - Tecnologia FPGA

FPGA - Introduzione

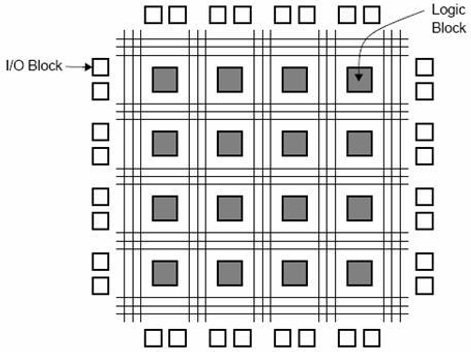

La forma completa di FPGA è "Field Programmable Gate Array". Contiene da diecimila a più di un milione di porte logiche con interconnessione programmabile. Sono disponibili interconnessioni programmabili per utenti o progettisti per eseguire facilmente determinate funzioni. Un tipico chip FPGA modello è mostrato nella figura data. Sono disponibili blocchi I / O, progettati e numerati in base alla funzione. Per ogni modulo di composizione a livello logico, ci sonoCLB’s (Configurable Logic Blocks).

CLB esegue l'operazione logica assegnata al modulo. L'interconnessione tra CLB e blocchi I / O viene effettuata con l'ausilio di canali di instradamento orizzontali, canali di instradamento verticali e PSM (Multiplexer programmabili).

Il numero di CLB che contiene decide solo la complessità dell'FPGA. Le funzionalità di CLB e PSM sono progettate da VHDL o da qualsiasi altro linguaggio descrittivo dell'hardware. Dopo la programmazione, CLB e PSM vengono posizionati su chip e collegati tra loro con canali di routing.

Vantaggi

- Richiede pochissimo tempo; partendo dal processo di progettazione al chip funzionale.

- Non sono coinvolte fasi di produzione fisica.

- L'unico svantaggio è che è costoso rispetto ad altri stili.

Gate Array Design

Il gate array (GA)è al secondo posto dopo l'FPGA, in termini di capacità di prototipazione rapida. Sebbene la programmazione utente sia importante per l'implementazione del progetto del chip FPGA, la progettazione e l'elaborazione della maschera metallica viene utilizzata per GA. L'implementazione del gate array richiede un processo di produzione in due fasi.

La prima fase si traduce in una serie di transistor non impegnati su ciascun chip GA. Questi chip non impegnati possono essere memorizzati per una successiva personalizzazione, che viene completata definendo le interconnessioni metalliche tra i transistor della matrice. La modellazione delle interconnessioni metalliche viene eseguita alla fine del processo di fabbricazione del chip, in modo che il tempo di consegna possa essere ancora breve, da pochi giorni a poche settimane. La figura riportata di seguito mostra le fasi di elaborazione di base per l'implementazione del gate array.

Le tipiche piattaforme di array di porte utilizzano aree dedicate chiamate canali, per l'instradamento tra le celle tra righe o colonne di transistor MOS. Semplificano le interconnessioni. I modelli di interconnessione che eseguono porte logiche di base sono memorizzati in una libreria, che può quindi essere utilizzata per personalizzare le righe di transistor non impegnati in base alla netlist.

Nella maggior parte dei GA moderni, vengono utilizzati più strati di metallo per il routing dei canali. Con l'uso di più strati interconnessi, l'instradamento può essere ottenuto sulle aree delle celle attive; in modo che i canali di instradamento possano essere rimossi come nei chip Sea-of-Gates (SOG). Qui, l'intera superficie del chip è coperta da transistor nMOS e pMOS non impegnati. I transistor vicini possono essere personalizzati utilizzando una maschera metallica per formare porte logiche di base.

Per l'instradamento tra le celle, alcuni dei transistor non impegnati devono essere sacrificati. Questo stile di progettazione si traduce in una maggiore flessibilità per le interconnessioni e di solito in una densità maggiore. Il fattore di utilizzo del chip GA è misurato dall'area del chip utilizzata divisa per l'area totale del chip. È superiore a quella dell'FPGA, così come la velocità del chip.

Design basato su celle standard

Un design basato su celle standard richiede lo sviluppo di un set completo di maschere personalizzate. La cella standard è anche nota come polycell. In questo approccio, tutte le celle logiche di uso comune vengono sviluppate, caratterizzate e memorizzate in una libreria di celle standard.

Una libreria può contenere alcune centinaia di celle, inclusi inverter, porte NAND, porte NOR, AOI complessi, porte OAI, D-latch e Flip-flop. Ogni tipo di cancello può essere implementato in diverse versioni per fornire capacità di pilotaggio adeguate per diversi fan-out. Il gate dell'inverter può avere dimensioni standard, doppie e quadruple in modo che il progettista del chip possa selezionare la dimensione corretta per ottenere velocità del circuito e densità di layout elevate.

Ogni cella è caratterizzata secondo diverse categorie di caratterizzazione differenti, come,

- Tempo di ritardo rispetto alla capacità di carico

- Modello di simulazione del circuito

- Modello di simulazione temporale

- Modello di simulazione dei guasti

- Dati della cella per luogo e percorso

- Dati maschera

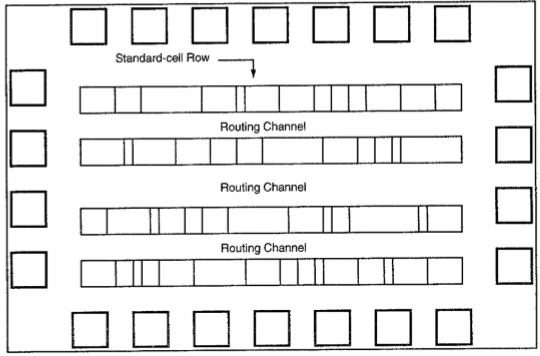

Per il posizionamento automatizzato delle celle e il routing, ogni layout di cella è progettato con un'altezza fissa, in modo che un numero di celle possa essere delimitato fianco a fianco per formare righe. I binari di alimentazione e di terra corrono paralleli ai limiti superiore e inferiore della cella. In questo modo, le celle adiacenti condividono un bus di alimentazione comune e un bus di terra comune. La figura mostrata di seguito è una planimetria per la progettazione basata su celle standard.

Design completamente personalizzato

In un design completamente personalizzato, l'intero design della maschera viene rinnovato, senza l'uso di alcuna libreria. Il costo di sviluppo di questo stile di design è in aumento. Pertanto, il concetto di riutilizzo del design sta diventando famoso per ridurre i tempi del ciclo di progettazione e i costi di sviluppo.

Il design completamente personalizzato più difficile può essere il design di una cella di memoria, sia statica che dinamica. Per la progettazione di chip logici, è possibile ottenere una buona negoziazione utilizzando una combinazione di diversi stili di progettazione sullo stesso chip, ovvero celle standard, celle di percorso dati eprogrammable logic arrays (PLAs).

In pratica, il progettista esegue il layout completamente personalizzato, ovvero la geometria, l'orientamento e il posizionamento di ogni transistor. La produttività del progetto è generalmente molto bassa; tipicamente poche decine di transistor al giorno, per progettista. Nel CMOS digitale VLSI, il design completamente personalizzato viene utilizzato raramente a causa dell'elevato costo della manodopera. Questi stili di progettazione includono la progettazione di prodotti ad alto volume come chip di memoria, microprocessori ad alte prestazioni e FPGA.