マイクロプロセッサ-クイックガイド

マイクロプロセッサは、マイクロコンピュータの制御ユニットであり、ALU(算術論理演算装置)操作を実行し、それに接続されている他のデバイスと通信できる小さなチップ上に製造されています。

マイクロプロセッサは、ALU、レジスタアレイ、および制御ユニットで構成されています。ALUは、メモリまたは入力デバイスから受信したデータに対して算術演算および論理演算を実行します。レジスタ配列は、B、C、D、E、H、L、アキュムレータなどの文字で識別されるレジスタで構成されます。コントロールユニットは、コンピュータ内のデータと命令の流れを制御します。

基本的なマイクロコンピューターのブロック図

マイクロプロセッサはどのように機能しますか?

マイクロプロセッサは、フェッチ、デコード、実行のシーケンスに従います。

最初に、命令は順番にメモリに保存されます。マイクロプロセッサはそれらの命令をメモリからフェッチし、それをデコードして、STOP命令に達するまでそれらの命令を実行します。後で、結果をバイナリで出力ポートに送信します。これらのプロセス間で、レジスタは一時データを格納し、ALUはコンピューティング機能を実行します。

マイクロプロセッサで使用される用語のリスト

これは、マイクロプロセッサで頻繁に使用される用語のリストです。

Instruction Set −マイクロプロセッサが理解できる一連の命令です。

Bandwidth −1つの命令で処理されるビット数です。

Clock Speed−プロセッサが実行できる1秒あたりの操作数を決定します。メガヘルツ(MHz)またはギガヘルツ(GHz)で表されます。クロックレートとも呼ばれます。

Word Length−内部データバス、レジスタ、ALUなどの幅によって異なります。8ビットマイクロプロセッサは、一度に8ビットデータを処理できます。ワード長は、マイクロコンピュータのタイプに応じて4ビットから64ビットの範囲です。

Data Types −マイクロプロセッサには、2進数、BCD、ASCII、符号付きおよび符号なしの数値など、複数のデータ型形式があります。

マイクロプロセッサの機能

これは、マイクロプロセッサの最も顕著な機能のいくつかのリストです-

Cost-effective −マイクロプロセッサチップは低価格で入手可能であり、その結果、低コストになります。

Size −マイクロプロセッサは小型チップであるため、ポータブルです。

Low Power Consumption −マイクロプロセッサは、低消費電力の金属酸化物半導体技術を使用して製造されています。

Versatility −ソフトウェアプログラムを構成することにより、多くのアプリケーションで同じチップを使用できるため、マイクロプロセッサは用途が広い。

Reliability −マイクロプロセッサのICの故障率は非常に低いため、信頼性があります。

マイクロプロセッサは3つのカテゴリに分類できます-

RISCプロセッサ

RISCは Reduced Instruction Set Computer。コンピュータの命令セットを簡素化することにより、実行時間を短縮するように設計されています。RISCプロセッサを使用すると、各命令を実行するのに1クロックサイクルしか必要とせず、結果が均一に実行されます。これにより、コード行が増えるため効率が低下するため、命令を格納するためにより多くのRAMが必要になります。コンパイラはまた、高級言語の命令を機械語に変換するためにさらに作業する必要があります。

RISCプロセッサの一部は次のとおりです。

- Power PC:601、604、615、620

- DEC Alpha:210642、211066、21068、21164

- MIPS:TS(R10000)RISCプロセッサー

- PA-RISC:HP 7100LC

RISCのアーキテクチャ

RISCマイクロプロセッサアーキテクチャは、高度に最適化された一連の命令を使用します。電力効率が高いため、AppleiPodなどのポータブルデバイスで使用されています。

RISCの特徴

RISCプロセッサの主な特徴は次のとおりです。

簡単な説明で構成されています。

さまざまなデータ型形式をサポートしています。

パイプライン化には、単純なアドレッシングモードと固定長の命令を利用します。

あらゆるコンテキストで使用するレジスタをサポートします。

1サイクルの実行時間。

「LOAD」および「STORE」命令は、メモリ位置にアクセスするために使用されます。

多数のレジスタで構成されています。

それはより少ない数のトランジスタで構成されています。

CISCプロセッサ

CISCの略 Complex Instruction Set Computer。命令あたりのサイクル数を無視して、プログラムあたりの命令数を最小限に抑えるように設計されています。複雑な命令をハードウェアに直接組み込むことに重点が置かれています。

コードの長さが比較的短いため、コンパイラーは高水準言語をアセンブリレベルの言語/マシンコードに変換するためにほとんど作業を行う必要がなく、命令を格納するために必要なRAMはごくわずかです。

CISCプロセッサの一部は次のとおりです。

- IBM 370/168

- VAX 11/780

- Intel 80486

CISCのアーキテクチャ

そのアーキテクチャは、より大きなプログラムでより多くのストレージが必要になり、メモリコストが高くなるため、メモリコストを削減するように設計されています。これを解決するために、1つの命令に操作の数を埋め込むことにより、プログラムごとの命令の数を減らすことができます。

CISCの特徴

- さまざまなアドレッシングモード。

- 命令の数が多い。

- 可変長の命令フォーマット。

- 1つの命令を実行するには、数サイクルかかる場合があります。

- 命令デコードロジックは複雑です。

- 複数のアドレッシングモードをサポートするには、1つの命令が必要です。

特別なプロセッサ

これらは、いくつかの特別な目的のために設計されたプロセッサです。特別なプロセッサのいくつかについて簡単に説明します-

コプロセッサー

コプロセッサーは特別に設計されたマイクロプロセッサーであり、通常のマイクロプロセッサーよりも何倍も速くその特定の機能を処理できます。

For example −数学コプロセッサー。

一部のIntel数学コプロセッサは次のとおりです。

- 8087-8086で使用

- 80287-80286で使用

- 80387-80386で使用

入出力プロセッサ

これは、独自のローカルメモリを備えた特別に設計されたマイクロプロセッサであり、CPUの関与を最小限に抑えてI / Oデバイスを制御するために使用されます。

For example −

- DMA(ダイレクトメモリアクセス)コントローラー

- キーボード/マウスコントローラー

- グラフィックディスプレイコントローラー

- SCSIポートコントローラー

トランスピュータ(トランジスタコンピュータ)

トランスピュータは、独自のローカルメモリを備え、プロセッサ間通信のために1つのトランスピュータを別のトランスピュータに接続するためのリンクを持つ特別に設計されたマイクロプロセッサです。1980年にInmosによって最初に設計され、VLSI技術の利用を対象としています。

トランスピュータは、シングルプロセッサシステムとして使用することも、外部リンクに接続することもできます。これにより、建設コストが削減され、パフォーマンスが向上します。

For example − 16ビットT212、32ビットT425、浮動小数点(T800、T805、およびT9000)プロセッサ。

DSP(デジタルシグナルプロセッサ)

このプロセッサは、アナログ信号をデジタル形式に処理するように特別に設計されています。これは、一定の時間間隔で電圧レベルをサンプリングし、その瞬間の電圧をデジタル形式に変換することによって行われます。このプロセスは、アナログ-デジタルコンバーター、A-DコンバーターまたはADCと呼ばれる回路によって実行されます。

DSPには次のコンポーネントが含まれています-

Program Memory −DSPがデータを処理するために使用するプログラムを格納します。

Data Memory −処理する情報を格納します。

Compute Engine −プログラムメモリからプログラムにアクセスし、データメモリからデータにアクセスして、数学的処理を実行します。

Input/Output −それは外の世界に接続します。

そのアプリケーションは-

- 音と音楽の統合

- オーディオとビデオの圧縮

- ビデオ信号処理

- 2Dおよび3Dグラフィックスアクセラレーション。

For example − TexasInstrumentのTMS320シリーズ(TMS 320C40、TMS320C50など)。

8085は「85」マイクロプロセッサと発音されます。これは、1977年にIntelがNMOSテクノロジを使用して設計した8ビットマイクロプロセッサです。

次の構成になっています-

- 8ビットデータバス

- 最大64KBをアドレス指定できる16ビットアドレスバス

- 16ビットプログラムカウンタ

- 16ビットスタックポインタ

- ペアで配置された6つの8ビットレジスタ:BC、DE、HL

- 3.2 MHZ単相クロックで動作するには、+ 5V電源が必要です

洗濯機、電子レンジ、携帯電話などに使用されています。

8085マイクロプロセッサ–機能ユニット

8085は次の機能ユニットで構成されています-

アキュムレータ

これは、算術、論理、I / O、およびLOAD / STORE操作を実行するために使用される8ビットレジスタです。内部データバスとALUに接続されています。

算術論理演算装置

名前が示すように、8ビットデータに対して加算、減算、AND、ORなどの算術演算および論理演算を実行します。

汎用レジスタ

8085プロセッサには6つの汎用レジスタ、つまりB、C、D、E、H、Lがあります。各レジスタは8ビットデータを保持できます。

これらのレジスタはペアで動作して16ビットデータを保持でき、ペアリングの組み合わせはBC、DE、HLのようになります。

プログラムカウンター

これは、次に実行される命令のメモリアドレス位置を格納するために使用される16ビットレジスタです。マイクロプロセッサは、命令が実行されるたびにプログラムをインクリメントするため、プログラムカウンタは、実行される次の命令のメモリアドレスを指します。

スタックポインタ

また、16ビットレジスタはスタックのように機能し、プッシュおよびポップ操作中に常に2ずつインクリメント/デクリメントされます。

一時登録

これは、算術演算および論理演算の一時データを保持する8ビットレジスタです。

フラグレジスタ

これは、5つの1ビットフリップフロップを備えた8ビットレジスタであり、アキュムレータに格納された結果に応じて0または1のいずれかを保持します。

これらは5つのフリップフロップのセットです-

- サイン(S)

- ゼロ(Z)

- 補助キャリー(AC)

- パリティ(P)

- キャリー(C)

そのビット位置を次の表に示します-

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| S | Z | 交流 | P | CY |

命令レジスタとデコーダ

8ビットレジスタです。命令がメモリからフェッチされると、命令レジスタに格納されます。命令デコーダは、命令レジスタに存在する情報をデコードします。

タイミングおよび制御ユニット

マイクロプロセッサにタイミングと制御信号を提供して、操作を実行します。以下は、外部回路と内部回路を制御するタイミング信号と制御信号です。

- 制御信号:READY、RD '、WR'、ALE

- ステータス信号:S0、S1、IO / M '

- DMA信号:HOLD、HLDA

- RESET信号:RESET IN、RESET OUT

割り込み制御

名前が示すように、プロセス中の割り込みを制御します。マイクロプロセッサがメインプログラムを実行しているとき、および割り込みが発生するたびに、マイクロプロセッサは制御をメインプログラムからシフトして、着信要求を処理します。リクエストが完了すると、コントロールはメインプログラムに戻ります。

8085マイクロプロセッサには、INTR、RST 7.5、RST 6.5、RST 5.5、TRAPの5つの割り込み信号があります。

シリアル入出力制御

SID(シリアル入力データ)とSOD(シリアル出力データ)の2つの命令を使用してシリアルデータ通信を制御します。

アドレスバッファとアドレスデータバッファ

スタックポインタとプログラムカウンタに格納されている内容は、アドレスバッファとアドレスデータバッファにロードされ、CPUと通信します。メモリとI / Oチップはこれらのバスに接続されています。CPUは、メモリおよびI / Oチップと必要なデータを交換できます。

アドレスバスとデータバス

データバスは、保存するデータを伝送します。それは双方向ですが、アドレスバスはそれが保存されるべき場所に場所を運び、それは単方向です。データとアドレスI / Oデバイスを転送するために使用されます。

8085アーキテクチャ

この次の画像で8085のアーキテクチャを表現しようとしました-

次の画像は、8085マイクロプロセッサのピン配列を示しています。

8085マイクロプロセッサのピンは7つのグループに分類できます-

アドレスバス

A15-A8、それはメモリ/ IOアドレスの最上位8ビットを運びます。

データバス

AD7-AD0、最下位の8ビットアドレスとデータバスを伝送します。

制御およびステータス信号

これらの信号は、動作の性質を識別するために使用されます。3つの制御信号と3つのステータス信号があります。

3つの制御信号はRD、WR、およびALEです。

RD −この信号は、選択されたIOまたはメモリデバイスが読み取られ、データバスで利用可能なデータを受け入れる準備ができていることを示します。

WR −この信号は、データバス上のデータが選択されたメモリまたはIOロケーションに書き込まれることを示します。

ALE−マイクロプロセッサによって新しい操作が開始されたときに生成される正方向のパルスです。パルスがハイになると、アドレスを示します。パルスが下がると、データを示します。

3つのステータス信号はIO / M、S0、S1です。

IO / M

この信号は、IO動作とメモリ動作を区別するために使用されます。つまり、ハイの場合はIO動作を示し、ローの場合はメモリ動作を示します。

S1&S0

これらの信号は、現在の動作のタイプを識別するために使用されます。

電源

2つの電源信号があります-VCCとVSS。VCCは+ 5v電源を示し、VSSはグランド信号を示します。

クロック信号

X1、X2、CLKOUTの3つのクロック信号があります。

X1, X2−水晶(RC、LC N / W)は、これら2つのピンに接続され、内部クロックジェネレータの周波数を設定するために使用されます。この周波数は内部で2で除算されます。

CLK OUT −この信号は、マイクロプロセッサに接続されたデバイスのシステムクロックとして使用されます。

割り込みと外部から開始された信号

割り込みは、マイクロプロセッサにタスクの実行を要求するために外部デバイスによって生成される信号です。5つの割り込み信号、つまりTRAP、RST 7.5、RST 6.5、RST 5.5、およびINTRがあります。割り込みについては、割り込みのセクションで詳しく説明します。

INTA −割り込み確認信号です。

RESET IN −この信号は、プログラムカウンタをゼロに設定してマイクロプロセッサをリセットするために使用されます。

RESET OUT −この信号は、マイクロプロセッサがリセットされたときに、接続されているすべてのデバイスをリセットするために使用されます。

READY−この信号は、デバイスがデータを送信または受信する準備ができていることを示します。READYがローの場合、CPUはREADYがハイになるのを待つ必要があります。

HOLD −この信号は、別のマスターがアドレスバスとデータバスの使用を要求していることを示します。

HLDA (HOLD Acknowledge)− CPUがHOLD要求を受信し、次のクロックサイクルでバスを放棄することを示します。HOLD信号が除去された後、HLDAはローに設定されます。

シリアルI / O信号

SIDとSODの2つのシリアル信号があり、これらの信号はシリアル通信に使用されます。

SOD (シリアル出力データライン)−出力SODはSIM命令で指定されたようにセット/リセットされます。

SID (シリアル入力データライン)-RIM命令が実行されるたびに、このラインのデータがアキュムレータにロードされます。

次に、8085マイクロプロセッサのアドレッシングモードについて説明します。

8085のアドレッシングモード

これらは、内容を変更せずに、あるレジスタから別のレジスタへ、メモリからレジスタへ、およびレジスタからメモリへデータを転送するために使用される命令です。8085のアドレッシングモードは5つのグループに分類されます-

即時アドレッシングモード

このモードでは、8/16ビットデータがそのオペランドの1つとして命令自体に指定されます。 For example: MVI K、20F:20FがレジスタKにコピーされることを意味します。

レジスタアドレッシングモード

このモードでは、データは1つのレジスタから別のレジスタにコピーされます。 For example: MOV K、B:レジスタBのデータがレジスタKにコピーされることを意味します。

ダイレクトアドレッシングモード

このモードでは、データは指定されたアドレスからレジスタに直接コピーされます。 For example: LDB 5000K:アドレス5000KのデータがレジスタBにコピーされることを意味します。

間接アドレッシングモード

このモードでは、データは、レジスタが指すアドレスを使用して、あるレジスタから別のレジスタに転送されます。 For example: MOV K、B:レジスタが指すメモリアドレスからレジスタKにデータが転送されることを意味します。

暗黙のアドレッシングモード

このモードはオペランドを必要としません。データはオペコード自体によって指定されます。For example: CMP。

8085での割り込み

割り込みは、マイクロプロセッサにタスクの実行を要求するために外部デバイスによって生成される信号です。5つの割り込み信号、つまりTRAP、RST 7.5、RST 6.5、RST 5.5、およびINTRがあります。

割り込みは、パラメータに基づいて次のグループに分類されます-

Vector interrupt −このタイプの割り込みでは、割り込みアドレスはプロセッサに認識されています。 For example: RST7.5、RST6.5、RST5.5、TRAP。

Non-Vector interrupt −このタイプの割り込みでは、割り込みアドレスはプロセッサに認識されないため、割り込みを実行するには、デバイスが割り込みアドレスを外部に送信する必要があります。 For example: INTR。

Maskable interrupt −このタイプの割り込みでは、プログラムにいくつかの命令を書き込むことにより、割り込みを無効にすることができます。 For example: RST7.5、RST6.5、RST5.5。

Non-Maskable interrupt −このタイプの割り込みでは、プログラムにいくつかの命令を書き込んで割り込みを無効にすることはできません。 For example: トラップ。

Software interrupt−このタイプの割り込みでは、プログラマは割り込みを実行するためにプログラムに命令を追加する必要があります。8085には、RST0、RST1、RST2、RST3、RST4、RST5、RST6、およびRST7の8つのソフトウェア割り込みがあります。

Hardware interrupt −ハードウェア割り込みとして使用される8085には5つの割り込みピン、つまりTRAP、RST7.5、RST6.5、RST5.5、INTAがあります。

Note− NTAは割り込みではなく、マイクロプロセッサが確認応答を送信するために使用します。TRAPが最も優先度が高く、次にRST7.5などです。

割り込みサービスルーチン(ISR)

実行時に対応する割り込みソースにサービスを提供する小さなプログラムまたはルーチンは、ISRと呼ばれます。

トラップ

これはマスク不可割り込みであり、すべての割り込みの中で最も優先度が高くなります。デフォルトでは、確認されるまで有効になっています。障害が発生した場合、ISRとして実行され、データがバックアップメモリに送信されます。この割り込みは、制御をロケーション0024Hに移します。

RST7.5

これはマスク可能な割り込みであり、すべての割り込みの中で2番目に優先度が高くなります。この割り込みが実行されると、プロセッサはPCレジスタの内容をスタックに保存し、003CHアドレスに分岐します。

RST 6.5

これはマスク可能な割り込みであり、すべての割り込みの中で3番目に優先度が高くなります。この割り込みが実行されると、プロセッサはPCレジスタの内容をスタックに保存し、0034Hアドレスに分岐します。

RST 5.5

マスク可能な割り込みです。この割り込みが実行されると、プロセッサはPCレジスタの内容をスタックに保存し、002CHアドレスに分岐します。

INTR

これはマスク可能な割り込みであり、すべての割り込みの中で最も優先度が低くなっています。マイクロプロセッサをリセットすることで無効にできます。

いつ INTR signal goes high、次のイベントが発生する可能性があります-

マイクロプロセッサは、各命令の実行中にINTR信号のステータスをチェックします。

INTR信号がハイの場合、マイクロプロセッサは現在の命令を完了し、アクティブロー割り込みアクノリッジ信号を送信します。

命令を受信すると、マイクロプロセッサは次の命令のアドレスをスタックに保存し、受信した命令を実行します。

8085マイクロプロセッサのプログラミングを見てみましょう。

命令セットは、いくつかのタスクを実行するための命令コードです。それは5つのカテゴリーに分類されます。

| S.No. | 指示と説明 |

|---|---|

| 1 | 制御手順 以下は、制御命令のリストとその意味を示す表です。 |

| 2 | 論理命令 以下は、論理命令とその意味のリストを示す表です。 |

| 3 | 分岐手順 以下は、分岐命令とその意味のリストを示す表です。 |

| 4 | 算術命令 以下は、算術命令とその意味のリストを示す表です。 |

| 5 | データ転送手順 以下は、データ転送命令とその意味のリストを示す表です。 |

8085 –デモプログラム

それでは、上記の手順を使用して、いくつかのプログラムのデモンストレーションを見てみましょう-

2つの8ビット数の加算

3005Hおよび3006Hのメモリ位置にデータを追加し、その結果を3007Hのメモリ位置に格納するプログラムを作成します。

Problem demo −

(3005H) = 14H

(3006H) = 89HResult −

14H + 89H = 9DH

プログラムコードは次のように書くことができます-

LXI H 3005H : "HL points 3005H"

MOV A, M : "Getting first operand"

INX H : "HL points 3006H"

ADD M : "Add second operand"

INX H : "HL points 3007H"

MOV M, A : "Store result at 3007H"

HLT : "Exit program"メモリ位置の交換

5000Mと6000Mのメモリ位置でデータを交換するプログラムを作成します。

LDA 5000M : "Getting the contents at5000M location into accumulator"

MOV B, A : "Save the contents into B register"

LDA 6000M : "Getting the contents at 6000M location into accumulator"

STA 5000M : "Store the contents of accumulator at address 5000M"

MOV A, B : "Get the saved contents back into A register"

STA 6000M : "Store the contents of accumulator at address 6000M"番号を昇順で並べる

メモリアドレス3000Hの最初の10個の数字を昇順で並べるプログラムを作成します。

MVI B, 09 :"Initialize counter"

START :"LXI H, 3000H: Initialize memory pointer"

MVI C, 09H :"Initialize counter 2"

BACK: MOV A, M :"Get the number"

INX H :"Increment memory pointer"

CMP M :"Compare number with next number"

JC SKIP :"If less, don’t interchange"

JZ SKIP :"If equal, don’t interchange"

MOV D, M

MOV M, A

DCX H

MOV M, D

INX H :"Interchange two numbers"

SKIP:DCR C :"Decrement counter 2"

JNZ BACK :"If not zero, repeat"

DCR B :"Decrement counter 1"

JNZ START

HLT :"Terminate program execution"8086マイクロプロセッサは、1976年にIntelによって設計された8085マイクロプロセッサの拡張バージョンです。これは、最大1MBのストレージを提供する20のアドレスラインと16のデータラインを備えた16ビットマイクロプロセッサです。強力な命令セットで構成されており、乗算や除算などの演算を簡単に実行できます。

最大モードと最小モードの2つの動作モードをサポートします。最大モードは複数のプロセッサを搭載したシステムに適しており、最小モードは単一のプロセッサを搭載したシステムに適しています。

8086の機能

8086マイクロプロセッサの最も顕著な機能は次のとおりです-

命令キューがあり、メモリから6命令バイトを格納できるため、処理が高速になります。

これは、16ビットALU、16ビットレジスタ、内部データバス、および16ビット外部データバスを備えた最初の16ビットプロセッサであり、処理が高速化されました。

動作頻度に応じて3つのバージョンがあります-

8086→5MHz

8086-2→8MHz

(c)8086-1→10 MHz

パイプラインの2つのステージ、つまりフェッチステージと実行ステージを使用してパフォーマンスを向上させます。

フェッチステージでは、最大6バイトの命令をプリフェッチして、キューに格納できます。

実行ステージはこれらの命令を実行します。

256個のベクタ割り込みがあります。

29,000個のトランジスタで構成されています。

8085と8086マイクロプロセッサの比較

Size − 8085は8ビットマイクロプロセッサですが、8086は16ビットマイクロプロセッサです。

Address Bus − 8085には16ビットのアドレスバスがあり、8086には20ビットのアドレスバスがあります。

Memory − 8085は最大64Kbにアクセスできますが、8086は最大1Mbのメモリにアクセスできます。

Instruction − 8085には命令キューがありませんが、8086には命令キューがあります。

Pipelining − 8085はパイプラインアーキテクチャをサポートしていませんが、8086はパイプラインアーキテクチャをサポートしています。

I/O −8085は2 ^ 8 = 256 I / Oに対応できますが、8086は2 ^ 16 = 65,536 I / Oにアクセスできます。

Cost − 8085のコストは低いのに対し、8086のコストは高い。

8086のアーキテクチャ

次の図は、8086マイクロプロセッサのアーキテクチャを示しています。

8086マイクロプロセッサは2つの機能ユニットに分かれています。 EU (実行ユニット)および BIU (バスインターフェースユニット)。

EU(実行ユニット)

実行ユニットは、データをどこからフェッチし、それらの命令をデコードして実行するかを示す命令をBIUに提供します。その機能は、命令デコーダとALUを使用してデータの操作を制御することです。EUは、上の図に示すようにシステムバスと直接接続しておらず、BIUを介してデータに対して操作を実行します。

ここで、8086マイクロプロセッサの機能部分について説明します。

ALU

+、−、×、/、OR、AND、NOT演算など、すべての算術演算と論理演算を処理します。

フラグレジスタ

これは、フリップフロップのように動作する16ビットレジスタです。つまり、アキュムレータに格納された結果に応じてステータスを変更します。9つのフラグがあり、条件付きフラグと制御フラグの2つのグループに分けられます。

条件付きフラグ

これは、最後に実行された算術命令または論理命令の結果を表します。以下は条件付きフラグのリストです-

Carry flag −このフラグは、算術演算のオーバーフロー条件を示します。

Auxiliary flag− ALUで演算を実行すると、下ニブル(つまり、D0 – D3)から上ニブル(つまり、D4 – D7)へのキャリー/バローが発生し、このフラグが設定されます。つまり、D3ビットからD4へのキャリーは次のようになります。 AFフラグ。プロセッサはこのフラグを使用して、バイナリからBCDへの変換を実行します。

Parity flag−このフラグは、結果のパリティを示すために使用されます。つまり、結果の下位8ビットに偶数の1が含まれている場合、パリティフラグが設定されます。奇数の1の場合、パリティフラグがリセットされます。

Zero flag −このフラグは、算術演算または論理演算の結果がゼロの場合は1に設定され、それ以外の場合は0に設定されます。

Sign flag −このフラグは結果の符号を保持します。つまり、演算の結果が負の場合、符号フラグは1に設定され、それ以外の場合は0に設定されます。

Overflow flag −このフラグは、システム容量を超えた場合の結果を表します。

制御フラグ

制御フラグは、実行ユニットの操作を制御します。以下は制御フラグのリストです-

Trap flag−シングルステップ制御に使用され、ユーザーはデバッグのために一度に1つの命令を実行できます。設定されている場合、プログラムはシングルステップモードで実行できます。

Interrupt flag−これは、割り込みの有効化/無効化フラグです。つまり、プログラムの中断を許可/禁止するために使用されます。割り込み有効状態の場合は1に設定され、割り込み無効状態の場合は0に設定されます。

Direction flag−文字列操作で使用されます。名前が示すように、設定されると、文字列バイトは上位のメモリアドレスから下位のメモリアドレスにアクセスされ、その逆も同様です。

汎用レジスタ

AH、AL、BH、BL、CH、CL、DH、DLの8つの汎用レジスタがあります。これらのレジスタは、8ビットデータを格納するために個別に使用でき、16ビットデータを格納するためにペアで使用できます。有効なレジスタペアは、AHとAL、BHとBL、CHとCL、およびDHとDLです。それぞれAX、BX、CX、DXと呼ばれます。

AX register−アキュムレータレジスタとも呼ばれます。算術演算のオペランドを格納するために使用されます。

BX register−ベースレジスタとして使用されます。これは、データセグメント内のメモリ領域の開始ベースアドレスを格納するために使用されます。

CX register−カウンターと呼ばれます。ループ命令でループカウンタを格納するために使用されます。

DX register −このレジスタは、I / O命令のI / Oポートアドレスを保持するために使用されます。

スタックポインタレジスタ

これは16ビットレジスタであり、セグメントの先頭から、ワードがスタックに最後に格納されたメモリ位置までのアドレスを保持します。

BIU(バスインターフェースユニット)

BIUは、アドレスの送信、メモリからの命令のフェッチ、ポートとメモリからのデータの読み取り、ポートとメモリへのデータの書き込みなど、EU向けのバスでのすべてのデータとアドレスの転送を処理します。EUにはシステムバスとの方向接続がないため、これはBIUで可能です。EUとBIUは内部バスに接続されています。

以下の機能部分があります-

Instruction queue−BIUには命令キューが含まれています。BIUは、最大6バイトの次の命令を取得し、それらを命令キューに格納します。EUが命令を実行し、次の命令の準備ができると、EUはこの命令キューから命令を読み取るだけで、実行速度が向上します。

現在の命令の実行中に次の命令をフェッチするが呼び出されます pipelining。

Segment register− BIUには、CS、DS、SS、ESの4つのセグメントバスがあります。プロセッサがメモリ位置にアクセスするために使用する命令とデータのアドレスをメモリに保持します。また、EUによって実行される次の命令のアドレスを保持する1つのポインタレジスタIPも含まれています。

CS−コードセグメントの略です。これは、実行可能プログラムが格納されているメモリのコードセグメント内のメモリ位置をアドレス指定するために使用されます。

DS−データセグメントの略です。これは、プログラムによって使用されるデータで構成され、オフセットアドレスまたはオフセットアドレスを保持する他のレジスタのコンテンツによってデータセグメントでアクセスされます。

SS−スタックセグメントの略です。実行中にデータとアドレスを格納するためのメモリを処理します。

ES−これはExtraSegmentの略です。ESは追加のデータセグメントであり、追加の宛先データを保持するために文字列によって使用されます。

Instruction pointer −次に実行する命令のアドレスを保持するために使用する16ビットのレジスタです。

8086は、40ピンDIP(デュアルインラインパッケージ)チップで利用可能な最初の16ビットマイクロプロセッサでした。ここで、8086マイクロプロセッサのピン構成について詳しく説明します。

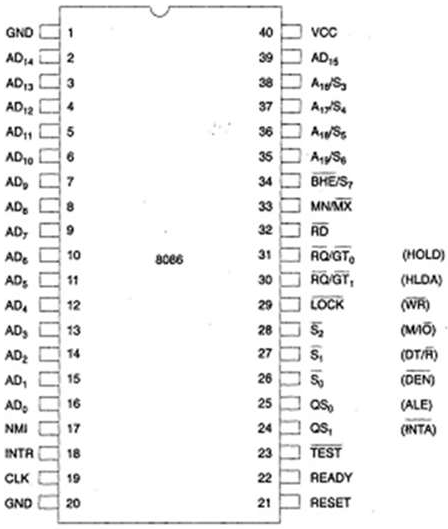

8086ピンダイアグラム

これが8086マイクロプロセッサのピン配列です-

信号について詳しく説明しましょう-

Power supply and frequency signals

VCCピン40で5VDC電源を使用し、VSSピン1および20でグランドを使用して動作します。

Clock signal

クロック信号はピン19を介して提供されます。プロセッサに操作のタイミングを提供します。その周波数はバージョンごとに異なります。つまり、5MHz、8MHz、10MHzです。

Address/data bus

AD0-AD15。これらは16アドレス/データバスです。AD0-AD7は下位バイトデータを伝送し、AD8AD15は上位バイトデータを伝送します。最初のクロックサイクルでは、16ビットアドレスを伝送し、その後、16ビットデータを伝送します。

Address/status bus

A16-A19 / S3-S6。これらは4つのアドレス/ステータスバスです。最初のクロックサイクルでは、4ビットアドレスを伝送し、その後、ステータス信号を伝送します。

S7/BHE

BHEはBusHighEnableの略です。これはピン34で使用でき、データバスD8〜D15を使用したデータの転送を示すために使用されます。この信号は、最初のクロックサイクル中はローで、その後はアクティブになります。

Read($\overline{RD}$)

これはピン32で使用可能であり、読み取り操作の信号を読み取るために使用されます。

Ready

ピン22で使用できます。データが転送されるのはI / Oデバイスからの確認応答信号です。これはアクティブハイ信号です。ハイの場合、デバイスがデータを転送する準備ができていることを示します。ローの場合は待機状態を示します。

RESET

ピン21で使用可能であり、実行を再開するために使用されます。これにより、プロセッサは現在のアクティビティをただちに終了します。この信号は、マイクロプロセッサをリセットするために最初の4クロックサイクルの間アクティブハイになります。

INTR

これはピン18で使用できます。これは割り込み要求信号であり、各命令の最後のクロックサイクル中にサンプリングされ、プロセッサがこれを割り込みと見なしたかどうかを判断します。

NMI

これはマスク不可割り込みの略で、ピン17で使用できます。これはエッジトリガー入力であり、マイクロプロセッサに割り込み要求を発生させます。

$\overline{TEST}$

この信号は待機状態に似ており、ピン23で使用できます。この信号がHighの場合、プロセッサはIDLE状態を待機する必要があります。それ以外の場合、実行は続行されます。

MN/$\overline{MX}$

これはMinimum / Maximumの略で、ピン33で使用できます。プロセッサがどのモードで動作するかを示します。高い場合は、最小モードで動作し、その逆も同様です。

INTA

これは、ピン24で使用可能な割り込み確認信号とIDです。マイクロプロセッサがこの信号を受信すると、割り込みを確認します。

ALE

これはアドレスイネーブルラッチの略で、ピン25で使用できます。プロセッサが動作を開始するたびに正のパルスが生成されます。この信号は、アドレス/データラインで有効なアドレスが利用可能であることを示します。

DEN

これはデータイネーブルの略で、ピン26で使用できます。トランシーバー8286を有効にするために使用されます。トランシーバーは、アドレス/データバスからデータを分離するために使用されるデバイスです。

DT/R

これはデータ送信/受信信号の略で、ピン27で使用できます。トランシーバーを通過するデータフローの方向を決定します。高い場合、データは送信され、その逆も同様です。

M/IO

この信号は、メモリ操作とI / O操作を区別するために使用されます。ハイの場合はI / O動作を示し、ローの場合はメモリ動作を示します。ピン28で入手できます。

WR

これは書き込み信号の略で、ピン29で使用できます。M/ IO信号のステータスに応じて、メモリまたは出力デバイスにデータを書き込むために使用されます。

HLDA

これはHoldAcknowledgement信号の略で、ピン30で使用できます。この信号はHOLD信号を確認します。

HOLD

この信号は、外部デバイスがアドレス/データバスへのアクセスを要求していることをプロセッサに示します。ピン31で利用できます。

QS1 and QS0

これらはキューステータス信号であり、ピン24および25で使用できます。これらの信号は、命令キューのステータスを提供します。それらの状態を次の表に示します-

| QS 0 | QS 1 | 状態 |

|---|---|---|

| 0 | 0 | 操作なし |

| 0 | 1 | キューからのオペコードの最初のバイト |

| 1 | 0 | キューを空にします |

| 1 | 1 | キューからの後続バイト |

S0, S1, S2

これらは、動作のステータスを提供するステータス信号であり、バスコントローラ8288がメモリおよびI / O制御信号を生成するために使用します。これらはピン26、27、および28で使用できます。以下はそれらのステータスを示す表です-

| S 2 | S 1 | S 0 | 状態 |

|---|---|---|---|

| 0 | 0 | 0 | 割り込み確認 |

| 0 | 0 | 1 | I / O読み取り |

| 0 | 1 | 0 | I / O書き込み |

| 0 | 1 | 1 | 停止 |

| 1 | 0 | 0 | オペコードフェッチ |

| 1 | 0 | 1 | 読み取ったメモリ |

| 1 | 1 | 0 | メモリ書き込み |

| 1 | 1 | 1 | 受動的 |

LOCK

この信号がアクティブな場合、CPUにシステムバスを離れるように要求しないように他のプロセッサに示します。これは、任意の命令でLOCKプレフィックスを使用してアクティブ化され、ピン29で使用できます。

RQ/GT1 and RQ/GT0

これらは、CPUにシステムバスの解放を要求する他のプロセッサによって使用される要求/許可信号です。信号がCPUによって受信されると、確認応答が送信されます。RQ / GT 0 RQ / GTより高い優先順位有する1。

8086マイクロプロセッサは8種類の命令をサポートします-

- データ転送手順

- 算術命令

- ビット操作手順

- 文字列命令

- プログラム実行転送命令(分岐およびループ命令)

- プロセッサ制御手順

- 反復制御命令

- 割り込み命令

ここで、これらの命令セットについて詳しく説明します。

データ転送手順

これらの命令は、ソースオペランドからデスティネーションオペランドにデータを転送するために使用されます。以下は、このグループの下の指示のリストです-

単語を転送するための指示

MOV −指定されたソースから指定された宛先にバイトまたはワードをコピーするために使用されます。

PPUSH −スタックの一番上に単語を置くために使用されます。

POP −スタックの最上位から指定された場所に単語を取得するために使用されます。

PUSHA −すべてのレジスタをスタックに入れるために使用されます。

POPA −スタックからすべてのレジスタにワードを取得するために使用されます。

XCHG −2つの場所からのデータを交換するために使用されます。

XLAT −メモリ内のテーブルを使用してALのバイトを変換するために使用されます。

入力および出力ポート転送の手順

IN −指定されたポートからアキュムレータにバイトまたはワードを読み取るために使用されます。

OUT −アキュムレータから指定されたポートにバイトまたはワードを送信するために使用されます。

アドレスを転送する手順

LEA −指定されたレジスタにオペランドのアドレスをロードするために使用されます。

LDS −メモリからDSレジスタおよびその他の提供されたレジスタをロードするために使用されます

LES −メモリからESレジスタおよびその他の提供されたレジスタをロードするために使用されます。

フラグレジスタを転送する手順

LAHF −フラグレジスタの下位バイトをAHにロードするために使用されます。

SAHF −AHレジスタをフラグレジスタの下位バイトに格納するために使用されます。

PUSHF −スタックの最上位にあるフラグレジスタをコピーするために使用されます。

POPF −スタックの最上位にあるワードをフラグレジスタにコピーするために使用されます。

算術命令

これらの命令は、加算、減算、乗算、除算などの算術演算を実行するために使用されます。

以下は、このグループの下の指示のリストです-

加算の実行手順

ADD −指定されたバイトをバイトに/ワードをワードに追加するために使用されます。

ADC −キャリーで追加するために使用されます。

INC −指定されたバイト/ワードを1インクリメントするために使用されます。

AAA −加算後にASCIIを調整するために使用されます。

DAA −加算/減算操作後の小数を調整するために使用されます。

減算を実行するための指示

SUB −ワードからバイト/ワードからバイトを減算するために使用されます。

SBB −借用による減算を実行するために使用されます。

DEC −指定されたバイト/ワードを1デクリメントするために使用されます。

NPG −指定されたバイト/ワードの各ビットを否定し、1/2の補数を追加するために使用されます。

CMP −提供された2バイト/ワードを比較するために使用されます。

AAS −減算後にASCIIコードを調整するために使用されます。

DAS −減算後に小数を調整するために使用されます。

乗算を実行するための指示

MUL −符号なしバイトをバイトごとに/ワードごとに乗算するために使用されます。

IMUL −符号付きバイトをバイトごとに/ワードごとに乗算するために使用されます。

AAM −乗算後にASCIIコードを調整するために使用されます。

除算の実行手順

DIV −符号なしワードをバイトで除算するか、符号なしダブルワードをワードで除算するために使用されます。

IDIV −符号付きワードをバイトごとに、または符号付きダブルワードをワードごとに分割するために使用されます。

AAD −除算後にASCIIコードを調整するために使用されます。

CBW −ワードの上位バイトを下位バイトの符号ビットのコピーで埋めるために使用されます。

CWD −ダブルワードの上位ワードを下位ワードの符号ビットで埋めるために使用されます。

ビット操作手順

これらの命令は、データビットが関係する操作、つまり論理、シフトなどの操作を実行するために使用されます。

以下は、このグループの下の指示のリストです-

論理演算を実行するための指示

NOT −バイトまたはワードの各ビットを反転するために使用されます。

AND −バイト/ワードの各ビットを別のバイト/ワードの対応するビットに追加するために使用されます。

OR −バイト/ワードの各ビットを別のバイト/ワードの対応するビットで乗算するために使用されます。

XOR −バイト/ワードの各ビットと別のバイト/ワードの対応するビットに対して排他的論理和演算を実行するために使用されます。

TEST −オペランドに影響を与えることなく、フラグを更新するためのオペランドを追加するために使用されます。

シフト操作を実行するための指示

SHL/SAL −バイト/ワードのビットを左にシフトし、LSBにゼロ(S)を入れるために使用されます。

SHR −バイト/ワードのビットを右にシフトし、MSBにゼロ(S)を入れるために使用されます。

SAR −バイト/ワードのビットを右にシフトし、古いMSBを新しいMSBにコピーするために使用されます。

回転操作を実行するための指示

ROL −バイト/ワードのビットを左にローテーションするために使用されます。つまり、MSBをLSBに、キャリーフラグ[CF]にローテーションします。

ROR − Used to rotate bits of byte/word towards the right, i.e. LSB to MSB and to Carry Flag [CF].

RCR − Used to rotate bits of byte/word towards the right, i.e. LSB to CF and CF to MSB.

RCL − Used to rotate bits of byte/word towards the left, i.e. MSB to CF and CF to LSB.

String Instructions

String is a group of bytes/words and their memory is always allocated in a sequential order.

Following is the list of instructions under this group −

REP − Used to repeat the given instruction till CX ≠ 0.

REPE/REPZ − Used to repeat the given instruction until CX = 0 or zero flag ZF = 1.

REPNE/REPNZ − Used to repeat the given instruction until CX = 0 or zero flag ZF = 1.

MOVS/MOVSB/MOVSW − Used to move the byte/word from one string to another.

COMS/COMPSB/COMPSW − Used to compare two string bytes/words.

INS/INSB/INSW − Used as an input string/byte/word from the I/O port to the provided memory location.

OUTS/OUTSB/OUTSW − Used as an output string/byte/word from the provided memory location to the I/O port.

SCAS/SCASB/SCASW − Used to scan a string and compare its byte with a byte in AL or string word with a word in AX.

LODS/LODSB/LODSW − Used to store the string byte into AL or string word into AX.

プログラム実行転送命令(分岐およびループ命令)

これらの命令は、実行中に命令を転送/分岐するために使用されます。次の手順が含まれています-

実行中に無条件で命令を転送する命令-

CALL −プロシージャを呼び出し、そのリターンアドレスをスタックに保存するために使用されます。

RET −プロシージャからメインプログラムに戻るために使用されます。

JMP −指定されたアドレスにジャンプして次の命令に進むために使用されます。

いくつかの条件で実行中に命令を転送するための命令-

JA/JNBE −上/下ではない/等しい命令が満たす場合にジャンプするために使用されます。

JAE/JNB −命令の上/下ではない場合にジャンプするために使用されます。

JBE/JNA −以下/等しい/上記ではない命令が満たす場合にジャンプするために使用されます。

JC −キャリーフラグCF = 1の場合にジャンプするために使用されます

JE/JZ −等しい/ゼロフラグZF = 1の場合にジャンプするために使用されます

JG/JNLE −より大きい/より小さい/等しい命令が満たす場合にジャンプするために使用されます。

JGE/JNL −命令以上/等しい/以上の場合にジャンプするために使用されます。

JL/JNGE −以下/以下/等しい命令が満たす場合にジャンプするために使用されます。

JLE/JNG −命令が満たす場合、以下/等しい/以下の場合にジャンプするために使用されます。

JNC −キャリーフラグがない場合にジャンプするために使用されます(CF = 0)

JNE/JNZ −等しくない場合にジャンプするために使用/ゼロフラグZF = 0

JNO −オーバーフローフラグOF = 0がない場合にジャンプするために使用されます

JNP/JPO −パリティ/パリティ奇数でない場合にジャンプするために使用PF = 0

JNS − SF = 0に署名しない場合にジャンプするために使用されます

JO −オーバーフローフラグOF = 1の場合にジャンプするために使用されます

JP/JPE − PF = 1でもパリティ/パリティの場合にジャンプするために使用されます

JS −符号フラグSF = 1の場合にジャンプするために使用されます

プロセッサ制御手順

これらの命令は、フラグ値を設定/リセットすることによってプロセッサの動作を制御するために使用されます。

以下は、このグループの下での指示です-

STC −キャリーフラグCFを1に設定するために使用されます

CLC −キャリーフラグCFをクリア/リセットするために使用されます0

CMC −キャリーフラグCFの状態で補数を配置するために使用されます。

STD −方向フラグDFを1に設定するために使用されます

CLD −方向フラグDFを0にクリア/リセットするために使用されます

STI −割り込みイネーブルフラグを1に設定するために使用されます。つまり、INTR入力をイネーブルにします。

CLI −割り込みイネーブルフラグを0にクリアするために使用されます。つまり、INTR入力を無効にします。

反復制御命令

これらの命令は、指定された命令を何度も実行するために使用されます。以下は、このグループの下の指示のリストです-

LOOP −条件が満たされるまで、つまりCX = 0になるまで、命令のグループをループするために使用されます

LOOPE/LOOPZ − ZF = 1およびCX = 0を満たすまで、命令のグループをループするために使用されます

LOOPNE/LOOPNZ − ZF = 0およびCX = 0を満たすまで、命令のグループをループするために使用されます

JCXZ − CX = 0の場合、指定されたアドレスにジャンプするために使用されます

割り込み命令

これらの命令は、プログラムの実行中に割り込みを呼び出すために使用されます。

INT −指定されたサービスの実行および呼び出し中にプログラムを中断するために使用されます。

INTO − OF = 1の場合、実行中にプログラムを中断するために使用されます

IRET −割り込みサービスからメインプログラムに戻るために使用されます

Interruptプログラムの実行中に一時停止を作成する方法であり、周辺機器がマイクロプロセッサにアクセスできるようにします。マイクロプロセッサはその割り込みに応答しますISR (割り込みサービスルーチン)。これは、割り込みの処理方法をマイクロプロセッサに指示するための短いプログラムです。

次の画像は、8086マイクロプロセッサで発生する割り込みの種類を示しています。

ハードウェア割り込み

ハードウェア割り込みは、指定されたピンを介してマイクロプロセッサに信号を送信することにより、周辺機器によって引き起こされます。

8086には、NMIとINTRの2つのハードウェア割り込みピンがあります。NMIはマスク不可割り込みであり、INTRは優先度の低いマスク不可割り込みです。関連するもう1つの割り込みピンは、割り込みアクノリッジと呼ばれるINTAです。

NMI

これは、マスカブル割り込み要求ピン(INTR)よりも優先度の高い単一のマスク不可割り込みピン(NMI)であり、タイプ2の割り込みです。

この割り込みがアクティブになると、これらのアクションが実行されます-

進行中の現在の命令を完了します。

フラグレジスタ値をスタックにプッシュします。

リターンアドレスのCS(コードセグメント)値とIP(命令ポインタ)値をスタックにプッシュします。

IPは、ワードロケーション00008Hのコンテンツからロードされます。

CSは、次のワード位置0000AHの内容からロードされます。

割り込みフラグとトラップフラグは0にリセットされます。

INTR

INTRは、割り込みフラグの設定命令を使用して割り込みが有効になっている場合にのみマイクロプロセッサが割り込みられるため、マスク可能な割り込みです。割り込みフラグのクリア命令を使用して有効にしないでください。

INTR割り込みは、I / Oポートによってアクティブになります。割り込みが有効でNMIが無効の場合、マイクロプロセッサは最初に現在の実行を完了し、INTAピンに「0」を2回送信します。最初の「0」は、INTAが外部デバイスに準備をするように通知し、2番目の「0」の間にマイクロプロセッサがプログラム可能な割り込みコントローラから8ビット(たとえばX)を受信することを意味します。

これらのアクションはマイクロプロセッサによって実行されます-

まず、現在の命令を完了します。

INTA出力をアクティブにし、割り込みタイプ(Xなど)を受け取ります。

フラグレジスタ値、リターンアドレスのCS値、リターンアドレスのIP値がスタックにプッシュされます。

IP値はワード位置X×4の内容からロードされます

CSは、次の単語の場所の内容からロードされます。

割り込みフラグとトラップフラグが0にリセットされます

ソフトウェア割り込み

一部の命令は、割り込みを作成するためにプログラムの目的の位置に挿入されます。これらの割り込み命令は、さまざまな割り込みハンドラの動作をテストするために使用できます。含まれています-

INT-タイプ番号の割り込み命令

2バイト命令です。最初のバイトはオペコードを提供し、2番目のバイトは割り込みタイプ番号を提供します。このグループには256種類の割り込みがあります。

その実行には、次の手順が含まれます-

フラグレジスタ値はスタックにプッシュされます。

リターンアドレスのCS値とリターンアドレスのIP値がスタックにプッシュされます。

IPは単語の場所「タイプ番号」×4の内容からロードされます

CSは、次の単語の場所の内容からロードされます。

割り込みフラグとトラップフラグが0にリセットされます

type0割り込みの開始アドレスは000000H、type1割り込みの場合は00004H、type2の場合も同様に00008Hなどです。最初の5つのポインターは、専用の割り込みポインターです。すなわち−

TYPE 0 割り込みは、ゼロ除算の状況を表します。

TYPE 1 割り込みは、プログラムのデバッグ中のシングルステップ実行を表します。

TYPE 2 割り込みは、マスク不可能なNMI割り込みを表します。

TYPE 3 割り込みはブレークポイント割り込みを表します。

TYPE 4 割り込みはオーバーフロー割り込みを表します。

タイプ5からタイプ31までの割り込みは、他の高度なマイクロプロセッサ用に予約されており、32からタイプ255までの割り込みは、ハードウェアおよびソフトウェアの割り込みに使用できます。

INT3-ブレークポイント割り込み命令

オペコードがCCHの1バイト命令です。これらの命令はプログラムに挿入されるため、プロセッサはそこに到達すると、プログラムの通常の実行を停止し、ブレークポイント手順に従います。

その実行には、次の手順が含まれます-

フラグレジスタ値はスタックにプッシュされます。

リターンアドレスのCS値とリターンアドレスのIP値がスタックにプッシュされます。

IPはワードロケーション3×4 = 0000CHのコンテンツからロードされます

CSは、次の単語の場所の内容からロードされます。

割り込みフラグとトラップフラグが0にリセットされます

INTO-オーバーフロー命令で割り込み

これは1バイトの命令とそのニーモニックです INTO。この命令のオペコードはCEHです。名前が示すように、これは条件付き割り込み命令です。つまり、オーバーフローフラグが1に設定されている場合にのみアクティブになり、割り込みタイプ番号が4の割り込みハンドラに分岐します。オーバーフローフラグがリセットされると、実行は次の指示。

その実行には、次の手順が含まれます-

フラグレジスタ値はスタックにプッシュされます。

リターンアドレスのCS値とリターンアドレスのIP値がスタックにプッシュされます。

IPはワードロケーション4×4 = 00010Hのコンテンツからロードされます

CSは、次の単語の場所の内容からロードされます。

割り込みフラグとトラップフラグが0にリセットされます

ソースオペランドが命令で示されるさまざまな方法は、次のように知られています。 addressing modes。8086プログラミングには8つの異なるアドレッシングモードがあります-

即時アドレッシングモード

データオペランドが命令自体の一部であるアドレッシングモードは、即時アドレッシングモードと呼ばれます。

例

MOV CX, 4929 H, ADD AX, 2387 H, MOV AL, FFHレジスタアドレッシングモード

これは、レジスタが命令のオペランドのソースであることを意味します。

例

MOV CX, AX ; copies the contents of the 16-bit AX register into

; the 16-bit CX register),

ADD BX, AXダイレクトアドレッシングモード

メモリ位置の実効アドレスが命令に直接書き込まれるアドレッシングモード。

例

MOV AX, [1592H], MOV AL, [0300H]間接アドレッシングモードを登録する

このアドレッシングモードでは、BP、BX、DI、SIのいずれかのレジスタに保持されているオフセットアドレスを介して、任意のメモリ位置でデータをアドレス指定できます。

例

MOV AX, [BX] ; Suppose the register BX contains 4895H, then the contents

; 4895H are moved to AX

ADD CX, {BX}ベースアドレッシングモード

このアドレッシングモードでは、オペランドのオフセットアドレスは、BX / BPレジスタの内容と8ビット/ 16ビットの変位の合計によって与えられます。

例

MOV DX, [BX+04], ADD CL, [BX+08]インデックス付きアドレッシングモード

このアドレッシングモードでは、オペランドオフセットアドレスは、SIまたはDIレジスタの内容と8ビット/ 16ビットの変位を加算することによって検出されます。

例

MOV BX, [SI+16], ADD AL, [DI+16]ベースインデックスアドレッシングモード

このアドレッシングモードでは、オペランドのオフセットアドレスは、ベースレジスタをインデックスレジスタの内容に合計することによって計算されます。

例

ADD CX, [AX+SI], MOV AX, [AX+DI]変位モードでインデックス付けされたベース

このアドレッシングモードでは、オペランドオフセットはベースレジスタの内容を加算することによって計算されます。インデックスは、内容と8ビットまたは16ビットの変位を登録します。

例

MOV AX, [BX+DI+08], ADD CX, [BX+SI+16]マルチプロセッサとは、命令を同時に実行するプロセッサの複数のセットを意味します。3つの基本的なマルチプロセッサ構成があります。

- コプロセッサー構成

- 密結合構成

- 疎結合構成

コプロセッサー構成

コプロセッサーは、マイクロプロセッサーチップ上で特別に設計された回路であり、マイクロプロセッサーが実行するのと同じタスクを非常に迅速に実行できます。メインプロセッサの作業負荷を軽減します。コプロセッサは、同じメモリ、IOシステム、バス、制御ロジック、およびクロックジェネレータを共有します。コプロセッサーは、数学計算、画面へのグラフィック表示などの特殊なタスクを処理します。

8086および8088はほとんどの演算を実行できますが、それらの命令セットは複雑な数学演算を実行できないため、これらの場合、マイクロプロセッサには、これらの演算を非常に迅速に簡単に実行できるIntel8087数学コプロセッサのような数学コプロセッサが必要です。

コプロセッサー構成のブロック図

コプロセッサーとプロセッサーはどのように接続されていますか?

コプロセッサ及びプロセッサはTEST、RQ- / GT-及びQSを介して接続されている0&QS 1つの信号。

TEST信号はコプロセッサーのBUSYピンに接続され、残りの3つのピンはコプロセッサーの同じ名前の3つのピンに接続されます。

TEST信号は、コプロセッサーのアクティビティーを処理します。つまり、コプロセッサーはビジーまたはアイドル状態です。

RT- / GT-はバスアービトレーションに使用されます。

コプロセッサは、QS使用0&QS 1をホストプロセッサのキューの状態を追跡します。

密結合構成

密結合構成はコプロセッサー構成に似ています。つまり、両方が同じメモリー、I / Oシステムバス、制御ロジック、および制御ジェネレーターをホストプロセッサーと共有します。ただし、コプロセッサーとホストプロセッサーは、独自の命令をフェッチして実行します。システムバスは、コプロセッサとホストプロセッサによって個別に制御されます。

密結合構成のブロック図

プロセッサと独立したプロセッサはどのように接続されていますか?

ホストと独立したプロセッサ間の通信は、メモリ空間を介して行われます。

WAIT、ESCなどのように、どの命令も通信には使用されません。

ホストプロセッサはメモリを管理し、ポートの1つにコマンドを送信することで独立したプロセッサをウェイクアップします。

次に、独立したプロセッサがメモリにアクセスしてタスクを実行します。

タスクの完了後、ステータス信号または割り込み要求を使用して、ホストプロセッサに確認応答を送信します。

疎結合構成

疎結合構成は、共通のシステムバスを介して接続されたマイクロプロセッサベースのシステムのモジュールの数で構成されます。各モジュールは、独自のクロックジェネレータ、メモリ、I / Oデバイスで構成され、ローカルバスを介して接続されます。

疎結合構成のブロック図

利点

複数のプロセッサを使用すると、効率が向上します。

各プロセッサには、ローカルメモリ/ I / Oデバイスにアクセスするための独自のローカルバスがあります。これにより、並列処理が容易になります。

システム構造は柔軟です。つまり、1つのモジュールの障害がシステム全体の障害に影響を与えることはありません。障害のあるモジュールは後で交換できます。

8087数値データプロセッサは、 Math co-processor, Numeric processor extension そして Floating point unit。これは、Intelが8086/8088とペアリングするように設計した最初の数学コプロセッサーであり、計算がより簡単かつ高速になりました。

命令が8086/8088プロセッサによって識別されると、それはさらに実行するために8087コプロセッサに割り当てられます。

8087でサポートされているデータ型は次のとおりです。

- 2進整数

- パック10進数

- 実数

- 一時的な実際の形式

8087数値データプロセッサの最も顕著な機能は次のとおりです。

整数型、浮動小数点型、および2〜10バイトの範囲の実数型のデータをサポートします。

処理速度が非常に速いため、2つの64ビット実数の乗算を約27 µsで計算でき、平方根を〜35 µsで計算することもできます。

IEEE浮動小数点標準に準拠しています。

8087アーキテクチャ

8087アーキテクチャは、2つのグループに分けられます。 Control Unit (CU)と Numeric Extension Unit (NEU)。

ザ・ control unit 命令の受信とデコード、メモリオペランドの読み取りと書き込み、並列キューの維持など、プロセッサとメモリ間のすべての通信を処理します。すべてのコプロセッサ命令はESC命令です。つまり、「F」で始まり、コプロセッサのみです。他の命令がマイクロプロセッサによって実行されている間、ESC命令を実行します。

ザ・ numeric extension unit算術命令、論理命令、超越命令、データ転送命令など、すべての数値プロセッサ命令を処理します。命令とその結果のオペランドを保持する8つのレジスタスタックがあります。

8087コプロセッサーのアーキテクチャーは次のとおりです。

8087ピンの説明

まず、8087 −のピン配列を見てみましょう。

次のリストは、8087-のピンの説明を示しています。

AD0 – AD15 −これらは時分割多重化されたアドレス/データラインであり、最初のクロックサイクル中にアドレスを伝送し、2番目のクロックサイクル以降のデータを伝送します。

A19 / S6 – A16/S−これらのラインは、時分割多重化されたアドレス/ステータスラインです。これは、8086ザSの対応するピンと同様に機能する6、S 4 SながらS3は、恒久的に高い5は永久的に低いです。

$\overline{BHE}$/S7 −最初のクロックサイクル中、 $\overline{BHE}$/ S 7は、ステータスラインがSとして8086台のデータバスの上位バイトに上とその作品の後にデータを有効にするために使用される7。

QS1, QS0 −これらは、次の表に示すように、命令キューのステータスとその状態を提供するキューステータス入力信号です。

| QS 0 | QS 1 | 状態 |

|---|---|---|

| 0 | 0 | 操作なし |

| 0 | 1 | キューからのオペコードの最初のバイト |

| 1 | 0 | キューを空にします |

| 1 | 1 | キューからの後続バイト |

INT −割り込み信号であり、実行中にマスクされていない例外を受信するとHighに変化します。

BUSY −これは出力信号であり、Highの場合、CPUにビジー状態を示します。

READY −バスがデータを受信する準備ができているかどうかをコプロセッサに通知するために使用される入力信号です。

RESET −これは、コプロセッサーの内部アクティビティーを拒否し、CPUが必要とするときにいつでも実行できるように準備するために使用される入力信号です。

CLK − CLK入力は、プロセッサ動作の基本的なタイミングを提供します。

VCC −これは電源信号であり、回路の動作には+ 5Vの電源が必要です。

S0, S1, S2−これらは、バスコントローラ8087がメモリおよびI / O制御信号を生成するために使用する動作のステータスを提供するステータス信号です。これらの信号は、4番目のクロックサイクル中にアクティブになります。

| S 2 | S 1 | S 0 | キューステータス |

|---|---|---|---|

| 0 | バツ | バツ | 未使用 |

| 1 | 0 | 0 | 未使用 |

| 1 | 0 | 1 | 読み取ったメモリ |

| 1 | 1 | 0 | メモリ書き込み |

| 1 | 1 | 1 | 受動的 |

RQ/GT1 & RQ/GT0 −これらは Request/Grant オペランド転送のためにホストプロセッサ8086/8088からバスの制御を取得するために8087プロセッサによって使用される信号。

この章では、8085を使用したメモリインターフェイスとIOインターフェイスについて説明します。

Interface2つのコンポーネント間の通信パスです。インターフェースには、メモリインターフェースとI / Oインターフェースの2種類があります。

メモリインターフェース

命令を実行するときは、命令コードとメモリに格納されているデータを読み取るためにメモリにアクセスするマイクロプロセッサが必要です。このため、メモリとマイクロプロセッサの両方で、レジスタからの読み取りとレジスタへの書き込みにいくつかの信号が必要です。

インターフェースプロセスには、メモリ要件とマイクロプロセッサ信号に一致するいくつかの重要な要素が含まれています。したがって、インターフェース回路は、メモリ信号の要件をマイクロプロセッサの信号と一致させるように設計する必要があります。

IOインターフェース

キーボード、マウス、プリンターなど、さまざまな通信デバイスがあります。そのため、ラッチとバッファーを使用して、キーボードやその他のデバイスをマイクロプロセッサーと接続する必要があります。このタイプのインターフェースは、I / Oインターフェースとして知られています。

メモリとI / Oインターフェースのブロック図

8085インターフェースピン

以下は、他のデバイスとのインターフェースに使用される8085ピンのリストです-

- A 15 -A 8(高アドレスバス)

- AD 7 -AD 0(下位アドレス/データバス)

- ALE

- RD

- WR

- READY

コミュニケーションの方法-外の世界とのマイクロプロセッサ?

マイクロプロセッサが外界と接続できる通信方法は2つあります。

- シリアル通信インターフェース

- パラレル通信インターフェース

Serial Communication Interface −このタイプの通信では、インターフェイスはマイクロプロセッサから1バイトのデータを取得し、それをビットごとに他のシステムにシリアルに送信します。その逆も同様です。

Parallel Communication Interface −このタイプの通信では、インターフェイスはマイクロプロセッサから1バイトのデータを取得し、それをビットごとに他のシステムに同時に(または)並列に送信します。その逆も同様です。

8279プログラマブルキーボード/ディスプレイコントローラーは、キーボードをCPUに接続するIntelによって設計されています。キーボードは最初にキーボードをスキャンし、キーが押されたかどうかを識別します。次に、押されたキーの相対応答をCPUに送信し、その逆も同様です。

キーボードがCPUとインターフェースする方法はいくつありますか?

キーボードは、割り込みモードまたはポーリングモードのいずれかでインターフェイスできます。の中にInterrupt mode、いずれかのキーが押された場合にのみプロセッサにサービスが要求されます。それ以外の場合、CPUはメインタスクを続行します。

の中に Polled mode、CPUは定期的に8279の内部フラグを読み取り、キーを押してもキーが押されているかどうかを確認します。

8279キーボードはどのように機能しますか?

キーボードは最大64個のキーで構成されており、キーコードを使用してCPUとインターフェイスします。これらのキーコードはデバウンスされ、CPUからアクセスできる8バイトのFIFORAMに格納されます。FIFOに8文字を超える文字が入力されている場合は、一度に8つを超えるキーが押されていることを意味します。これは、オーバーランステータスが設定されている場合です。

FIFOに有効なキーエントリが含まれている場合、CPUは割り込みモードで中断されます。それ以外の場合、CPUはポーリングのステータスをチェックしてエントリを読み取ります。CPUがキーエントリを読み取ると、FIFOが更新され、キーエントリがFIFOからプッシュされて、新しいエントリ用のスペースが生成されます。

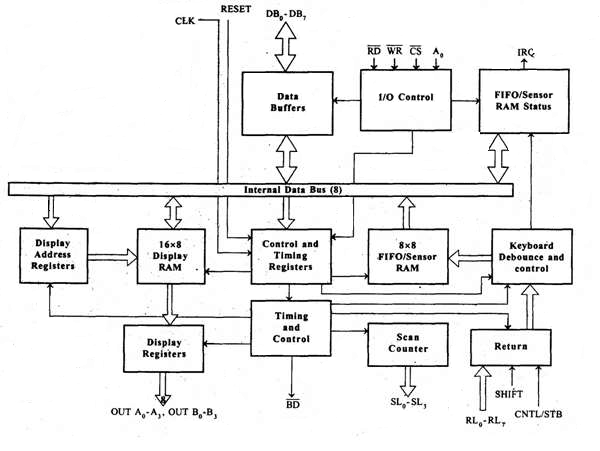

アーキテクチャと説明

I / O制御とデータバッファ

このユニットは、マイクロプロセッサを介したデータの流れを制御します。Dが低い場合にのみ有効になります。そのデータバッファは、システムの外部バスをマイクロプロセッサの内部バスに接続します。ピンA0、RD、およびWRは、コマンド、ステータス、またはデータの読み取り/書き込み操作に使用されます。

制御およびタイミングレジスタとタイミング制御

このユニットには、キーボード、表示モード、およびCPUによってプログラムされたその他の操作を格納するためのレジスタが含まれています。タイミングおよび制御ユニットは、回路の動作のタイミングを処理します。

スキャンカウンター

2つのモードがあります。 Encoded modeおよびデコードモード。エンコードモードでは、カウンターは、キーボードとディスプレイのスキャンラインを提供するために外部でデコードされるバイナリカウントを提供します。

の中に decoded scan mode、カウンタは内部最下位2ビットをデコードし、デコードされた1 SLにスキャン4から提供0 -SL 3。

リターンバッファ、キーボードデバウンス、および制御

このユニットは、最初にキークロージャーを行方向にスキャンし、見つかった場合は、キーボードデバウンスユニットがキーエントリをデバウンスします。同じキーが検出された場合、そのキーのコードは、SHIFT&CONTROLキーのステータスとともにセンサーRAMに直接転送されます。

FIFO /センサーRAMとステータスロジック

このユニットは、8バイトの先入れ先出し(FIFO)RAMとして機能し、押されたすべてのキーのキーコードがシーケンスに従ってRAMに入力されます。ステータスロジックは、FIFOが空になるまで、各FIFO読み取り操作の後に割り込み要求を生成します。

スキャンされたセンサーマトリックスモードでは、このユニットはセンサーRAMとして機能し、各行に対応するセンサー行のステータスがマトリックスに読み込まれます。センサーの状態が変化すると、IRQラインがHighに変化し、CPUに割り込みます。

ディスプレイアドレスレジスタとディスプレイRAM

このユニットは、CPUがディスプレイRAMとの間で現在読み書きしているワードのアドレスを保持するディスプレイアドレスレジスタで構成されています。

8279-ピンの説明

次の図は、8279 −のピン配列を示しています。

データバスライン、DB 0 -DB 7

これらは、CPUとの間でデータを転送するために使用される8つの双方向データバスラインです。

CLK

クロック入力は、マイクロプロセッサが必要とする内部タイミングを生成するために使用されます。

リセット

名前が示すように、このピンはマイクロプロセッサをリセットするために使用されます。

CSチップセレクト

このピンをローに設定すると、読み取り/書き込み操作が可能になります。それ以外の場合は、このピンをハイに設定する必要があります。

A 0

このピンは、コマンド/ステータス情報の転送を示します。低い場合は、データの転送を示します。

RD、WR

この読み取り/書き込みピンにより、データバッファはデータバスを介してデータを送受信できます。

IRQ

FIFOセンサーRAMにデータがある場合、この割り込み出力ラインはハイになります。FIFO RAMの読み取り操作ごとに、割り込みラインがローになります。ただし、FIFO RAMにCPUが読み取るキーコードエントリがさらに含まれている場合、このピンは再びHighになり、CPUへの割り込みが生成されます。

V ss、V cc

これらは、マイクロプロセッサのグランドおよび電源ラインです。

SL 0 − SL 3

これらは、キーボードマトリックスをスキャンして数字を表示するために使用されるスキャンラインです。これらのラインは、モード制御レジスタを使用して、エンコードまたはデコードとしてプログラムできます。

RL 0 − RL 7

これらは、キーの一方の端子に接続されているリターンラインであり、キーのもう一方の端子はデコードされたスキャンラインに接続されています。これらの行は、いずれかのキーが押されると0に設定されます。

シフト

シフト入力ラインのステータスは、スキャンされたキーボードモードのFIFOにすべてのキーコードとともに保存されます。キークロージャーで低くなるまで、内部で引き上げて高く保ちます

CNTL / STB-制御/ストロボI / Pモード

キーボードモードでは、このラインは制御入力として使用され、キーを閉じるとFIFOに保存されます。このラインは、ストローブ入力モードでデータをFIFORAMに入力するストローブラインです。内部プルアップがあります。キークロージャーでラインが引き下げられます。

BD

空白表示の略です。桁切り替え時に表示をブランクにするために使用します。

OUTA 0 - OUTA 3及びOUTB 0 - OUTB 3

これらは、2つの16x4または1つの16x8内部ディスプレイリフレッシュレジスタの出力ポートです。これらのラインからのデータは、ディスプレイとキーボードをスキャンするためにスキャンラインと同期されます。

8279の動作モード

8279には2つの動作モードがあります- Input Mode そして Output Mode。

入力モード

このモードはキーボードからの入力を処理し、このモードはさらに3つのモードに分類されます。

Scanned Keyboard Mode−このモードでは、キーマトリックスは、エンコードされたスキャンまたはデコードされたスキャンのいずれかを使用してインターフェイスできます。エンコードされたスキャン、8×8キーボード、またはデコードされたスキャンでは、4×8キーボードをインターフェースできます。SHIFTおよびCONTROLステータスで押されたキーのコードはFIFORAMに保存されます。

Scanned Sensor Matrix−このモードでは、エンコーダースキャンまたはデコーダースキャンのいずれかを使用して、センサーアレイをプロセッサーと接続できます。エンコーダースキャンでは、8×8センサーマトリックスまたはデコーダースキャンで4×8センサーマトリックスをインターフェースできます。

Strobed Input −このモードでは、制御ラインが0に設定されている場合、リターンラインのデータはバイトごとにFIFOに格納されます。

出力モード

このモードは、ディスプレイ関連の操作を処理します。このモードはさらに2つの出力モードに分類されます。

Display Scan −このモードでは、8/16文字の多重化ディスプレイをデュアル4ビット/シングル8ビットディスプレイユニットとして編成できます。

Display Entry −このモードでは、右側/左側からデータを入力して表示できます。

DMAはダイレクトメモリアクセスの略です。これは、データを最速で転送するようにIntelによって設計されています。これにより、デバイスはCPUの干渉なしに、メモリとの間でデータを直接転送できます。

デバイスはDMAコントローラを使用して、CPUにデータ、アドレス、および制御バスを保持するように要求するため、デバイスはメモリとの間でデータを直接自由に転送できます。DMAデータ転送は、CPUからHLDA信号を受信した後にのみ開始されます。

DMA操作はどのように実行されますか?

以下は、DMAによって実行される一連の操作です。

最初に、デバイスがデバイスとメモリの間でデータを送信する必要がある場合、デバイスはDMA要求(DRQ)をDMAコントローラーに送信する必要があります。

DMAコントローラーはホールド要求(HRQ)をCPUに送信し、CPUがHLDAをアサートするのを待ちます。

次に、マイクロプロセッサはすべてのデータバス、アドレスバス、および制御バスをトライステートにします。CPUはバスの制御を離れ、HLDA信号を介してHOLD要求を確認します。

これで、CPUはHOLD状態になり、DMAコントローラーは、CPU、メモリ、およびI / Oデバイス間のバスを介した操作を管理する必要があります。

8257の特徴

これが8257の顕著な特徴のいくつかのリストです-

4つのI / Oデバイスで使用できる4つのチャネルがあります。

各チャネルには、16ビットのアドレスと14ビットのカウンタがあります。

各チャネルは最大64kbのデータを転送できます。

各チャネルは個別にプログラムできます。

各チャネルは、読み取り転送、書き込み転送、および転送操作の検証を実行できます。

128バイトが転送されたというMARK信号を周辺機器に生成します。

単相クロックが必要です。

その周波数範囲は250Hzから3MHzです。

それは2つのモードで動作します。 Master mode そして Slave mode。

8257アーキテクチャ

次の画像は、8257-のアーキテクチャを示しています。

8257ピンの説明

次の画像は、8257DMAコントローラーのピン配列を示しています。

DRQ 0 −DRQ3

これらは、DMAサービスを使用するために周辺機器によって使用される4つの個別のチャネルDMA要求入力です。固定優先モードが選択された場合、その後、DRQ 0は最高の優先順位を有し、DRQ 3は、それらの間で最低の優先度を有します。

DACK o − DACK 3

これらはアクティブローDMA確認応答ラインであり、CPUによる要求のステータスについて要求しているペリフェラルを更新します。これらのラインは、要求元のデバイスのストロボラインとしても機能します。

D o − D 7

これらは双方向のデータラインであり、システムバスをDMAコントローラの内部データバスとインターフェイスさせるために使用されます。スレーブモードでは、コマンドワードを8257に、ステータスワードを8257から伝送します。マスターモードでは、これらのラインを使用して、生成されたアドレスの上位バイトをラッチに送信します。このアドレスは、ADSTB信号を使用してさらにラッチされます。

IOR

これはアクティブローの双方向トライステート入力ラインであり、CPUがスレーブモードで8257の内部レジスタを読み取るために使用します。マスターモードでは、メモリ書き込みサイクル中に周辺機器からデータを読み取るために使用されます。

IOW

これはアクティブロー双方向トライステートラインであり、データバスの内容を8ビットモードレジスタまたは16ビットDMAアドレスレジスタまたはターミナルカウントレジスタの上位/下位バイトにロードするために使用されます。マスターモードでは、DMAメモリの読み取りサイクル中に周辺機器にデータをロードするために使用されます。

CLK

8257の内部動作に必要なクロック周波数信号です。

リセット

この信号は、すべてのDMAチャネルを無効にすることによってDMAコントローラーをリセットするために使用されます。

A o -A 3

これらは、4つの最下位アドレス行です。スレーブモードでは、これらは入力として機能し、読み取りまたは書き込みを行うレジスタの1つを選択します。マスターモードでは、これらは8257によって生成される4つの最下位メモリアドレス出力ラインです。

CS

アクティブローチップセレクトラインです。スレーブモードでは、8257との間の読み取り/書き込み操作を有効にします。マスターモードでは、8257との間の読み取り/書き込み操作を無効にします。

A 4 -A 7

これらは、マスターモードでDMAによって生成された下位バイトアドレスの上位ニブルです。

準備完了

これはアクティブハイの非同期入力信号であり、待機状態を挿入することでDMAを準備します。

HRQ

この信号は、出力デバイスからホールド要求信号を受信するために使用されます。スレーブモードでは、DRQ入力ライン8257に接続されます。マスターモードでは、CPUのHOLD入力に接続されます。

HLDA

これは、バスが1に設定されている場合に、CPUによって要求側ペリフェラルにバスが許可されたことをDMAコントローラに示すホールド確認信号です。

MEMR

これは、DMA読み取りサイクル中にアドレス指定されたメモリ位置からデータを読み取るために使用される低メモリ読み取り信号です。

MEMW

これは、DMA書き込み操作中にアドレス指定されたメモリ位置にデータを書き込むために使用されるアクティブローの3ステート信号です。

ADST

この信号は、DMAコントローラによって生成されたメモリアドレスの上位バイトをラッチに変換するために使用されます。

AEN

この信号は、アドレスバス/データバスを無効にするために使用されます。

TC

これは「ターミナルカウント」の略で、現在の周辺機器への現在のDMAサイクルを示します。

マーク

マークは、最初から128サイクルまたはその整数倍ごとにアクティブになります。これは、現在のDMAサイクルが、選択した周辺機器への前回のMARK出力から128番目のサイクルであることを示しています。

V cc

回路の動作に必要なのは電力信号です。

A microcontroller は小型で低コストのマイクロコンピュータであり、マイクロ波の情報の表示、リモート信号の受信など、組み込みシステムの特定のタスクを実行するように設計されています。

一般的なマイクロコントローラは、プロセッサ、メモリ(RAM、ROM、EPROM)、シリアルポート、周辺機器(タイマー、カウンタ)などで構成されています。

マイクロプロセッサとマイクロコントローラの違い

次の表は、マイクロプロセッサとマイクロコントローラの違いを示しています。

| マイクロコントローラー | マイクロプロセッサ |

|---|---|

| マイクロコントローラーは、アプリケーション内で単一のタスクを実行するために使用されます。 | マイクロプロセッサは大きなアプリケーションに使用されます。 |

| その設計とハードウェアのコストは低いです。 | その設計とハードウェアのコストは高いです。 |

| 交換が簡単。 | 交換はそれほど簡単ではありません。 |

| これは、動作に必要な電力が少ないCMOSテクノロジで構築されています。 | システム全体を制御する必要があるため、消費電力が高くなります。 |

| CPU、RAM、ROM、I / Oポートで構成されています。 | RAM、ROM、I / Oポートで構成されていません。ピンを使用して周辺機器に接続します。 |

マイクロコントローラーの種類

マイクロコントローラは、メモリ、アーキテクチャ、ビット、および命令セットに基づいてさまざまなカテゴリに分類されます。以下はそれらのタイプのリストです-

ビット

ビット構成に基づいて、マイクロコントローラはさらに3つのカテゴリに分類されます。

8-bit microcontroller −このタイプのマイクロコントローラーは、加算、減算、乗算除算などの算術演算および論理演算を実行するために使用されます。たとえば、Intel8031および8051は8ビットのマイクロコントローラーです。

16-bit microcontroller−このタイプのマイクロコントローラーは、より高い精度とパフォーマンスが要求される算術演算および論理演算を実行するために使用されます。たとえば、Intel8096は16ビットマイクロコントローラです。

32-bit microcontroller −このタイプのマイクロコントローラは、一般に、自動操作機、医療機器などの自動制御機器で使用されます。

記憶

メモリ構成に基づいて、マイクロコントローラはさらに2つのカテゴリに分類されます。

External memory microcontroller−このタイプのマイクロコントローラは、チップ上にプログラムメモリを持たないように設計されています。そのため、外部メモリマイクロコントローラと呼ばれています。例:Intel8031マイクロコントローラー。

Embedded memory microcontroller−このタイプのマイクロコントローラは、マイクロコントローラにすべてのプログラムとデータメモリ、カウンタとタイマー、割り込み、I / Oポートがチップに組み込まれるように設計されています。例:Intel8051マイクロコントローラー。

指図書

命令セット構成に基づいて、マイクロコントローラはさらに2つのカテゴリに分類されます。

CISC− CISCは、複雑な命令セットコンピュータの略です。これにより、ユーザーは多くの単純な命令の代わりに単一の命令を挿入できます。

RISC− RISCは、縮小命令セットコンピュータの略です。命令あたりのクロックサイクルを短縮することにより、動作時間を短縮します。

マイクロコントローラーのアプリケーション

マイクロコントローラは、次のようなさまざまなデバイスで広く使用されています。

LEDのような光感知および制御装置。

電子レンジ、煙突などの温度検知および制御デバイス。

火災警報器のような火災検知および安全装置。

電圧計のような測定装置。

8051マイクロコントローラーは1981年にIntelによって設計されました。これは8ビットマイクロコントローラーです。40ピンDIP(デュアルインラインパッケージ)、4kbのROMストレージと128バイトのRAMストレージ、2つの16ビットタイマーで構築されています。これは、4つの並列8ビットポートで構成されており、要件に応じてプログラム可能であり、アドレス指定も可能です。オンチップ水晶発振器は、12MHzの水晶周波数を持つマイクロコントローラーに統合されています。

ここで、8051マイクロコントローラーのアーキテクチャについて説明します。

次の図では、システムバスがすべてのサポートデバイスをCPUに接続しています。システムバスは、8ビットのデータバス、16ビットのアドレスバス、およびバス制御信号で構成されています。プログラムメモリ、ポート、データメモリ、シリアルインターフェイス、割り込み制御、タイマー、CPUなどの他のすべてのデバイスは、すべてシステムバスを介して相互にインターフェイスされます。

8051マイクロコントローラのピン配列は次のようになります-

Pins 1 to 8−これらのピンはポート1と呼ばれます。このポートは他の機能を果たしません。内部でプルアップされた双方向I / Oポートです。

Pin 9 −マイクロコントローラを初期値にリセットするために使用されるRESETピンです。

Pins 10 to 17 −これらのピンはポート3と呼ばれます。このポートは、割り込み、タイマー入力、制御信号、シリアル通信信号RxDおよびTxDなどのいくつかの機能を提供します。

Pins 18 & 19 −これらのピンは、システムクロックを取得するために外部水晶をインターフェースするために使用されます。

Pin 20 −このピンは回路に電源を供給します。

Pins 21 to 28−これらのピンはポート2と呼ばれます。これはI / Oポートとして機能します。高次アドレスバス信号もこのポートを使用して多重化されます。

Pin 29−これは、Program StoreEnableを表すPSENピンです。外部プログラムメモリから信号を読み取るために使用されます。

Pin 30−これは外部アクセス入力を表すEAピンです。これは、外部メモリインターフェイスを有効/無効にするために使用されます。

Pin 31−これはアドレスラッチイネーブルを表すALEピンです。ポートのアドレスデータ信号を逆多重化するために使用されます。

Pins 32 to 39−これらのピンはポート0と呼ばれます。これはI / Oポートとして機能します。下位アドレスとデータバス信号は、このポートを使用して多重化されます。

Pin 40 −このピンは、回路に電源を供給するために使用されます。

8051マイクロコントローラにはそれぞれ8ビットの4つのI / Oポートがあり、入力または出力として構成できます。したがって、合計32の入力/出力ピンにより、マイクロコントローラを周辺機器に接続できます。

Pin configurationつまり、論理状態に応じて、ピンを入力用に1、出力用に0として構成できます。

Input/Output (I/O) pin −マイクロコントローラ内のすべての回路は、プルアップ抵抗が組み込まれていないため、P0ポートを除くピンの1つに接続する必要があります。

Input pin−ロジック1はPレジスタのビットに適用されます。出力FEトランジスタはオフになり、もう一方のピンは高抵抗のプルアップ抵抗を介して電源電圧に接続されたままになります。

Port 0 − P0(ゼロ)ポートは2つの機能によって特徴付けられます−

外部メモリを使用する場合は、下位アドレスバイト(アドレスA0A7)が適用されます。それ以外の場合、このポートのすべてのビットが入力/出力として構成されます。

P0ポートが出力として構成されている場合、プルアップ抵抗が組み込まれたピンで構成されている他のポートの端が5V電源に接続されている場合、このポートのピンではこの抵抗が省略されます。

入力構成

このポートのいずれかのピンが入力として構成されている場合、それは「フロート」しているかのように機能します。つまり、入力には無制限の入力抵抗と不確定な電位があります。

出力構成

ピンが出力として構成されている場合、それは「オープンドレイン」として機能します。ロジック0をポートビットに適用することにより、適切なピンがグランド(0V)に接続され、ロジック1を適用することにより、外部出力は「フローティング」を維持します。

この出力ピンにロジック1(5V)を適用するには、外部プルアップ抵抗を構築する必要があります。

ポート1

P1は、P0のような代替機能がないため、真のI / Oポートですが、このポートは一般的なI / Oとしてのみ構成できます。プルアップ抵抗を内蔵しており、TTL回路と完全に互換性があります。

ポート2

P2は、外部メモリを使用する場合のP0と同様です。このポートのピンは、外部メモリチップ用のアドレスを占有します。このポートは、アドレスA8〜A15の上位アドレスバイトに使用できます。メモリが追加されていない場合、このポートはポート1と同様に一般的な入出力ポートとして使用できます。

ポート3

このポートでは、ロジック1をP3レジスタの適切なビットに適用する必要があることを除いて、機能は他のポートと同様です。

ピン電流制限

ピンが出力(つまりロジック0)として構成されている場合、シングルポートピンは10mAの電流を受け取ることができます。

これらのピンが入力(つまりロジック1)として構成されている場合、内蔵のプルアップ抵抗は非常に弱い電流を供給しますが、LSシリーズの最大4つのTTL入力をアクティブにすることができます。

ポートの8ビットすべてがアクティブな場合、合計電流を15mAに制限する必要があります(ポートP0:26mA)。

すべてのポート(32ビット)がアクティブな場合、合計最大電流は71mAに制限する必要があります。

割り込みは、メインプログラムを一時的に中断し、制御を外部ソースに渡し、それらのタスクを実行するイベントです。次に、中断したメインプログラムに制御を渡します。

8051には、INT0、TFO、INT1、TF1、RI / TIの5つの割り込み信号があります。各割り込みはIEレジスタのビットを設定することで有効または無効にでき、割り込みシステム全体は同じレジスタのEAビットをクリアすることで無効にできます。

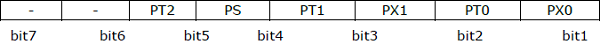

IE(割り込みイネーブル)レジスタ

このレジスタは、割り込みの有効化と無効化を担当します。EAレジスタは、割り込みを有効にする場合は1に設定され、割り込みを無効にする場合は0に設定されます。そのビットシーケンスとその意味を次の図に示します。

| EA | IE.7 | すべての割り込みを無効にします。EA = 0の場合、割り込みは確認されず、EA = 1では個別に割り込みが有効になります。 |

| - | IE.6 | 将来の使用のために予約されています。 |

| - | IE.5 | 将来の使用のために予約されています。 |

| ES | IE.4 | シリアルポート割り込みを有効/無効にします。 |

| ET1 | IE.3 | timer1オーバーフロー割り込みを有効/無効にします。 |

| EX1 | IE.2 | 外部割り込みを有効/無効にします1。 |

| ET0 | IE.1 | timer0オーバーフロー割り込みを有効/無効にします。 |

| EX0 | IE.0 | 外部割り込み0を有効/無効にします。 |

IP(割り込み優先度)レジスタ

次の図に示すように、割り込み優先度(IP)レジスタの対応するビットを変更することにより、割り込みの優先度レベルを変更できます。

優先度の低い割り込みは、優先度の高い割り込みによってのみ中断できますが、優先度の低い別の割り込みによって中断することはできません。

優先度の異なる2つの割り込みを同時に受信した場合、優先度の高い要求に対応します。

同じ優先度レベルの要求が同時に受信された場合、内部ポーリングシーケンスによって、処理される要求が決定されます。

| - | IP.6 | 将来の使用のために予約されています。 |

| - | IP.5 | 将来の使用のために予約されています。 |

| PS | IP.4 | シリアルポート割り込みの優先度を定義します。 |

| PT1 | IP.3 | 1優先度のタイマー割り込みを定義します。 |

| PX1 | IP.2 | 外部割り込みの優先度を定義します。 |

| PT0 | IP.1 | timer0割り込み優先度レベルを定義します。 |

| PX0 | IP.0 | 優先度0の外部割り込みを定義します。 |

TCONレジスタ

TCONレジスタは、マイクロコントローラへの外部割り込みのタイプを指定します。

8255Aは、必要に応じて特定の条件下でI / Oからデータを転送してI / Oを中断するように設計された汎用のプログラム可能なI / Oデバイスです。ほとんどすべてのマイクロプロセッサで使用できます。

これは、要件に応じて構成できる3つの8ビット双方向I / Oポート(24I / Oライン)で構成されています。

8255Aのポート

8255Aには、ポートA、ポートB、およびポートCの3つのポートがあります。

Port A 1つの8ビット出力ラッチ/バッファと1つの8ビット入力バッファが含まれています。

Port B ポートAに似ています。

Port C 制御ワードにより、ポートC下部(PC0-PC3)とポートC上部(PC7-PC4)の2つの部分に分割できます。

これらの3つのポートは、さらに2つのグループに分けられます。つまり、グループAにはポートAと上部ポートCが含まれます。グループBにはポートBと下部ポートCが含まれます。これら2つのグループは、3つの異なるモードでプログラムできます。つまり、最初のモードはモードと呼ばれます。 0の場合、2番目のモードはモード1と呼ばれ、3番目のモードはモード2と呼ばれます。

動作モード

8255Aには3つの異なる動作モードがあります-

Mode 0−このモードでは、ポートAとBが2つの8ビットポートとして使用され、ポートCが2つの4ビットポートとして使用されます。各ポートは、出力がラッチされ、入力がラッチされない入力モードまたは出力モードのいずれかでプログラムできます。ポートには割り込み機能がありません。

Mode 1−このモードでは、ポートAとBが8ビットI / Oポートとして使用されます。これらは、入力ポートまたは出力ポートとして構成できます。各ポートは、ハンドシェイク信号としてポートCからの3本のラインを使用します。入力と出力はラッチされます。

Mode 2−このモードでは、ポートAを双方向ポートとして構成し、ポートBをモード0またはモード1のいずれかに構成できます。ポートAは、データ転送のハンドシェイク信号としてポートCからの5つの信号を使用します。ポートCからの残りの3つの信号は、単純なI / OまたはポートBのハンドシェイクとして使用できます。

8255Aの機能

8255Aの顕著な特徴は次のとおりです-

これは、3つの8ビットIOポート、つまりPA、PB、およびPCで構成されています。

アドレス/データバスは外部でデマックスする必要があります。

TTL互換です。

DC駆動能力が向上しています。

8255アーキテクチャ

次の図は、8255Aのアーキテクチャを示しています。

まず、Intel8255Aのピン配列を見てみましょう。

ここで、8255Aのピンの機能説明について説明します。

データバスバッファ

これはトライステート8ビットバッファであり、マイクロプロセッサをシステムデータバスに接続するために使用されます。データは、CPUの指示に従って、バッファによって送受信されます。制御ワードとステータス情報もこのバスを使用して転送されます。

読み取り/書き込み制御ロジック

このブロックは、データ/制御/ステータスワードの内部/外部転送を制御する役割を果たします。CPUアドレスと制御バスからの入力を受け入れ、両方の制御グループにコマンドを発行します。

CS

チップセレクトの略です。この入力のLOWはチップを選択し、8255AとCPU間の通信を有効にします。これは、デコードされたアドレスに接続され、A 0およびA 1は、マイクロプロセッサのアドレス線に接続されています。

それらの結果は以下の条件に依存します-

| CS | A 1 | A 0 | 結果 |

|---|---|---|---|

| 0 | 0 | 0 | ポートA |

| 0 | 0 | 1 | ポートB |

| 0 | 1 | 0 | ポートC |

| 0 | 1 | 1 | 制御レジスタ |

| 1 | バツ | バツ | 選択なし |

WR

書き込みの略です。この制御信号により、書き込み動作が可能になります。この信号がローになると、マイクロプロセッサは選択されたI / Oポートまたは制御レジスタに書き込みます。

リセット

これはアクティブハイ信号です。制御レジスタをクリアし、すべてのポートを入力モードに設定します。

RD

Readの略です。この制御信号により、読み出し動作が可能になります。信号がローの場合、マイクロプロセッサは8255の選択されたI / Oポートからデータを読み取ります。

0とA 1

これらの入力信号は、RD、WR、および制御信号の1つで機能します。以下は、さまざまな信号とその結果を示す表です。

| A 1 | A 0 | RD | WR | CS | 結果 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | Input Operation ポートA→データバス |

| 0 | 1 | 0 | 1 | 0 | ポートB→データバス |

| 1 | 0 | 0 | 1 | 0 | ポートC→データバス |

| 0 | 0 | 1 | 0 | 0 | Output Operation データバス→ポートA |

| 0 | 1 | 1 | 0 | 0 | データバス→ポートA |

| 1 | 0 | 1 | 0 | 0 | データバス→ポートB |

| 1 | 1 | 1 | 0 | 0 | データバス→ポートD |

Intel 8253および8254は、マイクロプロセッサが3つの16ビットレジスタを使用してタイミングおよびカウント機能を実行するために設計されたプログラマブルインターバルタイマー(PTI)です。各カウンタには、クロックとゲートの2つの入力ピンと、「OUT」出力用の1つのピンがあります。カウンタを操作するために、16ビットカウントがそのレジスタにロードされます。コマンドで、0に達するまでカウントをデクリメントし始め、次にCPUに割り込むために使用できるパルスを生成します。

8253と8254の違い

次の表は、8253と8254の機能を区別しています。

| 8253 | 8254 |

|---|---|

| その動作周波数は0〜2.6MHzです | その動作周波数は0〜10MHzです |

| N-MOSテクノロジーを使用しています | H-MOSテクノロジーを使用しています |

| リードバックコマンドは使用できません | リードバックコマンドが使用可能です |

| 同じカウンタの読み取りと書き込みをインターリーブすることはできません。 | 同じカウンタの読み取りと書き込みをインターリーブできます。 |

8253/54の特徴

8253/54の最も顕著な特徴は次のとおりです-

3つの独立した16ビットダウンカウンターがあります。

DCから10MHzまでの入力を処理できます。

これらの3つのカウンターは、バイナリカウントまたはBCDカウントのいずれかにプログラムできます。

ほとんどすべてのマイクロプロセッサと互換性があります。

8254には、READ BACKコマンドと呼ばれる強力なコマンドがあります。これにより、ユーザーは、カウント値、プログラムされたモード、現在のモード、およびカウンターの現在のステータスを確認できます。

8254アーキテクチャ

8254のアーキテクチャは次のようになります-

8254ピンの説明

これが8254のピン配列です-

上の図では、3つのカウンター、データバスバッファー、読み取り/書き込み制御ロジック、および制御レジスタがあります。各カウンタには、2つの入力信号(CLOCK&GATE)と1つの出力信号(OUT)があります。

データバスバッファ

これは、8253/54をシステムデータバスにインターフェイスするために使用される、トライステート、双方向、8ビットのバッファです。それは3つの基本的な機能を持っています-

- 8253/54のモードのプログラミング。

- カウントレジスタをロードしています。

- カウント値の読み取り。

読み取り/書き込みロジック

それは5つの信号、すなわちRD、WR、CS、およびアドレス線A含む0&A 1。周辺I / Oモードでは、RD信号とWR信号はそれぞれIORとIOWに接続されます。メモリマップドI / Oモードでは、これらはMEMRおよびMEMWに接続されます。

アドレスラインA 0&A 1 CPUのは、ラインAに接続されている0とA 1 54分の8253の、およびCSはデコードされたアドレスに関連付けられています。制御ワードレジスタおよびカウンタは、ラインA上の信号に応じて選択される0&A 1。

| A 1 | A 0 | 結果 |

|---|---|---|

| 0 | 0 | カウンター0 |

| 0 | 1 | カウンター1 |

| 1 | 0 | カウンター2 |

| 1 | 1 | コントロールワードレジスタ |

| バツ | バツ | 選択なし |

コントロールワードレジスタ

このレジスタは、アクセスされたときの線A 0およびA 1論理1で、コマンドの使用するカウンタを指定する単語、そのモード、及びいずれかの読み取りまたは書き込み動作を記述するために使用されます。次の表は、さまざまな制御入力の結果を示しています。

| A 1 | A 0 | RD | WR | CS | 結果 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | カウンタ0を書き込む |

| 0 | 1 | 1 | 0 | 0 | 書き込みカウンター1 |

| 1 | 0 | 1 | 0 | 0 | カウンター2を書く |

| 1 | 1 | 1 | 0 | 0 | コントロールワードを書く |

| 0 | 0 | 0 | 1 | 0 | カウンタ0の読み取り |

| 0 | 1 | 0 | 1 | 0 | カウンター1を読む |

| 1 | 0 | 0 | 1 | 0 | カウンター2を読む |

| 1 | 1 | 0 | 1 | 0 | 操作なし |

| バツ | バツ | 1 | 1 | 0 | 操作なし |

| バツ | バツ | バツ | バツ | 1 | 操作なし |

カウンター

各カウンタは、バイナリまたはBCDのいずれかで操作できる単一の16ビットダウンカウンタで構成されています。その入力と出力は、制御ワードレジスタに格納されているモードの選択によって構成されます。プログラマーは、処理中の実際のカウントを妨げることなく、3つのカウンターのいずれかの内容を読み取ることができます。

8253/54は6つの異なるモードで操作できます。この章では、これらの動作モードについて説明します。

モード0─ターミナルカウントでの割り込み

これは、特定の間隔の後にマイクロプロセッサへの割り込みを生成するために使用されます。

モードが設定された後、最初は出力がローです。カウント値がカウンターにロードされた後、出力はLOWのままです。

カウンタをデクリメントするプロセスは、ターミナルカウントに達するまで続きます。つまり、カウントがゼロになり、出力がHIGHになり、新しいカウントをリロードするまでHighのままになります。

GATE信号は、通常のカウントではハイです。GATEがローになると、カウントが終了し、GATEが再びハイになるまで現在のカウントがラッチされます。

モード1–プログラム可能なワンショット

モノ安定マルチバイブレータとして使用できます。

このモードでは、ゲート入力がトリガー入力として使用されます。

カウントがロードされてトリガーが適用されるまで、出力はハイのままです。

モード2–レートジェネレータ

通常、初期化後の出力はハイです。

カウントがゼロになるたびに、出力で別のローパルスが生成され、カウンタがリロードされます。

モード3–方形波発生器

このモードはモード2と似ていますが、出力がタイマー期間の半分の間ローのままで、残りの半分の間ハイのままである点が異なります。

モード4-ソフトウェアトリガーモード

このモードでは、タイマーがゼロにカウントされるまで出力はハイのままになり、ゼロにカウントされると、出力はパルスローになり、その後再びハイになります。

GATE信号がLOWになると、カウントがラッチされます。

端子カウントでは、出力は1クロックサイクルの間ローになり、次にハイになります。この低パルスはストロボとして使用できます。

モード5–ハードウェアトリガーモード

このモードは、外部で生成された信号に応答してストロボを生成します。

このモードはモード4と似ていますが、カウントがゲート入力の信号によって開始される点が異なります。つまり、ソフトウェアによってトリガーされるのではなく、ハードウェアによってトリガーされます。

初期化後、出力はハイになります。

端子数に達すると、出力は1クロックサイクルの間ローになります。