並列コンピュータアーキテクチャ-モデル

並列処理は、実際のアプリケーションでのより高いパフォーマンス、より低いコスト、および正確な結果に対する要求を満たすために、最新のコンピューターで効果的なテクノロジーとして開発されました。マルチプログラミング、マルチプロセッシング、またはマルチコンピューティングの実践により、今日のコンピューターでは並行イベントが一般的です。

最新のコンピューターには、強力で広範なソフトウェアパッケージがあります。コンピュータのパフォーマンスの発達を分析するには、まずハードウェアとソフトウェアの基本的な発達を理解する必要があります。

Computer Development Milestones −コンピュータの開発には2つの主要な段階があります- mechanical または electromechanical部品。現代のコンピューターは、電子部品の導入後に進化しました。電子コンピュータの高移動度電子は、機械式コンピュータの操作部品に取って代わりました。情報伝達のために、ほとんど光の速度で伝わる電気信号は、機械的な歯車またはレバーに取って代わった。

Elements of Modern computers −最新のコンピュータシステムは、コンピュータハードウェア、命令セット、アプリケーションプログラム、システムソフトウェア、およびユーザーインターフェイスで構成されています。

コンピューティングの問題は、数値コンピューティング、論理的推論、およびトランザクション処理に分類されます。一部の複雑な問題では、3つの処理モードすべての組み合わせが必要になる場合があります。

Evolution of Computer Architecture−過去40年間で、コンピュータアーキテクチャは革命的な変化を遂げました。私たちはフォンノイマンアーキテクチャから始めましたが、今ではマルチコンピュータとマルチプロセッサがあります。

Performance of a computer system−コンピュータシステムのパフォーマンスは、マシンの機能とプログラムの動作の両方に依存します。マシンの機能は、より優れたハードウェアテクノロジー、高度なアーキテクチャ機能、および効率的なリソース管理によって向上させることができます。プログラムの動作は、アプリケーションと実行時の条件に依存するため、予測できません。

マルチプロセッサとマルチコンピュータ

このセクションでは、2種類の並列コンピューターについて説明します。

- Multiprocessors

- Multicomputers

共有メモリマルチコンピュータ

最も一般的な3つの共有メモリマルチプロセッサモデルは次のとおりです。

ユニフォームメモリアクセス(UMA)

このモデルでは、すべてのプロセッサが物理メモリを均一に共有します。すべてのプロセッサは、すべてのメモリワードへのアクセス時間が等しくなります。各プロセッサには、プライベートキャッシュメモリがあります。周辺機器についても同じルールが適用されます。

すべてのプロセッサがすべての周辺機器に平等にアクセスできる場合、そのシステムは symmetric multiprocessor。1つまたは少数のプロセッサのみが周辺機器にアクセスできる場合、そのシステムはasymmetric multiprocessor。

不均一メモリアクセス(NUMA)

NUMAマルチプロセッサモデルでは、アクセス時間はメモリワードの場所によって異なります。ここで、共有メモリは、ローカルメモリと呼ばれるすべてのプロセッサに物理的に分散されています。すべてのローカルメモリのコレクションは、すべてのプロセッサがアクセスできるグローバルアドレス空間を形成します。

キャッシュオンリーメモリアーキテクチャ(COMA)

COMAモデルは、NUMAモデルの特殊なケースです。ここでは、すべての分散メインメモリがキャッシュメモリに変換されます。

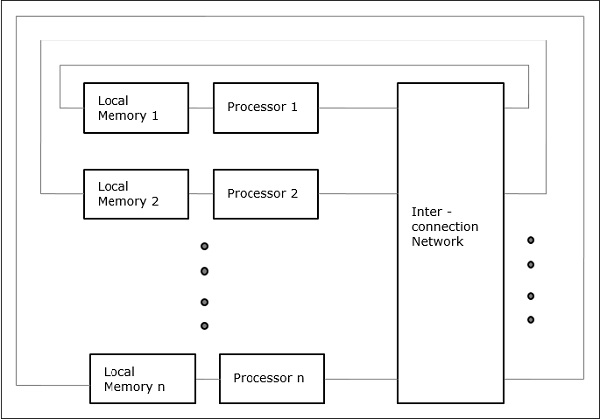

Distributed - Memory Multicomputers−分散メモリマルチコンピュータシステムは、メッセージパッシングネットワークによって相互接続されたノードと呼ばれる複数のコンピュータで構成されています。各ノードは、プロセッサ、ローカルメモリ、場合によってはI / Oデバイスを備えた自律型コンピュータとして機能します。この場合、すべてのローカルメモリはプライベートであり、ローカルプロセッサのみがアクセスできます。これが、従来の機械が呼ばれる理由ですno-remote-memory-access (NORMA) マシン。

マルチベクトルおよびSIMDコンピューター

このセクションでは、ベクトル処理とデータ並列処理のためのスーパーコンピューターと並列プロセッサーについて説明します。

ベクトルスーパーコンピューター

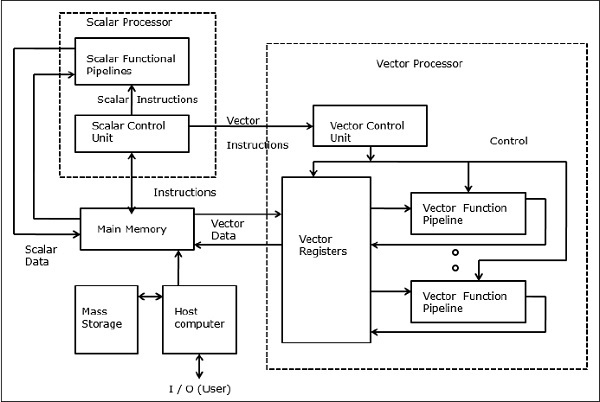

ベクトルコンピュータでは、オプション機能としてベクトルプロセッサがスカラープロセッサに接続されています。ホストコンピュータは最初にプログラムとデータをメインメモリにロードします。次に、スカラー制御ユニットがすべての命令をデコードします。デコードされた命令がスカラー演算またはプログラム演算である場合、スカラープロセッサはスカラー関数パイプラインを使用してそれらの演算を実行します。

一方、デコードされた命令がベクトル演算の場合、命令はベクトル制御ユニットに送信されます。

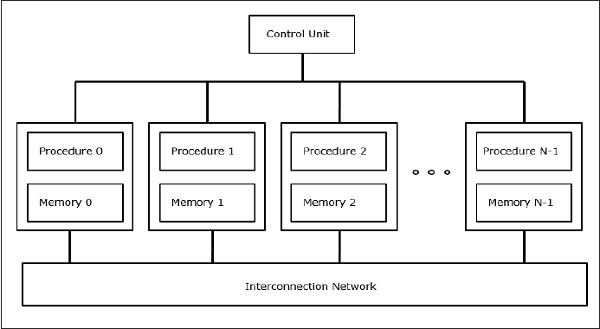

SIMDスーパーコンピューター

SIMDコンピュータでは、「N」個のプロセッサが制御ユニットに接続されており、すべてのプロセッサに個別のメモリユニットがあります。すべてのプロセッサは相互接続ネットワークによって接続されています。

PRAMおよびVLSIモデル

理想的なモデルは、物理的な制約や実装の詳細を考慮せずに、並列アルゴリズムを開発するための適切なフレームワークを提供します。

モデルを適用して、並列コンピューターで理論上のパフォーマンスの限界を取得したり、チップ領域のVLSIの複雑さとチップが製造される前の動作時間を評価したりできます。

並列ランダムアクセスマシン

Sheperdson and Sturgis(1963)は、従来のユニプロセッサコンピュータをランダムアクセスマシン(RAM)としてモデル化しました。Fortune and Wyllie(1978)は、メモリアクセスのオーバーヘッドと同期がゼロの理想的な並列コンピューターをモデル化するための並列ランダムアクセスマシン(PRAM)モデルを開発しました。

NプロセッサPRAMには共有メモリユニットがあります。この共有メモリは、一元化することも、プロセッサ間で分散させることもできます。これらのプロセッサは、同期された読み取りメモリ、書き込みメモリ、および計算サイクルで動作します。したがって、これらのモデルは、同時読み取りおよび書き込み操作の処理方法を指定します。

可能なメモリ更新操作は次のとおりです-

Exclusive read (ER) −この方法では、各サイクルで1つのプロセッサのみが任意のメモリ位置からの読み取りを許可されます。

Exclusive write (EW) −この方法では、少なくとも1つのプロセッサが一度にメモリ位置に書き込むことができます。

Concurrent read (CR) −複数のプロセッサが同じサイクルで同じメモリ位置から同じ情報を読み取ることができます。

Concurrent write (CW)−同じメモリ位置への同時書き込み操作が可能です。書き込みの競合を回避するために、いくつかのポリシーが設定されています。

VLSI複雑性モデル

並列コンピュータは、VLSIチップを使用して、プロセッサアレイ、メモリアレイ、および大規模なスイッチングネットワークを製造します。

今日、VLSI技術は2次元です。VLSIチップのサイズは、そのチップで使用可能なストレージ(メモリ)スペースの量に比例します。

アルゴリズムのスペースの複雑さは、そのアルゴリズムのVLSIチップ実装のチップ面積(A)によって計算できます。Tがアルゴリズムの実行に必要な時間(レイテンシー)である場合、ATはチップ(またはI / O)を介して処理されるビットの総数の上限を示します。特定のコンピューティングでは、次のような下限f(s)が存在します。

AT 2 > = O(f(s))

ここで、A =チップ面積およびT =時間

建築開発トラック

私が次のトラックに沿って広めた並列コンピューターの進化-

- 複数のプロセッサトラック

- マルチプロセッサトラック

- マルチコンピュータートラック

- 複数のデータトラック

- ベクタートラック

- SIMDトラック

- 複数のスレッドが追跡します

- マルチスレッドトラック

- データフロートラック

に multiple processor track、異なるスレッドが異なるプロセッサで同時に実行され、共有メモリ(マルチプロセッサトラック)またはメッセージパッシング(マルチコンピュータトラック)システムを介して通信すると想定されています。

に multiple data track、同じコードが大量のデータに対して実行されると想定されています。これは、データ要素のシーケンス(ベクタートラック)で同じ命令を実行するか、同様のデータセット(SIMDトラック)で同じ命令のシーケンスを実行することによって行われます。

に multiple threads track、異なるプロセッサで実行されているスレッド間の同期遅延を隠すために、同じプロセッサでのさまざまなスレッドのインターリーブ実行が想定されています。スレッドのインターリーブは、粗い(マルチスレッドトラック)または細かい(データフロートラック)ことができます。