Sistemas Embarcados - Tipos de Arquitetura

Os microcontroladores 8051 funcionam com barramento de dados de 8 bits. Portanto, eles podem suportar memória de dados externa de até 64K e memória de programa externa de 64K, no máximo. Coletivamente, os microcontroladores 8051 podem endereçar 128k de memória externa.

Quando os dados e o código estão em diferentes blocos de memória, a arquitetura é referida como Harvard architecture. Caso os dados e o código estejam no mesmo bloco de memória, a arquitetura é referida comoVon Neumann architecture.

Arquitetura Von Neumann

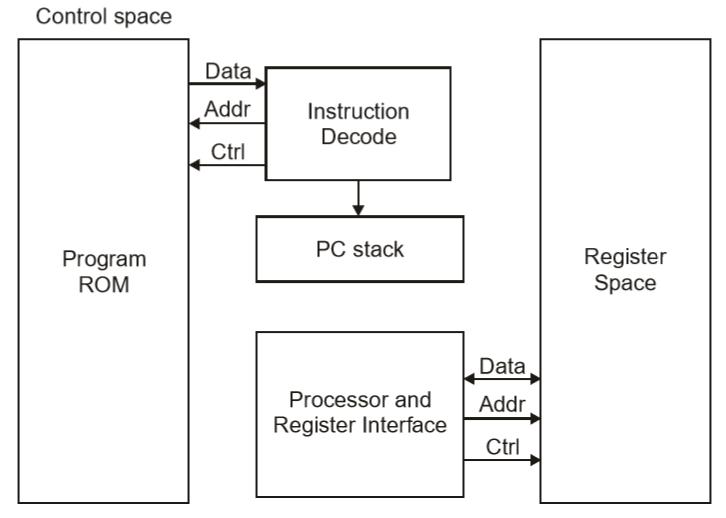

A arquitetura Von Neumann foi proposta pela primeira vez por um cientista da computação John von Neumann. Nesta arquitetura, existe um caminho ou barramento de dados para instrução e dados. Como resultado, a CPU realiza uma operação por vez. Ele busca uma instrução da memória ou executa a operação de leitura / gravação nos dados. Portanto, uma busca de instrução e uma operação de dados não podem ocorrer simultaneamente, compartilhando um barramento comum.

A arquitetura Von-Neumann suporta hardware simples. Permite o uso de uma única memória sequencial. As velocidades de processamento atuais superam em muito os tempos de acesso à memória, e empregamos uma quantidade muito rápida, mas pequena de memória (cache) local para o processador.

Arquitetura Harvard

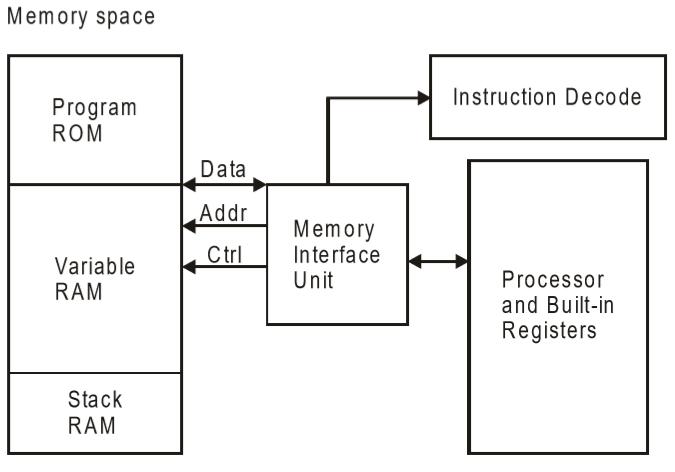

A arquitetura Harvard oferece armazenamento separado e barramentos de sinal para instruções e dados. Esta arquitetura possui armazenamento de dados inteiramente contido na CPU, e não há acesso ao armazenamento de instruções como dados. Os computadores têm áreas de memória separadas para instruções de programa e dados usando barramentos de dados internos, permitindo acesso simultâneo a instruções e dados.

Os programas precisavam ser carregados por um operador; o processador não conseguiu inicializar sozinho. Em uma arquitetura de Harvard, não há necessidade de fazer as duas memórias compartilharem propriedades.

Arquitetura Von-Neumann vs Arquitetura Harvard

Os pontos a seguir distinguem a Arquitetura de Von Neumann da Arquitetura de Harvard.

| Arquitetura Von-Neumann | Arquitetura Harvard |

|---|---|

| Memória única a ser compartilhada por código e dados. | Memórias separadas para código e dados. |

| O processador precisa buscar código em um ciclo de clock separado e dados em outro ciclo de clock. Portanto, requer dois ciclos de clock. | Um único ciclo de clock é suficiente, pois barramentos separados são usados para acessar o código e os dados. |

| Maior velocidade, portanto, menos demorado. | Mais lento em velocidade, portanto, mais demorado. |

| Design simples. | Com design complexo. |

CISC e RISC

CISC é um computador com conjunto de instruções complexas. É um computador que pode endereçar um grande número de instruções.

No início da década de 1980, os projetistas de computadores recomendaram que os computadores usassem menos instruções com construções simples para que pudessem ser executados muito mais rápido na CPU sem a necessidade de usar memória. Esses computadores são classificados como Computador de conjunto de instruções reduzido ou RISC.

CISC vs RISC

Os seguintes pontos diferenciam um CISC de um RISC -

| CISC | RISC |

|---|---|

| Conjunto maior de instruções. Fácil de programar | Conjunto menor de instruções. Difícil de programar. |

| Projeto mais simples de compilador, considerando um conjunto maior de instruções. | Projeto complexo de compilador. |

| Muitos modos de endereçamento causando formatos de instrução complexos. | Poucos modos de endereçamento, formato de instrução fixo. |

| O comprimento da instrução é variável. | A duração da instrução varia. |

| Ciclos de clock mais altos por segundo. | Ciclo de clock baixo por segundo. |

| A ênfase está no hardware. | A ênfase está no software. |

| A unidade de controle implementa um grande conjunto de instruções usando a unidade de micro-programa. | Cada instrução deve ser executada por hardware. |

| Execução mais lenta, pois as instruções devem ser lidas da memória e decodificadas pela unidade decodificadora. | Execução mais rápida, pois cada instrução deve ser executada por hardware. |

| O pipelining não é possível. | O pipelining de instruções é possível, considerando um único ciclo de clock. |