Circuitos de pulso - gerador de varredura Miller

O circuito gerador de base de tempo de transistor Miller é o popular Miller integratorcircuito que produz uma forma de onda de varredura. Isso é usado principalmente em circuitos de deflexão horizontal.

Vamos tentar entender a construção e o funcionamento de um circuito gerador de base de tempo de Miller.

Construção do gerador de varredura Miller

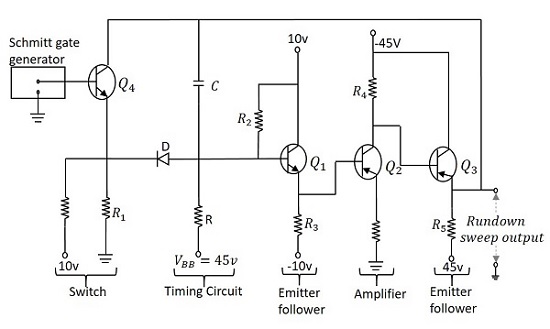

O circuito gerador da base de tempo Miller consiste em uma chave e um circuito de temporização no estágio inicial, cuja entrada é obtida do circuito gerador da porta de Schmitt. A seção do amplificador é a seguinte, que possui três estágios, sendo o primeiro umemitter follower, segundo um amplifier e o terceiro também é um emitter follower.

Um circuito seguidor de emissor geralmente atua como um Buffer amplifier. Tem umlow output impedance e um high input impedance. A baixa impedância de saída permite que o circuito acione uma carga pesada. A alta impedância de entrada evita que o circuito não carregue seu circuito anterior. A última seção do seguidor do emissor não carregará a seção anterior do amplificador. Por causa disso, o ganho do amplificador será alto.

O capacitor C colocado entre a base de Q 1 e o emissor de Q 3 é o capacitor temporizador. Os valores de R e C e a variação do nível de tensão de V BB altera a velocidade de varredura. A figura abaixo mostra o circuito de um gerador de base de tempo Miller.

Operação do gerador de varredura Miller

Quando a saída do gerador de gatilho Schmitt é um pulso negativo, o transistor Q 4 liga e a corrente do emissor flui através de R 1 . O emissor está em potencial negativo e o mesmo é aplicado no cátodo do diodo D, o que o torna polarizado direto. Como o capacitor C é desviado aqui, ele não é carregado.

A aplicação de um pulso de disparo torna a saída da porta Schmitt alta, que por sua vez, desliga o transistor Q 4 . Agora, uma voltagem de 10 V é aplicada no emissor de Q 4 que faz a corrente fluir através de R 1, o que também torna o diodo D polarizado reversamente. Como o transistor Q 4 está em corte, o capacitor C é carregado de V BB a R e fornece uma saída de varredura reduzida no emissor de Q 3 . O capacitor C descarrega através de D e do transistor Q 4 no final da varredura.

Considerando o efeito da capacitância C 1 , a velocidade de inclinação ou erro de velocidade de varredura é dado por

$$ e_s = \ frac {V_s} {V} \ left (1- A + \ frac {R} {R_i} + \ frac {C} {C_i} \ right) $$

Formulários

Os circuitos de varredura Miller são os circuitos integradores mais comumente usados em muitos dispositivos. É um gerador de dentes de serra amplamente utilizado.