Встроенные системы - Типы архитектуры

Микроконтроллеры 8051 работают с 8-битной шиной данных. Таким образом, они могут поддерживать внешнюю память данных до 64 КБ и внешнюю память программ до 64 КБ в лучшем случае. В совокупности микроконтроллеры 8051 могут адресовать 128 КБ внешней памяти.

Когда данные и код находятся в разных блоках памяти, тогда архитектура называется Harvard architecture. В случае, если данные и код находятся в одном блоке памяти, тогда архитектура называетсяVon Neumann architecture.

Архитектура фон Неймана

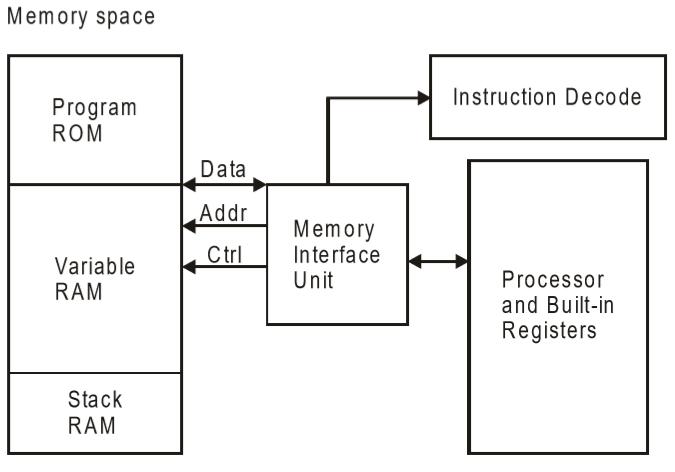

Архитектура фон Неймана была впервые предложена компьютерным ученым Джоном фон Нейманом. В этой архитектуре существует один путь или шина данных как для инструкции, так и для данных. В результате ЦП выполняет одну операцию за раз. Он либо извлекает инструкцию из памяти, либо выполняет операцию чтения / записи данных. Таким образом, выборка команды и операция с данными не могут происходить одновременно, имея общую шину.

Архитектура фон Неймана поддерживает простое оборудование. Это позволяет использовать одну последовательную память. Сегодняшняя скорость обработки значительно превышает время доступа к памяти, и мы используем очень быстрый, но небольшой объем памяти (кеша), локальный для процессора.

Гарвардская Архитектура

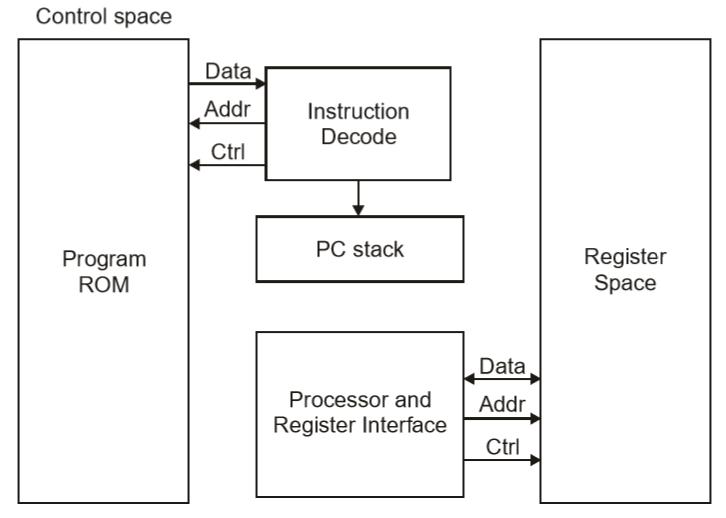

Гарвардская архитектура предлагает отдельные шины хранения и сигналов для инструкций и данных. Эта архитектура имеет хранилище данных, полностью содержащееся в ЦП, и нет доступа к хранилищу инструкций как к данным. Компьютеры имеют отдельные области памяти для программных инструкций и данных, использующих внутренние шины данных, что обеспечивает одновременный доступ как к инструкциям, так и к данным.

Программы должны быть загружены оператором; процессор не может загрузиться сам. В гарвардской архитектуре нет необходимости заставлять два воспоминания разделять свойства.

Архитектура фон Неймана против архитектуры Гарварда

Следующие пункты отличают архитектуру фон Неймана от архитектуры Гарварда.

| Архитектура фон Неймана | Гарвардская Архитектура |

|---|---|

| Единая память должна использоваться как кодом, так и данными. | Отдельная память для кода и данных. |

| Процессору необходимо получить код в отдельном тактовом цикле и данные в другом тактовом цикле. Таким образом, требуется два тактовых цикла. | Одного такта достаточно, поскольку для доступа к коду и данным используются отдельные шины. |

| Более высокая скорость, поэтому меньше времени. | Медленнее по скорости, поэтому требуется больше времени. |

| Простая конструкция. | Сложный по дизайну. |

CISC и RISC

CISC - это компьютер со сложным набором команд. Это компьютер, который может обрабатывать большое количество инструкций.

В начале 1980-х годов разработчики компьютеров рекомендовали компьютерам использовать меньше инструкций с простыми конструкциями, чтобы их можно было выполнять намного быстрее в ЦП без необходимости использования памяти. Такие компьютеры классифицируются как компьютеры с сокращенным набором команд или RISC.

CISC против RISC

Следующие пункты отличают CISC от RISC:

| CISC | RISC |

|---|---|

| Большой набор инструкций. Легко программировать | Меньший набор инструкций. Сложно программировать. |

| Более простой дизайн компилятора с учетом большего набора инструкций. | Комплексный дизайн компилятора. |

| Многие режимы адресации вызывают сложные форматы команд. | Мало режимов адресации, исправлен формат инструкции. |

| Длина инструкции переменная. | Длина инструкций варьируется. |

| Более высокие тактовые циклы в секунду. | Низкий тактовый цикл в секунду. |

| Упор делается на оборудование. | Упор делается на программное обеспечение. |

| Блок управления реализует большой набор команд с помощью микропрограммного блока. | Каждая инструкция должна выполняться аппаратно. |

| Более медленное выполнение, поскольку инструкции должны считываться из памяти и декодироваться блоком декодера. | Более быстрое выполнение, поскольку каждая инструкция должна выполняться аппаратно. |

| Конвейерная обработка невозможна. | Конвейерная обработка инструкций возможна с учетом одного такта. |