Микропроцессор - конфигурация контактов 8086

8086 был первым 16-битным микропроцессором, доступным в 40-контактном чипе DIP (Dual Inline Package). Давайте теперь подробно обсудим конфигурацию выводов микропроцессора 8086.

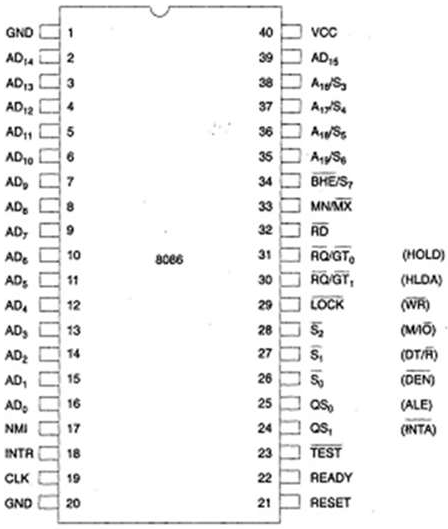

Схема контактов 8086

Вот схема контактов микропроцессора 8086 -

Давайте теперь обсудим сигналы подробно -

Power supply and frequency signals

Он использует питание 5 В постоянного тока на контакте 40 V CC и заземление на контактах 1 и 20 V SS для своей работы.

Clock signal

Тактовый сигнал подается через контакт 19. Он обеспечивает синхронизацию операций с процессором. Его частота разная для разных версий, т.е. 5 МГц, 8 МГц и 10 МГц.

Address/data bus

AD0-AD15. Это 16 шин адреса / данных. AD0-AD7 передает байтовые данные младшего разряда, а AD8AD15 - байтовые данные более высокого порядка. В течение первого тактового цикла он передает 16-битный адрес, а после этого - 16-битные данные.

Address/status bus

A16-A19 / S3-S6. Это 4 шины адреса / состояния. В течение первого такта он передает 4-битный адрес, а затем передает сигналы состояния.

S7/BHE

BHE расшифровывается как Bus High Enable. Он доступен на выводе 34 и используется для индикации передачи данных по шине данных D8-D15. Этот сигнал низкий в течение первого тактового цикла, после чего он активен.

Read($\overline{RD}$)

Он доступен на выводе 32 и используется для считывания сигнала операции чтения.

Ready

Он доступен на выводе 22. Это сигнал подтверждения от устройств ввода-вывода о передаче данных. Это активный высокий сигнал. Высокий уровень означает, что устройство готово к передаче данных. Когда он низкий, это указывает на состояние ожидания.

RESET

Он доступен на выводе 21 и используется для перезапуска выполнения. Это заставляет процессор немедленно прекратить свою текущую деятельность. Этот сигнал активен на высоком уровне в течение первых 4 тактовых циклов для СБРОСА микропроцессора.

INTR

Он доступен на выводе 18. Это сигнал запроса прерывания, который дискретизируется в течение последнего тактового цикла каждой инструкции, чтобы определить, считает ли процессор это прерыванием или нет.

NMI

Он означает немаскируемое прерывание и доступен на выводе 17. Это вход, запускаемый по фронту, который вызывает запрос прерывания на микропроцессор.

$ \ overline {ТЕСТ} $

Этот сигнал похож на состояние ожидания и доступен на выводе 23. Когда этот сигнал высокий, процессор должен ждать состояния IDLE, иначе выполнение продолжается.

MN/$\overline{MX}$

Он обозначает минимум / максимум и доступен на выводе 33. Он указывает, в каком режиме должен работать процессор; при высоком он работает в режиме минимума и наоборот.

INTA

Это сигнал подтверждения прерывания и идентификатор, доступный на выводе 24. Когда микропроцессор получает этот сигнал, он подтверждает прерывание.

ALE

Он обозначает защелку разрешения адреса и доступен на выводе 25. Положительный импульс генерируется каждый раз, когда процессор начинает любую операцию. Этот сигнал указывает на наличие действительного адреса в строках адреса / данных.

DEN

Он означает включение данных и доступен на выводе 26. Он используется для включения приемопередатчика 8286. Приемопередатчик - это устройство, используемое для отделения данных от шины адреса / данных.

DT/R

Он обозначает сигнал передачи / приема данных и доступен на выводе 27. Он определяет направление потока данных через приемопередатчик. Когда он высокий, данные передаются и наоборот.

M/IO

Этот сигнал используется для различения операций памяти и ввода-вывода. Когда он высокий, это указывает на операцию ввода / вывода, а когда он низкий - на операцию с памятью. Он доступен на контакте 28.

WR

Он обозначает сигнал записи и доступен на выводе 29. Он используется для записи данных в память или устройство вывода в зависимости от состояния сигнала M / IO.

HLDA

Он означает сигнал подтверждения удержания и доступен на выводе 30. Этот сигнал подтверждает сигнал удержания.

HOLD

Этот сигнал указывает процессору, что внешние устройства запрашивают доступ к шинам адреса / данных. Он доступен на контакте 31.

QS1 and QS0

Это сигналы состояния очереди, которые доступны на выводах 24 и 25. Эти сигналы предоставляют состояние очереди команд. Их условия показаны в следующей таблице -

| QS 0 | QS 1 | Положение дел |

|---|---|---|

| 0 | 0 | Нет операции |

| 0 | 1 | Первый байт кода операции из очереди |

| 1 | 0 | Очистить очередь |

| 1 | 1 | Последующий байт из очереди |

S0, S1, S2

Это сигналы состояния, которые обеспечивают состояние работы, которое используется контроллером шины 8288 для генерации сигналов управления памятью и вводом / выводом. Они доступны на выводах 26, 27 и 28. Ниже приводится таблица, показывающая их статус:

| S 2 | S 1 | S 0 | Положение дел |

|---|---|---|---|

| 0 | 0 | 0 | Подтверждение прерывания |

| 0 | 0 | 1 | I / O чтение |

| 0 | 1 | 0 | I / O Запись |

| 0 | 1 | 1 | Остановка |

| 1 | 0 | 0 | Получение кода операции |

| 1 | 0 | 1 | Чтение из памяти |

| 1 | 1 | 0 | Запись в память |

| 1 | 1 | 1 | Пассивный |

LOCK

Когда этот сигнал активен, он указывает другим процессорам, чтобы они не просили ЦП покинуть системную шину. Он активируется с помощью префикса LOCK для любой инструкции и доступен на выводе 29.

RQ/GT1 and RQ/GT0

Это сигналы запроса / предоставления, используемые другими процессорами, запрашивающими ЦП освободить системную шину. Когда сигнал получен ЦП, он отправляет подтверждение. RQ / GT 0 имеет более высокий приоритет, чем RQ / GT 1 .