वीएलएसआई डिज़ाइन - अनुक्रमिक एमओएस लॉजिक सर्किट

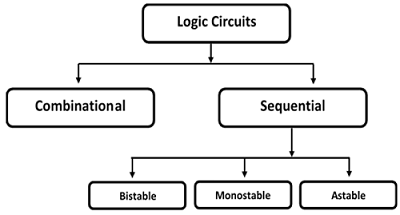

लॉजिक सर्किट को दो श्रेणियों में बांटा गया है - (ए) कॉम्बिनेशन सर्किट, और (बी) सीक्वेंशियल सर्किट।

संयोजन सर्किट में, आउटपुट केवल नवीनतम इनपुट की स्थिति पर निर्भर करता है।

अनुक्रमिक सर्किट में, आउटपुट न केवल नवीनतम इनपुट पर निर्भर करता है, बल्कि पहले के इनपुट की स्थिति पर भी निर्भर करता है। अनुक्रमिक सर्किट में स्मृति तत्व होते हैं।

अनुक्रमिक सर्किट तीन प्रकार के होते हैं -

Bistable- बिस्टेबल सर्किट में दो स्थिर परिचालन बिंदु होते हैं और दोनों राज्यों में होंगे। उदाहरण - मेमोरी सेल्स, लैचेस, फ्लिप-फ्लॉप और रजिस्टर।

Monostable- मोनोस्टेबल सर्किट में केवल एक स्थिर ऑपरेटिंग बिंदु होता है और भले ही वे अस्थायी रूप से विपरीत स्थिति के लिए परेशान हों, वे समय पर अपने स्थिर ऑपरेटिंग बिंदु पर लौट आएंगे। उदाहरण: टाइमर, नाड़ी जनरेटर।

Astable- सर्किट में कई राज्यों के बीच कोई स्थिर परिचालन बिंदु और दोलन नहीं है। उदाहरण - रिंग ऑसिलेटर।

CMOS तर्क सर्किट

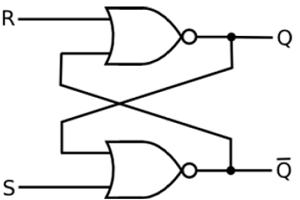

NOR गेट पर आधारित SR Latch

यदि सेट इनपुट (S) तर्क के बराबर है "1" और रीसेट इनपुट तर्क के बराबर है "0." तब आउटपुट Q को तर्क के लिए मजबूर किया जाएगा "1"। जबकि $ \ overline {Q} $ को तर्क के लिए मजबूर किया जाता है"0"। इसका मतलब यह है कि एसआर कुंडी स्थापित की जाएगी, भले ही इसकी पिछली स्थिति कैसी भी हो।

इसी तरह, यदि S "0" के बराबर है और R बराबर है "1" तो उत्पादन क्यू के लिए मजबूर किया जाएगा "0" जबकि $ \ overline {Q} $ के लिए मजबूर किया जाता है "1"। इसका मतलब यह है कि कुंडी को रीसेट किया गया है, भले ही इसकी पहले की स्थिति हो। अंत में, यदि दोनों इनपुट एस और आर तर्क के बराबर हैं"1" फिर दोनों आउटपुट को तर्क के लिए मजबूर किया जाएगा "0" जो क्यू और $ \ overline {Q} $ की संपूरकता के साथ संघर्ष करता है।

इसलिए, सामान्य ऑपरेशन के दौरान इस इनपुट संयोजन की अनुमति नहीं है। NOR आधारित SR Latch की सत्य तालिका तालिका में दी गई है।

| रों | आर | क्यू | $ \ Overline {क्यू} $ | ऑपरेशन |

|---|---|---|---|---|

| 0 | 0 | क्यू | $ \ Overline {क्यू} $ | होल्ड |

| 1 | 0 | 1 | 0 | सेट |

| 0 | 1 | 0 | 1 | रीसेट |

| 1 | 1 | 0 | 0 | अनुमति नहीं हैं |

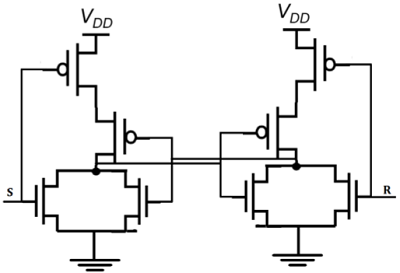

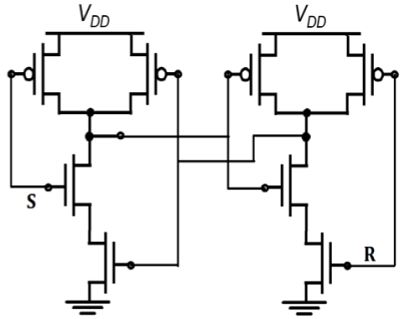

NOR फाटक पर आधारित CMOS SR कुंडी नीचे दिए गए चित्र में दिखाया गया है।

यदि S, V OH के बराबर है और R , V OL के बराबर है , तो समानांतर जुड़े ट्रांजिस्टर M1 और M2 दोनों चालू होंगे। नोड $ \ overline {Q} $ पर वोल्टेज V OL = 0 के तर्क-निम्न स्तर को मान लेगा ।

एक ही समय में, M3 और M4 दोनों को बंद कर दिया जाता है, जिसके परिणामस्वरूप नोड Q पर एक तर्क-उच्च वोल्टेज V OH होता है। यदि R, V OH के बराबर है और S , V OL , M1 और M2 के समान है। M3 और M4 चालू।

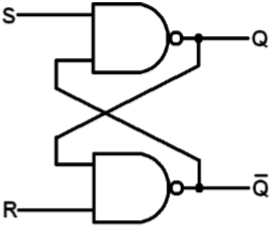

NAND गेट पर आधारित SR Latch

नंद स्थित एसआर कुंडी का ब्लॉक आरेख और गेट स्तर योजनाबद्ध चित्र में दिखाया गया है। एस और आर इनपुट टर्मिनलों पर छोटे वृत्त यह दर्शाते हैं कि सर्किट सक्रिय निम्न इनपुट संकेतों का जवाब देता है। नंद स्थित एसआर कुंडी की सच्चाई तालिका में दी गई है

| रों | आर | क्यू | क्यू ' | |

| 0 | 0 | एनसी | एनसी | कोई परिवर्तन नहीं होता है। वर्तमान स्थिति में कुंडी बनी रही। |

| 1 | 0 | 1 | 0 | लेट सेट। |

| 0 | 1 | 0 | 1 | लाकेट RESET। |

| 1 | 1 | 0 | 0 | अमान्य स्थिति। |

यदि S 0 पर जाता है (जबकि R = 1), Q उच्च जाता है, तो $ \ overline {Q} $ कम खींचता है और कुंडी प्रवेश करती है

स = 0 फिर क्यू = 1 (यदि आर = 1)

यदि R 0 पर जाता है (जबकि S = 1), Q उच्च जाता है, तो $ \ overline {Q} $ कम खींचता है और कुंडी रीसेट होती है

आर = 0 फिर क्यू = 1 (यदि एस = 1)

होल्ड स्थिति में S और R दोनों की आवश्यकता होती है। यदि S = R = 0 तो आउटपुट की अनुमति नहीं है, क्योंकि यह अनिश्चित स्थिति में परिणाम देगा। NAND गेट पर आधारित CMOS SR Latch को चित्र में दिखाया गया है।

नंद गेट पर आधारित डिप्लोडियन-लोड nMOS एसआर लैच को चित्र में दिखाया गया है। यह ऑपरेशन CMOS NAND SR कुंडी के समान है। CMOS सर्किट कार्यान्वयन में कम स्थैतिक बिजली अपव्यय और उच्च शोर मार्जिन है।

CMOS तर्क सर्किट

देखा एसआर लाच

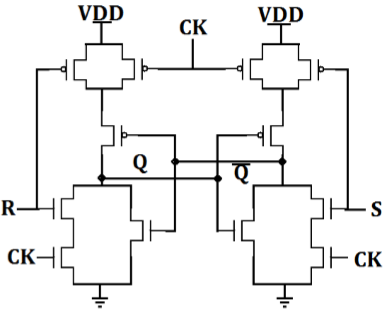

यह आंकड़ा एक एनआर-आधारित एसआर कुंडी दिखाता है जिसमें एक घड़ी जोड़ा गया है। कुंडली एस और आर इनपुट के लिए उत्तरदायी है, जब सीएलके अधिक है।

जब CLK कम होता है, तो कुंडी अपनी वर्तमान स्थिति को बनाए रखता है। निरीक्षण करें कि क्यू परिवर्तन स्थिति -

- जब सकारात्मक सीएलके के दौरान एस उच्च जाता है।

- सीएलके कम समय के दौरान एसएंडआर में बदलाव के बाद सीएलके बढ़त पर।

- एस में एक सकारात्मक गड़बड़, जबकि सीएलके अधिक है

- जब सकारात्मक सीएलके के दौरान आर उच्च जाता है।

CMOS AOI क्लॉक किए गए NOR आधारित SR कुंडी का कार्यान्वयन चित्र में दिखाया गया है। ध्यान दें कि केवल 12 ट्रांजिस्टर की आवश्यकता है।

जब सीएलके कम होता है, तो एन ट्री एन में दो श्रृंखला टर्मिनल खुले होते हैं और पेड़ पी में दो समानांतर ट्रांजिस्टर ऑन होते हैं, इस प्रकार मेमोरी सेल में स्थिति को बनाए रखते हैं।

जब घड़ी अधिक होती है, तो सर्किट बस एक NOR आधारित CMOS कुंडी बन जाता है जो इनपुट S और R पर प्रतिक्रिया देगा।

Clocked SR Latch based on NAND Gate

सर्किट चार नंद द्वारों के साथ कार्यान्वित किया जाता है। यदि यह सर्किट CMOS के साथ लागू किया जाता है तो इसके लिए 16 ट्रांजिस्टर की आवश्यकता होती है।

- यदि सीएलके अधिक है तो कुंडी S या R के लिए उत्तरदायी है।

- यदि दोनों इनपुट सिग्नल और सीएलके सिग्नल सक्रिय उच्च हैं: यानी, कुंडी आउटपुट क्यू तब सेट किया जाएगा जब सीएलके = "1" एस = "1" और आर = "0"।

- इसी तरह, CLK = "1," S = "0," और

जब CLK कम होता है, तो कुंडी अपनी वर्तमान स्थिति को बनाए रखती है।

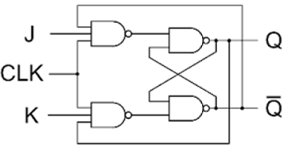

जेके कुंडी देखा

ऊपर का आंकड़ा नंद द्वार पर आधारित एक घड़ी जेके कुंडी दिखाता है। एसआर कुंडी का नुकसान यह है कि जब एस और आर दोनों उच्च होते हैं, तो इसकी उत्पादन स्थिति अनिश्चित हो जाती है। जेके कुंडी आउटपुट से इनपुट तक की प्रतिक्रिया का उपयोग करके इस समस्या को समाप्त करती है, जैसे कि सत्य तालिका के सभी इनपुट राज्य स्वीकार्य हैं। यदि J = K = 0, तो कुंडी अपनी वर्तमान स्थिति धारण करेगा।

यदि J = 1 और K = 0, तो कुंडी अगली धनात्मक-घड़ी के किनारे पर सेट हो जाएगी, अर्थात Q = 1, $ \ overline {Q} $ = 0

यदि J = 0 और K = 1, तो कुंडी अगले पॉजिटिव-क्लॉक किनारे पर रीसेट हो जाएगी, अर्थात Q = 1 और $ \ overline {Q} $ = 0।

यदि J = K = 1 है, तो अगले पॉजिटिव-क्लॉक एज पर कुंडी टॉगल होगी

तालिका में दिए गए सत्य सारणी में क्लॉक किए गए JK कुंडी के संचालन को संक्षेप में प्रस्तुत किया गया है।

J |

K |

Q |

$ \ Overline {क्यू} $ | S |

R |

Q |

$ \ Overline {क्यू} $ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | होल्ड |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | रीसेट |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | सेट |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | टॉगल |

| 1 | 0 | 1 | 0 | 0 | 1 |

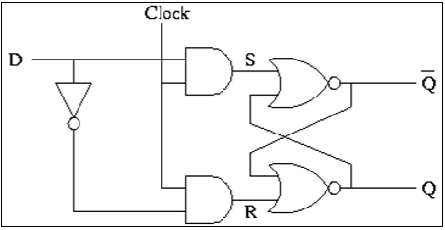

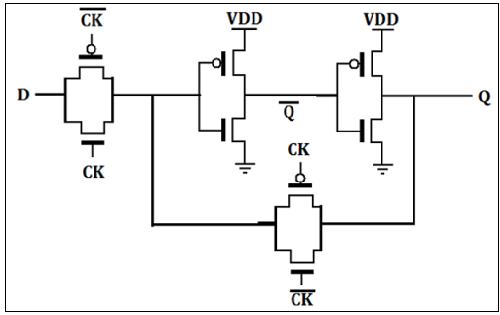

CMOS D Latch कार्यान्वयन

डी कुंडी सामान्य रूप से, ट्रांसमिशन गेट (टीजी) स्विच के साथ लागू की जाती है जैसा कि आंकड़े में दिखाया गया है। इनपुट टीजी सीएलके के साथ सक्रिय होता है जबकि कुंडी प्रतिक्रिया पाश टीजी सीएलके के साथ सक्रिय होता है। सीएलके अधिक होने पर इनपुट डी स्वीकार किया जाता है। जब सीएलके कम हो जाता है, तो इनपुट opencircuited है और कुंडी पूर्व डेटा डी के साथ सेट है।