Sistemi integrati - Tipi di architettura

I microcontrollori 8051 funzionano con bus dati a 8 bit. Quindi possono supportare una memoria dati esterna fino a 64K e una memoria di programma esterna di 64k al massimo. Collettivamente, 8051 microcontrollori possono indirizzare 128k di memoria esterna.

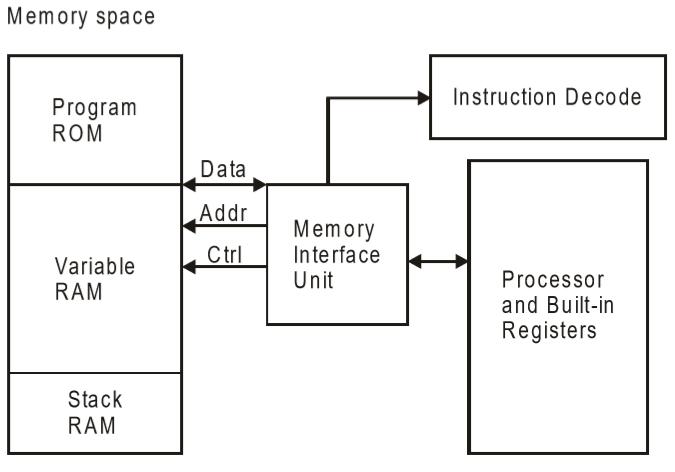

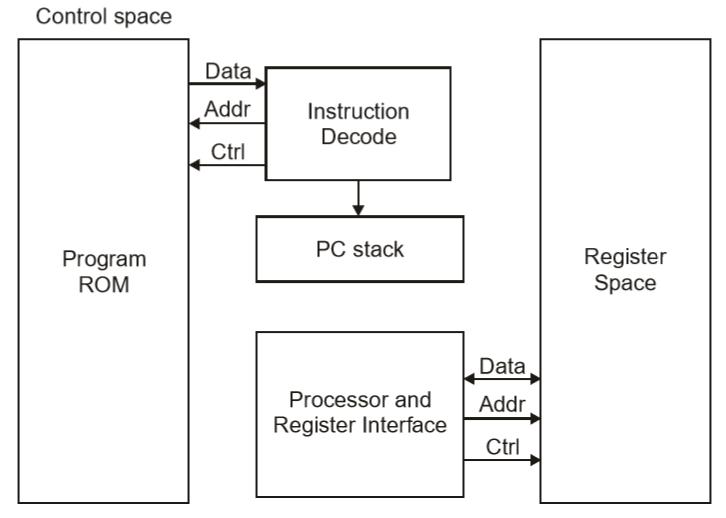

Quando dati e codice si trovano in blocchi di memoria diversi, l'architettura viene indicata come Harvard architecture. Nel caso in cui dati e codice si trovino nello stesso blocco di memoria, si fa riferimento all'architettura comeVon Neumann architecture.

Von Neumann Architecture

L'architettura Von Neumann è stata proposta per la prima volta da uno scienziato informatico John von Neumann. In questa architettura, esiste un percorso dati o un bus sia per l'istruzione che per i dati. Di conseguenza, la CPU esegue un'operazione alla volta. Recupera un'istruzione dalla memoria o esegue operazioni di lettura / scrittura sui dati. Quindi un'istruzione fetch e un'operazione sui dati non possono avvenire simultaneamente, condividendo un bus comune.

L'architettura Von-Neumann supporta hardware semplice. Consente l'utilizzo di un'unica memoria sequenziale. Le velocità di elaborazione odierne superano di gran lunga i tempi di accesso alla memoria e utilizziamo una quantità di memoria (cache) molto veloce ma ridotta locale al processore.

Architettura di Harvard

L'architettura di Harvard offre memoria separata e bus di segnale per istruzioni e dati. Questa architettura ha l'archiviazione dei dati interamente contenuta all'interno della CPU e non è possibile accedere all'archiviazione delle istruzioni come dati. I computer hanno aree di memoria separate per istruzioni di programma e dati che utilizzano bus dati interni, consentendo l'accesso simultaneo sia alle istruzioni che ai dati.

I programmi dovevano essere caricati da un operatore; il processore non è riuscito ad avviarsi da solo. In un'architettura di Harvard, non è necessario che i due ricordi condividano le proprietà.

Von-Neumann Architecture vs Harvard Architecture

I seguenti punti distinguono l'architettura Von Neumann dall'architettura di Harvard.

| Architettura Von-Neumann | Architettura di Harvard |

|---|---|

| Memoria unica da condividere sia dal codice che dai dati. | Memorie separate per codice e dati. |

| Il processore deve recuperare il codice in un ciclo di clock separato e i dati in un altro ciclo di clock. Quindi richiede due cicli di clock. | Un singolo ciclo di clock è sufficiente, poiché vengono utilizzati bus separati per accedere al codice e ai dati. |

| Maggiore velocità, quindi meno tempo. | Più lento nella velocità, quindi più dispendioso in termini di tempo. |

| Semplice nel design. | Complesso nel design. |

CISC e RISC

CISC è un computer con set di istruzioni complesso. È un computer che può indirizzare un gran numero di istruzioni.

All'inizio degli anni '80, i progettisti di computer raccomandavano che i computer usassero meno istruzioni con costrutti semplici in modo che possano essere eseguite molto più velocemente all'interno della CPU senza dover utilizzare la memoria. Tali computer sono classificati come computer con set di istruzioni ridotto o RISC.

CISC vs RISC

I seguenti punti differenziano un CISC da un RISC:

| CISC | RISC |

|---|---|

| Set di istruzioni più ampio. Facile da programmare | Set di istruzioni più piccolo. Difficile da programmare. |

| Progettazione più semplice del compilatore, considerando un set di istruzioni più ampio. | Progettazione complessa del compilatore. |

| Molte modalità di indirizzamento che causano formati di istruzioni complessi. | Poche modalità di indirizzamento, correzione del formato delle istruzioni. |

| La lunghezza delle istruzioni è variabile. | La lunghezza delle istruzioni varia. |

| Cicli di clock più elevati al secondo. | Basso ciclo di clock al secondo. |

| L'enfasi è sull'hardware. | L'enfasi è sul software. |

| L'unità di controllo implementa un ampio set di istruzioni utilizzando un'unità di microprogrammi. | Ogni istruzione deve essere eseguita dall'hardware. |

| Esecuzione più lenta, poiché le istruzioni devono essere lette dalla memoria e decodificate dall'unità di decodifica. | Esecuzione più rapida, poiché ogni istruzione deve essere eseguita dall'hardware. |

| Il pipelining non è possibile. | È possibile il pipelining delle istruzioni, considerando un singolo ciclo di clock. |