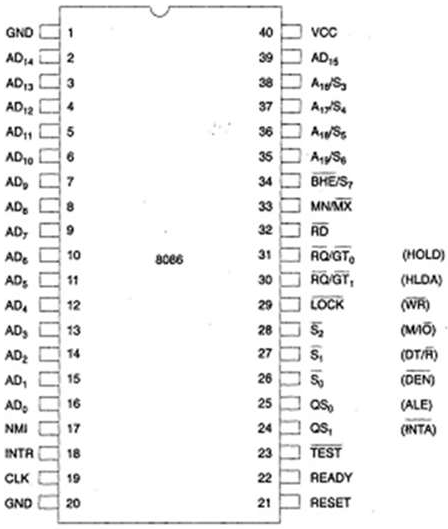

Microprocessore - Configurazione 8086 Pin

8086 è stato il primo microprocessore a 16 bit disponibile nel chip DIP (Dual Inline Package) a 40 pin. Discutiamo ora in dettaglio la configurazione dei pin di un microprocessore 8086.

Schema pin 8086

Ecco il diagramma dei pin del microprocessore 8086 -

Discutiamo ora i segnali in dettaglio:

Power supply and frequency signals

Utilizza un'alimentazione a 5 V CC a V CC pin 40 e utilizza la massa a V SS pin 1 e 20 per il suo funzionamento.

Clock signal

Il segnale di clock è fornito tramite il Pin-19. Fornisce i tempi al processore per le operazioni. La sua frequenza è diversa per le diverse versioni, cioè 5 MHz, 8 MHz e 10 MHz.

Address/data bus

AD0-AD15. Questi sono 16 indirizzi / bus dati. AD0-AD7 trasporta dati di byte di ordine inferiore e AD8AD15 trasporta dati di byte di ordine superiore. Durante il primo ciclo di clock, trasporta indirizzi a 16 bit e successivamente trasporta dati a 16 bit.

Address/status bus

A16-A19 / S3-S6. Questi sono i 4 bus indirizzo / stato. Durante il primo ciclo di clock, trasporta indirizzi a 4 bit e successivamente trasporta segnali di stato.

S7/BHE

BHE sta per Bus High Enable. È disponibile al pin 34 e utilizzato per indicare il trasferimento dei dati utilizzando il bus dati D8-D15. Questo segnale è basso durante il primo ciclo di clock, dopodiché è attivo.

Read($\overline{RD}$)

È disponibile al pin 32 e viene utilizzato per leggere il segnale per l'operazione di lettura.

Ready

È disponibile al pin 22. È un segnale di riconoscimento dai dispositivi I / O che i dati vengono trasferiti. È un segnale alto attivo. Quando è alto, indica che il dispositivo è pronto per il trasferimento dei dati. Quando è basso, indica lo stato di attesa.

RESET

È disponibile al pin 21 e serve per riavviare l'esecuzione. Fa sì che il processore interrompa immediatamente la sua attività attuale. Questo segnale è attivo alto per i primi 4 cicli di clock per RESETTARE il microprocessore.

INTR

È disponibile al pin 18. È un segnale di richiesta di interruzione, che viene campionato durante l'ultimo ciclo di clock di ciascuna istruzione per determinare se il processore lo considera come un interrupt oppure no.

NMI

È l'acronimo di interrupt non mascherabile ed è disponibile al pin 17. È un ingresso triggerato dal fronte, che provoca una richiesta di interrupt al microprocessore.

$ \ overline {TEST} $

Questo segnale è come lo stato di attesa ed è disponibile al pin 23. Quando questo segnale è alto, il processore deve attendere lo stato IDLE, altrimenti l'esecuzione continua.

MN/$\overline{MX}$

Sta per Minimo / Massimo ed è disponibile al pin 33. Indica in quale modalità deve operare il processore; quando è alto funziona in modalità minima e viceversa.

INTA

È un segnale di riconoscimento dell'interruzione e ID disponibile al pin 24. Quando il microprocessore riceve questo segnale, riconosce l'interruzione.

ALE

È l'acronimo di address enable latch ed è disponibile al pin 25. Un impulso positivo viene generato ogni volta che il processore inizia qualsiasi operazione. Questo segnale indica la disponibilità di un indirizzo valido sulle linee indirizzo / dati.

DEN

Sta per Data Enable ed è disponibile al pin 26. Viene utilizzato per abilitare il Transreceiver 8286. Il transreceiver è un dispositivo utilizzato per separare i dati dall'indirizzo / bus dati.

DT/R

È l'acronimo di Data Transmit / Receive signal ed è disponibile al pin 27. Decide la direzione del flusso di dati attraverso il ricetrasmettitore. Quando è alto, i dati vengono trasmessi e viceversa.

M/IO

Questo segnale viene utilizzato per distinguere tra memoria e operazioni di I / O. Quando è alto, indica l'operazione di I / O e quando è basso indica l'operazione di memoria. È disponibile al pin 28.

WR

Sta per segnale di scrittura ed è disponibile al pin 29. Viene utilizzato per scrivere i dati nella memoria o nel dispositivo di uscita a seconda dello stato del segnale M / IO.

HLDA

Sta per segnale di conferma di attesa ed è disponibile al pin 30. Questo segnale riconosce il segnale di attesa.

HOLD

Questo segnale indica al processore che i dispositivi esterni richiedono di accedere ai bus di indirizzo / dati. È disponibile al pin 31.

QS1 and QS0

Questi sono segnali di stato della coda e sono disponibili ai pin 24 e 25. Questi segnali forniscono lo stato della coda di istruzioni. Le loro condizioni sono riportate nella tabella seguente:

| QS 0 | QS 1 | Stato |

|---|---|---|

| 0 | 0 | Nessuna operazione |

| 0 | 1 | Primo byte di codice operativo dalla coda |

| 1 | 0 | Svuota la coda |

| 1 | 1 | Byte successivo dalla coda |

S0, S1, S2

Questi sono i segnali di stato che forniscono lo stato di funzionamento, che viene utilizzato dal controller bus 8288 per generare segnali di controllo I / O e memoria. Questi sono disponibili ai pin 26, 27 e 28. Di seguito è riportata la tabella che mostra il loro stato:

| S 2 | S 1 | S 0 | Stato |

|---|---|---|---|

| 0 | 0 | 0 | Riconoscimento dell'interruzione |

| 0 | 0 | 1 | Lettura I / O |

| 0 | 1 | 0 | Scrittura I / O |

| 0 | 1 | 1 | Ferma |

| 1 | 0 | 0 | Recupero codice operativo |

| 1 | 0 | 1 | Lettura della memoria |

| 1 | 1 | 0 | Scrittura in memoria |

| 1 | 1 | 1 | Passivo |

LOCK

Quando questo segnale è attivo, indica agli altri processori di non chiedere alla CPU di lasciare il bus di sistema. Si attiva utilizzando il prefisso LOCK su qualsiasi istruzione ed è disponibile al pin 29.

RQ/GT1 and RQ/GT0

Questi sono i segnali di richiesta / concessione utilizzati dagli altri processori che richiedono alla CPU di rilasciare il bus di sistema. Quando il segnale viene ricevuto dalla CPU, invia il riconoscimento. RQ / GT 0 ha una priorità maggiore di RQ / GT 1 .