Microprocessore - Guida rapida

Il microprocessore è un'unità di controllo di un microcomputer, fabbricato su un piccolo chip in grado di eseguire operazioni ALU (Arithmetic Logical Unit) e di comunicare con gli altri dispositivi ad esso collegati.

Il microprocessore è costituito da un ALU, un array di registri e un'unità di controllo. ALU esegue operazioni aritmetiche e logiche sui dati ricevuti dalla memoria o da un dispositivo di input. L'array dei registri è costituito da registri identificati da lettere come B, C, D, E, H, L e accumulatore. L'unità di controllo controlla il flusso di dati e istruzioni all'interno del computer.

Schema a blocchi di un microcomputer di base

Come funziona un microprocessore?

Il microprocessore segue una sequenza: Fetch, Decode e quindi Execute.

Inizialmente, le istruzioni vengono archiviate nella memoria in ordine sequenziale. Il microprocessore preleva quelle istruzioni dalla memoria, quindi le decodifica ed esegue quelle istruzioni fino a raggiungere l'istruzione STOP. Successivamente, invia il risultato in formato binario alla porta di output. Tra questi processi, il registro memorizza temporaneamente i dati e ALU esegue le funzioni di calcolo.

Elenco dei termini utilizzati in un microprocessore

Di seguito è riportato un elenco di alcuni dei termini utilizzati di frequente in un microprocessore:

Instruction Set - È l'insieme di istruzioni che il microprocessore può capire.

Bandwidth - È il numero di bit elaborati in una singola istruzione.

Clock Speed- Determina il numero di operazioni al secondo che il processore può eseguire. È espresso in megahertz (MHz) o gigahertz (GHz). È anche noto come Clock Rate.

Word Length- Dipende dalla larghezza del bus dati interno, registri, ALU, ecc. Un microprocessore a 8 bit può elaborare dati a 8 bit alla volta. La lunghezza della parola varia da 4 bit a 64 bit a seconda del tipo di microcomputer.

Data Types - Il microprocessore ha più formati di tipi di dati come binari, BCD, ASCII, numeri con e senza segno.

Caratteristiche di un microprocessore

Di seguito è riportato un elenco di alcune delle caratteristiche più importanti di qualsiasi microprocessore:

Cost-effective - I chip del microprocessore sono disponibili a prezzi bassi e ne risultano un costo contenuto.

Size - Il microprocessore è di piccole dimensioni, quindi è portatile.

Low Power Consumption - I microprocessori sono prodotti utilizzando la tecnologia dei semiconduttori di metaloossido, che ha un basso consumo energetico.

Versatility - I microprocessori sono versatili in quanto possiamo utilizzare lo stesso chip in una serie di applicazioni configurando il programma software.

Reliability - Il tasso di guasto di un circuito integrato nei microprocessori è molto basso, quindi è affidabile.

Un microprocessore può essere classificato in tre categorie:

Processore RISC

RISC sta per Reduced Instruction Set Computer. È progettato per ridurre il tempo di esecuzione semplificando il set di istruzioni del computer. Utilizzando i processori RISC, ciascuna istruzione richiede un solo ciclo di clock per eseguire i risultati in un tempo di esecuzione uniforme. Ciò riduce l'efficienza poiché ci sono più righe di codice, quindi è necessaria più RAM per memorizzare le istruzioni. Il compilatore deve anche lavorare di più per convertire le istruzioni del linguaggio di alto livello in codice macchina.

Alcuni dei processori RISC sono:

- Power PC: 601, 604, 615, 620

- DEC Alpha: 210642, 211066, 21068, 21164

- MIPS: processore RISC TS (R10000)

- PA-RISC: HP 7100LC

Architettura di RISC

L'architettura del microprocessore RISC utilizza un set di istruzioni altamente ottimizzato. Viene utilizzato in dispositivi portatili come Apple iPod grazie alla sua efficienza energetica.

Caratteristiche del RISC

Le caratteristiche principali di un processore RISC sono le seguenti:

Consiste in semplici istruzioni.

Supporta vari formati di tipi di dati.

Utilizza semplici modalità di indirizzamento e istruzioni a lunghezza fissa per il pipelining.

Supporta il registro da utilizzare in qualsiasi contesto.

Un tempo di esecuzione del ciclo.

Le istruzioni "LOAD" e "STORE" vengono utilizzate per accedere alla posizione di memoria.

Consiste in un numero maggiore di registri.

Consiste in un numero inferiore di transistor.

Processore CISC

CISC sta per Complex Instruction Set Computer. È progettato per ridurre al minimo il numero di istruzioni per programma, ignorando il numero di cicli per istruzione. L'enfasi è sulla creazione di istruzioni complesse direttamente nell'hardware.

Il compilatore deve fare pochissimo lavoro per tradurre un linguaggio di alto livello in linguaggio di livello assembly / codice macchina perché la lunghezza del codice è relativamente breve, quindi è richiesta pochissima RAM per memorizzare le istruzioni.

Alcuni dei processori CISC sono:

- IBM 370/168

- VAX 11/780

- Intel 80486

Architettura del CISC

La sua architettura è progettata per ridurre il costo della memoria poiché è necessaria una maggiore capacità di archiviazione in programmi più grandi, con conseguente aumento dei costi di memoria. Per risolvere questo problema, il numero di istruzioni per programma può essere ridotto incorporando il numero di operazioni in una singola istruzione.

Caratteristiche del CISC

- Varietà di modalità di indirizzamento.

- Maggior numero di istruzioni.

- Lunghezza variabile dei formati di istruzione.

- Potrebbero essere necessari diversi cicli per eseguire un'istruzione.

- La logica di decodifica delle istruzioni è complessa.

- È necessaria un'istruzione per supportare più modalità di indirizzamento.

Processori speciali

Questi sono i processori progettati per scopi speciali. Vengono discussi brevemente alcuni processori speciali:

Coprocessore

Un coprocessore è un microprocessore appositamente progettato, che può gestire la sua particolare funzione molte volte più velocemente del normale microprocessore.

For example - Coprocessore matematico.

Alcuni coprocessori matematici Intel sono:

- 8087-utilizzato con 8086

- 80287-utilizzato con 80286

- 80387-utilizzato con 80386

Processore di input / output

È un microprocessore appositamente progettato con una propria memoria locale, che viene utilizzata per controllare i dispositivi I / O con il minimo coinvolgimento della CPU.

For example -

- Controller DMA (accesso diretto alla memoria)

- Controller tastiera / mouse

- Controller grafico del display

- Controller della porta SCSI

Transputer (computer a transistor)

Un transputer è un microprocessore appositamente progettato con una propria memoria locale e con collegamenti per collegare un transputer a un altro transputer per comunicazioni tra processori. È stato progettato per la prima volta nel 1980 da Inmos ed è destinato all'utilizzo della tecnologia VLSI.

Un transputer può essere utilizzato come sistema a processore singolo o può essere collegato a collegamenti esterni, il che riduce i costi di costruzione e aumenta le prestazioni.

For example - Processori T212 a 16 bit, T425 a 32 bit, a virgola mobile (T800, T805 e T9000).

DSP (processore del segnale digitale)

Questo processore è appositamente progettato per elaborare i segnali analogici in una forma digitale. Questo viene fatto campionando il livello di tensione a intervalli di tempo regolari e convertendo la tensione in quell'istante in una forma digitale. Questo processo viene eseguito da un circuito chiamato convertitore da analogico a digitale, convertitore da A a D o ADC.

Un DSP contiene i seguenti componenti:

Program Memory - Memorizza i programmi che DSP utilizzerà per elaborare i dati.

Data Memory - Memorizza le informazioni da elaborare.

Compute Engine - Esegue l'elaborazione matematica, accedendo al programma dalla memoria del programma e ai dati dalla memoria dati.

Input/Output - Si collega al mondo esterno.

Le sue applicazioni sono:

- Sintesi sonora e musicale

- Compressione audio e video

- Elaborazione del segnale video

- Accelerazione grafica 2D e 3D.

For example - Serie TMS 320 di Texas Instrument, ad esempio TMS 320C40, TMS320C50.

8085 è pronunciato come microprocessore "ottantottantacinque". È un microprocessore a 8 bit progettato da Intel nel 1977 utilizzando la tecnologia NMOS.

Ha la seguente configurazione:

- Bus dati a 8 bit

- Bus indirizzi a 16 bit, che può indirizzare fino a 64 KB

- Un contatore di programma a 16 bit

- Un puntatore allo stack a 16 bit

- Sei registri a 8 bit disposti a coppie: BC, DE, HL

- Richiede un'alimentazione di + 5V per funzionare a un clock monofase di 3,2 MHZ

Viene utilizzato in lavatrici, forni a microonde, telefoni cellulari, ecc.

8085 Microprocessore - Unità funzionali

8085 è costituito dalle seguenti unità funzionali:

Accumulatore

È un registro a 8 bit utilizzato per eseguire operazioni aritmetiche, logiche, I / O e LOAD / STORE. È collegato al bus dati interno e ALU.

Unità aritmetica e logica

Come suggerisce il nome, esegue operazioni aritmetiche e logiche come addizione, sottrazione, AND, OR, ecc. Su dati a 8 bit.

Registro di uso generale

Ci sono 6 registri per uso generico nel processore 8085, cioè B, C, D, E, H e L. Ciascun registro può contenere dati a 8 bit.

Questi registri possono funzionare in coppia per contenere dati a 16 bit e la loro combinazione di accoppiamento è come BC, DE e HL.

Contatore di programma

È un registro a 16 bit utilizzato per memorizzare la posizione dell'indirizzo di memoria dell'istruzione successiva da eseguire. Il microprocessore incrementa il programma ogni volta che viene eseguita un'istruzione, in modo che il contatore del programma punti all'indirizzo di memoria dell'istruzione successiva che verrà eseguita.

Puntatore dello stack

È anche un registro a 16 bit che funziona come uno stack, che viene sempre incrementato / decrementato di 2 durante le operazioni push & pop.

Registro temporaneo

È un registro a 8 bit, che contiene i dati temporanei delle operazioni aritmetiche e logiche.

Registro delle bandiere

È un registro a 8 bit con cinque flip-flop da 1 bit, che contiene 0 o 1 a seconda del risultato memorizzato nell'accumulatore.

Questi sono il set di 5 infradito -

- Segno (S)

- Zero (Z)

- Trasporto ausiliario (AC)

- Parità (P)

- Trasportare (C)

La sua posizione del bit è mostrata nella tabella seguente:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| S | Z | corrente alternata | P | CY |

Registro delle istruzioni e decodificatore

È un registro a 8 bit. Quando un'istruzione viene recuperata dalla memoria, viene archiviata nel registro delle istruzioni. Il decodificatore delle istruzioni decodifica le informazioni presenti nel registro delle istruzioni.

Unità di temporizzazione e controllo

Fornisce il segnale di temporizzazione e controllo al microprocessore per eseguire le operazioni. Di seguito sono riportati i segnali di temporizzazione e controllo, che controllano i circuiti esterni e interni:

- Segnali di controllo: READY, RD ', WR', ALE

- Segnali di stato: S0, S1, IO / M '

- Segnali DMA: HOLD, HLDA

- Segnali di RESET: RESET IN, RESET OUT

Controllo dell'interruzione

Come suggerisce il nome, controlla gli interrupt durante un processo. Quando un microprocessore sta eseguendo un programma principale e ogni volta che si verifica un'interruzione, il microprocessore sposta il controllo dal programma principale per elaborare la richiesta in arrivo. Dopo che la richiesta è stata completata, il controllo torna al programma principale.

Ci sono 5 segnali di interrupt nel microprocessore 8085: INTR, RST 7.5, RST 6.5, RST 5.5, TRAP.

Controllo ingresso / uscita seriale

Controlla la comunicazione dei dati seriali utilizzando queste due istruzioni: SID (Serial input data) e SOD (Serial output data).

Buffer degli indirizzi e buffer dei dati degli indirizzi

Il contenuto memorizzato nello stack pointer e nel program counter viene caricato nel buffer degli indirizzi e nel buffer dei dati degli indirizzi per comunicare con la CPU. La memoria e i chip I / O sono collegati a questi bus; la CPU può scambiare i dati desiderati con la memoria e i chip di I / O.

Bus indirizzi e bus dati

Il bus dati trasporta i dati da memorizzare. È bidirezionale, mentre il bus indirizzi trasporta la posizione in cui dovrebbe essere memorizzato ed è unidirezionale. Viene utilizzato per trasferire i dati e i dispositivi I / O di indirizzo.

8085 Architecture

Abbiamo provato a rappresentare l'architettura dell'8085 con questa immagine seguente:

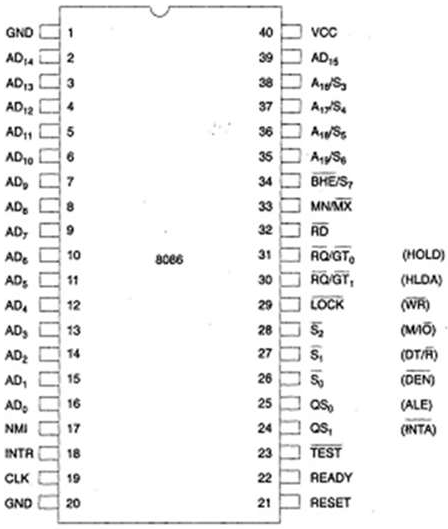

L'immagine seguente mostra il diagramma dei pin del microprocessore 8085 -

I pin di un microprocessore 8085 possono essere classificati in sette gruppi:

Indirizzo bus

A15-A8, trasporta gli 8 bit più significativi di memoria / indirizzo IO.

Bus dati

AD7-AD0, trasporta l'indirizzo a 8 bit e il bus dati meno significativi.

Segnali di controllo e stato

Questi segnali vengono utilizzati per identificare la natura del funzionamento. Ci sono 3 segnali di controllo e 3 segnali di stato.

Tre segnali di controllo sono RD, WR e ALE.

RD - Questo segnale indica che l'IO o il dispositivo di memoria selezionato deve essere letto ed è pronto per accettare i dati disponibili sul bus dati.

WR - Questo segnale indica che i dati sul bus dati devono essere scritti in una memoria o posizione IO selezionata.

ALE- È un impulso ad andamento positivo generato all'avvio di una nuova operazione dal microprocessore. Quando l'impulso è alto, indica l'indirizzo. Quando il polso scende indica i dati.

Tre segnali di stato sono IO / M, S0 e S1.

IO / M

Questo segnale viene utilizzato per distinguere tra operazioni di I / O e di memoria, cioè quando è alto indica operazione di I / O e quando è basso indica operazione da memoria.

S1 e S0

Questi segnali vengono utilizzati per identificare il tipo di operazione corrente.

Alimentazione elettrica

Sono presenti 2 segnali di alimentazione: VCC e VSS. VCC indica alimentazione + 5v e VSS indica segnale di massa.

Segnali dell'orologio

Ci sono 3 segnali di clock, cioè X1, X2, CLK OUT.

X1, X2- Un cristallo (RC, LC N / W) è collegato a questi due pin e viene utilizzato per impostare la frequenza del generatore di clock interno. Questa frequenza è divisa internamente per 2.

CLK OUT - Questo segnale viene utilizzato come orologio di sistema per i dispositivi collegati al microprocessore.

Interruzioni e segnali avviati esternamente

Gli interrupt sono i segnali generati da dispositivi esterni per richiedere al microprocessore di eseguire un'attività. Ci sono 5 segnali di interrupt, cioè TRAP, RST 7.5, RST 6.5, RST 5.5 e INTR. Discuteremo gli interrupt in dettaglio nella sezione interrupt.

INTA - È un segnale di conferma dell'interruzione.

RESET IN - Questo segnale viene utilizzato per resettare il microprocessore azzerando il contatore del programma.

RESET OUT - Questo segnale viene utilizzato per resettare tutti i dispositivi collegati al ripristino del microprocessore.

READY- Questo segnale indica che il dispositivo è pronto per inviare o ricevere dati. Se READY è basso, la CPU deve attendere che READY diventi alto.

HOLD - Questo segnale indica che un altro master richiede l'uso dei bus di indirizzo e dati.

HLDA (HOLD Acknowledge)- Indica che la CPU ha ricevuto la richiesta HOLD e abbandonerà il bus nel ciclo di clock successivo. HLDA è impostato su basso dopo la rimozione del segnale HOLD.

Segnali I / O seriali

Ci sono 2 segnali seriali, cioè SID e SOD e questi segnali sono usati per la comunicazione seriale.

SOD (Linea dati di uscita seriale) - L'uscita SOD viene impostata / ripristinata come specificato dall'istruzione SIM.

SID (Riga dati di ingresso seriale) - I dati su questa riga vengono caricati nell'accumulatore ogni volta che viene eseguita un'istruzione RIM.

Parliamo ora delle modalità di indirizzamento nel microprocessore 8085.

Modalità di indirizzamento nell'8085

Sono le istruzioni utilizzate per trasferire i dati da un registro a un altro registro, dalla memoria al registro e dal registro alla memoria senza alcuna alterazione del contenuto. Le modalità di indirizzamento in 8085 sono classificate in 5 gruppi:

Modalità di indirizzamento immediato

In questa modalità, i dati a 8/16 bit sono specificati nell'istruzione stessa come uno dei suoi operandi. For example: MVI K, 20F: significa che 20F viene copiato nel registro K.

Registra la modalità di indirizzamento

In questa modalità, i dati vengono copiati da un registro all'altro. For example: MOV K, B: significa che i dati nel registro B vengono copiati nel registro K.

Modalità di indirizzamento diretto

In questa modalità, i dati vengono copiati direttamente dall'indirizzo specificato nel registro. For example: LDB 5000K: significa che i dati all'indirizzo 5000K vengono copiati nel registro B.

Modalità di indirizzamento indiretto

In questa modalità, i dati vengono trasferiti da un registro all'altro utilizzando l'indirizzo puntato dal registro. For example: MOV K, B: significa che i dati vengono trasferiti dall'indirizzo di memoria puntato dal registro al registro K.

Modalità di indirizzamento implicito

Questa modalità non richiede alcun operando; i dati sono specificati dal codice operativo stesso.For example: CMP.

Si interrompe nell'8085

Gli interrupt sono i segnali generati dai dispositivi esterni per richiedere al microprocessore di eseguire un'attività. Ci sono 5 segnali di interrupt, cioè TRAP, RST 7.5, RST 6.5, RST 5.5 e INTR.

Gli interrupt sono classificati nei seguenti gruppi in base al loro parametro:

Vector interrupt - In questo tipo di interrupt, l'indirizzo dell'interrupt è noto al processore. For example: RST7.5, RST6.5, RST5.5, TRAP.

Non-Vector interrupt - In questo tipo di interrupt, l'indirizzo dell'interrupt non è noto al processore, quindi l'indirizzo dell'interrupt deve essere inviato esternamente dal dispositivo per eseguire gli interrupt. For example: INTR.

Maskable interrupt - In questo tipo di interrupt, possiamo disabilitare l'interrupt scrivendo alcune istruzioni nel programma. For example: RST7.5, RST6.5, RST5.5.

Non-Maskable interrupt - In questo tipo di interrupt, non possiamo disabilitare l'interrupt scrivendo alcune istruzioni nel programma. For example: TRAPPOLA.

Software interrupt- In questo tipo di interrupt, il programmatore deve aggiungere le istruzioni nel programma per eseguire l'interrupt. Ci sono 8 interrupt software nell'8085, cioè RST0, RST1, RST2, RST3, RST4, RST5, RST6 e RST7.

Hardware interrupt - Ci sono 5 pin di interrupt nell'8085 usati come interrupt hardware, cioè TRAP, RST7.5, RST6.5, RST5.5, INTA.

Note- NTA non è un interrupt, viene utilizzato dal microprocessore per l'invio del riconoscimento. TRAP ha la priorità più alta, quindi RST7.5 e così via.

Interrupt Service Routine (ISR)

Un piccolo programma o una routine che, quando viene eseguita, serve la corrispondente sorgente di interruzione è chiamata ISR.

TRAPPOLA

È un interrupt non mascherabile, con la priorità più alta tra tutti gli interrupt. Per impostazione predefinita, è abilitato fino a quando non viene riconosciuto. In caso di guasto, viene eseguito come ISR e invia i dati alla memoria di backup. Questo interrupt trasferisce il controllo alla posizione 0024H.

RST7.5

È un interrupt mascherabile, con la seconda priorità più alta tra tutti gli interrupt. Quando viene eseguito questo interrupt, il processore salva il contenuto del registro del PC nello stack e si dirama all'indirizzo 003CH.

RST 6.5

È un interrupt mascherabile, con la terza priorità più alta tra tutti gli interrupt. Quando viene eseguito questo interrupt, il processore salva il contenuto del registro del PC nello stack e si dirama all'indirizzo 0034H.

RST 5.5

È un'interruzione mascherabile. Quando viene eseguito questo interrupt, il processore salva il contenuto del registro del PC nello stack e si dirama all'indirizzo 002CH.

INTR

È un interrupt mascherabile, con la priorità più bassa tra tutti gli interrupt. Può essere disabilitato resettando il microprocessore.

quando INTR signal goes high, possono verificarsi i seguenti eventi:

Il microprocessore controlla lo stato del segnale INTR durante l'esecuzione di ogni istruzione.

Quando il segnale INTR è alto, il microprocessore completa la sua istruzione corrente e invia il segnale di riconoscimento interrupt basso attivo.

Quando le istruzioni vengono ricevute, il microprocessore salva l'indirizzo dell'istruzione successiva sullo stack ed esegue l'istruzione ricevuta.

Diamo uno sguardo alla programmazione del microprocessore 8085.

I set di istruzioni sono codici di istruzioni per eseguire alcune attività. È classificato in cinque categorie.

| S.No. | Istruzioni e descrizione |

|---|---|

| 1 | Istruzioni di controllo Di seguito è riportata la tabella che mostra l'elenco delle istruzioni di controllo con il loro significato. |

| 2 | Istruzioni logiche Di seguito è riportata la tabella che mostra l'elenco delle istruzioni logiche con il loro significato. |

| 3 | Istruzioni di ramificazione Di seguito è riportata la tabella che mostra l'elenco delle istruzioni di diramazione con il loro significato. |

| 4 | Istruzioni aritmetiche Di seguito è riportata la tabella che mostra l'elenco delle istruzioni aritmetiche con il loro significato. |

| 5 | Istruzioni per il trasferimento dei dati Di seguito è riportata la tabella che mostra l'elenco delle istruzioni di trasferimento dati con il loro significato. |

8085 - Programmi demo

Ora, diamo un'occhiata ad alcune dimostrazioni del programma usando le istruzioni sopra -

Aggiunta di due numeri a 8 bit

Scrivere un programma per aggiungere dati nella posizione di memoria 3005H e 3006H e memorizzare il risultato nella posizione di memoria 3007H.

Problem demo -

(3005H) = 14H

(3006H) = 89HResult -

14H + 89H = 9DH

Il codice del programma può essere scritto in questo modo:

LXI H 3005H : "HL points 3005H"

MOV A, M : "Getting first operand"

INX H : "HL points 3006H"

ADD M : "Add second operand"

INX H : "HL points 3007H"

MOV M, A : "Store result at 3007H"

HLT : "Exit program"Scambio di posizioni di memoria

Scrivere un programma per scambiare i dati nella posizione di memoria 5000M e 6000M.

LDA 5000M : "Getting the contents at5000M location into accumulator"

MOV B, A : "Save the contents into B register"

LDA 6000M : "Getting the contents at 6000M location into accumulator"

STA 5000M : "Store the contents of accumulator at address 5000M"

MOV A, B : "Get the saved contents back into A register"

STA 6000M : "Store the contents of accumulator at address 6000M"Disponi i numeri in ordine crescente

Scrivere un programma per disporre i primi 10 numeri dall'indirizzo di memoria 3000H in ordine crescente.

MVI B, 09 :"Initialize counter"

START :"LXI H, 3000H: Initialize memory pointer"

MVI C, 09H :"Initialize counter 2"

BACK: MOV A, M :"Get the number"

INX H :"Increment memory pointer"

CMP M :"Compare number with next number"

JC SKIP :"If less, don’t interchange"

JZ SKIP :"If equal, don’t interchange"

MOV D, M

MOV M, A

DCX H

MOV M, D

INX H :"Interchange two numbers"

SKIP:DCR C :"Decrement counter 2"

JNZ BACK :"If not zero, repeat"

DCR B :"Decrement counter 1"

JNZ START

HLT :"Terminate program execution"8086 Microprocessor è una versione migliorata di 8085Microprocessor progettato da Intel nel 1976. Si tratta di un microprocessore a 16 bit con 20 linee di indirizzo e 16 linee di dati che fornisce fino a 1 MB di memoria. Consiste in un potente set di istruzioni, che fornisce facilmente operazioni come moltiplicazione e divisione.

Supporta due modalità di funzionamento, ovvero modalità massima e modalità minima. La modalità massima è adatta per sistemi con più processori e la modalità minima è adatta per sistemi con un singolo processore.

Caratteristiche di 8086

Le caratteristiche più importanti di un microprocessore 8086 sono le seguenti:

Ha una coda di istruzioni, che è in grado di memorizzare sei byte di istruzioni dalla memoria con conseguente elaborazione più veloce.

È stato il primo processore a 16 bit con ALU a 16 bit, registri a 16 bit, bus dati interno e bus dati esterno a 16 bit con conseguente elaborazione più rapida.

È disponibile in 3 versioni in base alla frequenza di funzionamento -

8086 → 5 MHz

8086-2 → 8 MHz

(c) 8086-1 → 10 MHz

Utilizza due fasi di pipelining, ovvero Fetch Stage ed Execute Stage, che migliora le prestazioni.

La fase di recupero può precaricare fino a 6 byte di istruzioni e le memorizza nella coda.

Execute stage esegue queste istruzioni.

Ha 256 interrupt vettorizzati.

Consiste di 29.000 transistor.

Confronto tra 8085 e 8086 Microprocessore

Size - 8085 è un microprocessore a 8 bit, mentre 8086 è un microprocessore a 16 bit.

Address Bus - 8085 ha un bus indirizzi a 16 bit mentre 8086 ha un bus indirizzi a 20 bit.

Memory - 8085 può accedere fino a 64 KB, mentre 8086 può accedere fino a 1 Mb di memoria.

Instruction - 8085 non ha una coda di istruzioni, mentre 8086 ha una coda di istruzioni.

Pipelining - 8085 non supporta un'architettura pipeline mentre 8086 supporta un'architettura pipeline.

I/O - 8085 può indirizzare 2 ^ 8 = 256 I / O, mentre 8086 può accedere a 2 ^ 16 = 65.536 I / O.

Cost - Il costo dell'8085 è basso mentre quello dell'8086 è alto.

Architettura dell'8086

Il diagramma seguente mostra l'architettura di un microprocessore 8086 -

8086 Il microprocessore è diviso in due unità funzionali, ovvero EU (Execution Unit) e BIU (Unità interfaccia bus).

UE (unità esecutiva)

L'unità di esecuzione fornisce istruzioni alla BIU indicando da dove prelevare i dati e quindi decodificare ed eseguire tali istruzioni. La sua funzione è controllare le operazioni sui dati utilizzando l'istruzione decoder e ALU. EU non ha alcun collegamento diretto con i bus di sistema come mostrato nella figura sopra, esegue operazioni sui dati tramite BIU.

Parliamo ora delle parti funzionali dei microprocessori 8086.

ALU

Gestisce tutte le operazioni aritmetiche e logiche, come +, -, ×, /, OR, AND, NOT.

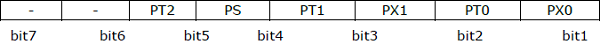

Flag Register

È un registro a 16 bit che si comporta come un flip-flop, cioè cambia il suo stato in base al risultato memorizzato nell'accumulatore. Ha 9 flag e sono divisi in 2 gruppi: flag condizionali e flag di controllo.

Flag condizionali

Rappresenta il risultato dell'ultima istruzione aritmetica o logica eseguita. Di seguito è riportato l'elenco dei flag condizionali:

Carry flag - Questo flag indica una condizione di overflow per le operazioni aritmetiche.

Auxiliary flag- Quando un'operazione viene eseguita in ALU, risulta in un carry / barrow da nibble inferiore (cioè D0 - D3) a nibble superiore (cioè D4 - D7), allora questo flag è Flag AF. Il processore utilizza questo flag per eseguire la conversione da binario a BCD.

Parity flag- Questo flag viene utilizzato per indicare la parità del risultato, ovvero quando gli 8 bit di ordine inferiore del risultato contengono un numero pari di 1, viene impostato il flag di parità. Per un numero dispari di 1, il flag di parità viene ripristinato.

Zero flag - Questo flag è impostato a 1 quando il risultato di un'operazione aritmetica o logica è zero, altrimenti è impostato a 0.

Sign flag - Questo flag contiene il segno del risultato, cioè quando il risultato dell'operazione è negativo, il flag del segno è impostato a 1 altrimenti impostato a 0.

Overflow flag - Questo flag rappresenta il risultato quando viene superata la capacità del sistema.

Flag di controllo

I flag di controllo controllano le operazioni dell'unità di esecuzione. Di seguito è riportato l'elenco dei flag di controllo:

Trap flag- Viene utilizzato per il controllo a passo singolo e consente all'utente di eseguire un'istruzione alla volta per il debug. Se è impostato, il programma può essere eseguito in una modalità a passo singolo.

Interrupt flag- È un flag di abilitazione / disabilitazione dell'interruzione, ovvero utilizzato per consentire / vietare l'interruzione di un programma. È impostato a 1 per la condizione di interrupt abilitato e impostato a 0 per la condizione di interrupt disabilitato.

Direction flag- Viene utilizzato nelle operazioni su stringhe. Come suggerisce il nome quando è impostato, si accede ai byte di stringa dall'indirizzo di memoria superiore all'indirizzo di memoria inferiore e viceversa.

Registro di uso generale

Sono disponibili 8 registri di uso generale, ovvero AH, AL, BH, BL, CH, CL, DH e DL. Questi registri possono essere utilizzati individualmente per memorizzare dati a 8 bit e possono essere utilizzati in coppia per memorizzare dati a 16 bit. Le coppie di registri valide sono AH e AL, BH e BL, CH e CL e DH e DL. Si riferisce rispettivamente ad AX, BX, CX e DX.

AX register- È anche noto come registro accumulatore. Viene utilizzato per memorizzare gli operandi per le operazioni aritmetiche.

BX register- Viene utilizzato come registro di base. Viene utilizzato per memorizzare l'indirizzo di base iniziale dell'area di memoria all'interno del segmento di dati.

CX register- È indicato come contatore. Viene utilizzato nelle istruzioni di loop per memorizzare il contatore di loop.

DX register - Questo registro viene utilizzato per contenere l'indirizzo della porta I / O per l'istruzione I / O.

Registro del puntatore dello stack

È un registro a 16 bit, che contiene l'indirizzo dall'inizio del segmento alla posizione di memoria, dove una parola è stata memorizzata più di recente nello stack.

BIU (unità interfaccia bus)

BIU si occupa di tutti i trasferimenti di dati e indirizzi sui bus per l'UE come l'invio di indirizzi, il recupero di istruzioni dalla memoria, la lettura dei dati dalle porte e dalla memoria, nonché la scrittura dei dati nelle porte e nella memoria. L'UE non ha alcun collegamento di direzione con i bus di sistema, quindi questo è possibile con la BIU. EU e BIU sono collegati con il Bus Interno.

Ha le seguenti parti funzionali:

Instruction queue- BIU contiene la coda delle istruzioni. BIU riceve fino a 6 byte di istruzioni successive e le memorizza nella coda delle istruzioni. Quando EU esegue le istruzioni ed è pronto per l'istruzione successiva, legge semplicemente l'istruzione da questa coda di istruzioni con conseguente maggiore velocità di esecuzione.

Viene chiamato il recupero dell'istruzione successiva durante l'esecuzione dell'istruzione corrente pipelining.

Segment register- BIU ha 4 bus di segmento, cioè CS, DS, SS & ES. Contiene gli indirizzi delle istruzioni e dei dati in memoria, che vengono utilizzati dal processore per accedere alle posizioni di memoria. Contiene anche 1 registro puntatore IP, che contiene l'indirizzo della successiva istruzione eseguita dall'UE.

CS- È l'acronimo di Code Segment. Viene utilizzato per indirizzare una posizione di memoria nel segmento di codice della memoria, dove è memorizzato il programma eseguibile.

DS- È l'acronimo di Data Segment. Consiste di dati utilizzati dal programma e vi si accede nel segmento dati da un indirizzo di offset o dal contenuto di un altro registro che contiene l'indirizzo di offset.

SS- Sta per Stack Segment. Gestisce la memoria per memorizzare dati e indirizzi durante l'esecuzione.

ES- È l'acronimo di Extra Segment. ES è un segmento di dati aggiuntivo, utilizzato dalla stringa per contenere i dati di destinazione aggiuntivi.

Instruction pointer - È un registro a 16 bit utilizzato per contenere l'indirizzo della successiva istruzione da eseguire.

8086 è stato il primo microprocessore a 16 bit disponibile nel chip DIP (Dual Inline Package) a 40 pin. Discutiamo ora in dettaglio la configurazione dei pin di un microprocessore 8086.

Schema pin 8086

Ecco il diagramma dei pin del microprocessore 8086 -

Discutiamo ora i segnali in dettaglio:

Power supply and frequency signals

Utilizza un'alimentazione a 5 V CC a V CC pin 40 e utilizza la massa a V SS pin 1 e 20 per il suo funzionamento.

Clock signal

Il segnale di clock viene fornito tramite il Pin-19. Fornisce i tempi al processore per le operazioni. La sua frequenza è diversa per le diverse versioni, cioè 5 MHz, 8 MHz e 10 MHz.

Address/data bus

AD0-AD15. Questi sono 16 indirizzi / bus dati. AD0-AD7 trasporta dati di byte di ordine basso e AD8AD15 trasporta dati di byte di ordine superiore. Durante il primo ciclo di clock, trasporta indirizzi a 16 bit e successivamente trasporta dati a 16 bit.

Address/status bus

A16-A19 / S3-S6. Questi sono i 4 bus di indirizzo / stato. Durante il primo ciclo di clock, porta l'indirizzo a 4 bit e successivamente trasporta i segnali di stato.

S7/BHE

BHE sta per Bus High Enable. È disponibile al pin 34 e viene utilizzato per indicare il trasferimento di dati utilizzando il bus dati D8-D15. Questo segnale è basso durante il primo ciclo di clock, dopodiché è attivo.

Read($\overline{RD}$)

È disponibile al pin 32 e viene utilizzato per leggere il segnale per l'operazione di lettura.

Ready

È disponibile al pin 22. È un segnale di riconoscimento dai dispositivi I / O che i dati vengono trasferiti. È un segnale alto attivo. Quando è alto, indica che il dispositivo è pronto per il trasferimento dei dati. Quando è basso, indica lo stato di attesa.

RESET

È disponibile al pin 21 e serve per riavviare l'esecuzione. Fa sì che il processore interrompa immediatamente la sua attività attuale. Questo segnale è attivo alto per i primi 4 cicli di clock per RESETTARE il microprocessore.

INTR

È disponibile al pin 18. Si tratta di un segnale di richiesta di interruzione, che viene campionato durante l'ultimo ciclo di clock di ciascuna istruzione per determinare se il processore lo considera come interruzione o meno.

NMI

Sta per interrupt non mascherabile ed è disponibile al pin 17. È un ingresso triggerato dal fronte, che provoca una richiesta di interrupt al microprocessore.

$\overline{TEST}$

Questo segnale è come lo stato di attesa ed è disponibile al pin 23. Quando questo segnale è alto, il processore deve attendere lo stato IDLE, altrimenti l'esecuzione continua.

MN/$\overline{MX}$

Sta per Minimo / Massimo ed è disponibile al pin 33. Indica in quale modalità deve funzionare il processore; quando è alto funziona in modalità minima e viceversa.

INTA

È un segnale di riconoscimento di interruzione e ID disponibile al pin 24. Quando il microprocessore riceve questo segnale, riconosce l'interruzione.

ALE

È l'acronimo di address enable latch ed è disponibile al pin 25. Un impulso positivo viene generato ogni volta che il processore inizia qualsiasi operazione. Questo segnale indica la disponibilità di un indirizzo valido sulle linee indirizzo / dati.

DEN

Sta per Data Enable ed è disponibile al pin 26. Viene utilizzato per abilitare il Transreceiver 8286. Il transreceiver è un dispositivo utilizzato per separare i dati dall'indirizzo / bus dati.

DT/R

È l'acronimo di Segnale di trasmissione / ricezione dati ed è disponibile al pin 27. Decide la direzione del flusso di dati attraverso il ricetrasmettitore. Quando è alto, i dati vengono trasmessi e viceversa.

M/IO

Questo segnale viene utilizzato per distinguere tra operazioni di memoria e operazioni di I / O. Quando è alto, indica l'operazione di I / O e quando è basso indica l'operazione di memoria. È disponibile al pin 28.

WR

Sta per segnale di scrittura ed è disponibile al pin 29. Viene utilizzato per scrivere i dati nella memoria o nel dispositivo di uscita a seconda dello stato del segnale M / IO.

HLDA

È l'acronimo di Hold A recognition signal ed è disponibile al pin 30. Questo segnale riconosce il segnale HOLD.

HOLD

Questo segnale indica al processore che i dispositivi esterni richiedono di accedere ai bus di indirizzo / dati. È disponibile al pin 31.

QS1 and QS0

Questi sono segnali di stato della coda e sono disponibili ai pin 24 e 25. Questi segnali forniscono lo stato della coda di istruzioni. Le loro condizioni sono riportate nella tabella seguente:

| QS 0 | QS 1 | Stato |

|---|---|---|

| 0 | 0 | Nessuna operazione |

| 0 | 1 | Primo byte di codice operativo dalla coda |

| 1 | 0 | Svuota la coda |

| 1 | 1 | Byte successivo dalla coda |

S0, S1, S2

Questi sono i segnali di stato che forniscono lo stato di funzionamento, che viene utilizzato dal controller bus 8288 per generare segnali di controllo I / O e memoria. Questi sono disponibili ai pin 26, 27 e 28. Di seguito è riportata la tabella che mostra il loro stato:

| S 2 | S 1 | S 0 | Stato |

|---|---|---|---|

| 0 | 0 | 0 | Riconoscimento dell'interruzione |

| 0 | 0 | 1 | Lettura I / O |

| 0 | 1 | 0 | Scrittura I / O |

| 0 | 1 | 1 | Ferma |

| 1 | 0 | 0 | Recupero codice operativo |

| 1 | 0 | 1 | Lettura della memoria |

| 1 | 1 | 0 | Scrittura in memoria |

| 1 | 1 | 1 | Passivo |

LOCK

Quando questo segnale è attivo, indica agli altri processori di non chiedere alla CPU di lasciare il bus di sistema. Si attiva utilizzando il prefisso LOCK su qualsiasi istruzione ed è disponibile al pin 29.

RQ/GT1 and RQ/GT0

Questi sono i segnali di richiesta / concessione utilizzati dagli altri processori che richiedono alla CPU di rilasciare il bus di sistema. Quando il segnale viene ricevuto dalla CPU, invia il riconoscimento. RQ / GT 0 ha una priorità maggiore di RQ / GT 1 .

Il microprocessore 8086 supporta 8 tipi di istruzioni:

- Istruzioni per il trasferimento dei dati

- Istruzioni aritmetiche

- Istruzioni per la manipolazione dei bit

- Istruzioni per le stringhe

- Istruzioni di trasferimento dell'esecuzione del programma (istruzioni Branch & Loop)

- Istruzioni per il controllo del processore

- Istruzioni per il controllo dell'iterazione

- Istruzioni di interruzione

Discutiamo ora in dettaglio questi set di istruzioni.

Istruzioni per il trasferimento dei dati

Queste istruzioni vengono utilizzate per trasferire i dati dall'operando di origine all'operando di destinazione. Di seguito è riportato l'elenco delle istruzioni in questo gruppo:

Istruzioni per trasferire una parola

MOV - Utilizzato per copiare il byte o la parola dalla sorgente fornita alla destinazione fornita.

PPUSH - Usato per mettere una parola in cima alla pila.

POP - Utilizzato per ottenere una parola dalla cima della pila alla posizione fornita.

PUSHA - Usato per mettere tutti i registri nello stack.

POPA - Usato per portare le parole dallo stack a tutti i registri.

XCHG - Utilizzato per scambiare i dati da due posizioni.

XLAT - Usato per tradurre un byte in AL utilizzando una tabella in memoria.

Istruzioni per il trasferimento delle porte di input e output

IN - Utilizzato per leggere un byte o una parola dalla porta fornita all'accumulatore.

OUT - Utilizzato per inviare un byte o una parola dall'accumulatore alla porta fornita.

Istruzioni per trasferire l'indirizzo

LEA - Utilizzato per caricare l'indirizzo dell'operando nel registro fornito.

LDS - Usato per caricare il registro DS e altri registri forniti dalla memoria

LES - Utilizzato per caricare il registro ES e altri registri forniti dalla memoria.

Istruzioni per trasferire i registri flag

LAHF - Utilizzato per caricare AH con il byte basso del registro flag.

SAHF - Utilizzato per memorizzare il registro AH nel byte basso del registro flag.

PUSHF - Usato per copiare il registro flag in cima allo stack.

POPF - Usato per copiare una parola in cima allo stack nel registro flag.

Istruzioni aritmetiche

Queste istruzioni vengono utilizzate per eseguire operazioni aritmetiche come addizione, sottrazione, moltiplicazione, divisione, ecc.

Di seguito è riportato l'elenco delle istruzioni in questo gruppo:

Istruzioni per eseguire l'addizione

ADD - Utilizzato per aggiungere il byte fornito a byte / parola a parola.

ADC - Usato per aggiungere con riporto.

INC - Utilizzato per incrementare di 1 il byte / parola fornito.

AAA - Utilizzato per regolare ASCII dopo l'aggiunta.

DAA - Utilizzato per regolare il decimale dopo l'operazione di addizione / sottrazione.

Istruzioni per eseguire la sottrazione

SUB - Usato per sottrarre il byte da byte / parola dalla parola.

SBB - Utilizzato per eseguire la sottrazione con il prestito.

DEC - Utilizzato per decrementare di 1 il byte / parola fornito.

NPG - Usato per negare ogni bit del byte / parola fornito e aggiungere il complemento di 1/2.

CMP - Usato per confrontare 2 byte / parola forniti.

AAS - Utilizzato per regolare i codici ASCII dopo la sottrazione.

DAS - Utilizzato per regolare i decimali dopo la sottrazione.

Istruzioni per eseguire la moltiplicazione

MUL - Usato per moltiplicare byte senza segno per byte / parola per parola.

IMUL - Utilizzato per moltiplicare byte con segno per byte / parola per parola.

AAM - Utilizzato per regolare i codici ASCII dopo la moltiplicazione.

Istruzioni per eseguire la divisione

DIV - Utilizzato per dividere la parola senza segno per byte o la doppia parola senza segno per parola.

IDIV - Usato per dividere la parola con segno per byte o la doppia parola con segno per parola.

AAD - Utilizzato per regolare i codici ASCII dopo la divisione.

CBW - Usato per riempire il byte superiore della parola con le copie del bit di segno del byte inferiore.

CWD - Usato per riempire la parola superiore della doppia parola con il bit di segno della parola inferiore.

Istruzioni per la manipolazione dei bit

Queste istruzioni vengono utilizzate per eseguire operazioni in cui sono coinvolti bit di dati, ovvero operazioni come logica, spostamento, ecc.

Di seguito è riportato l'elenco delle istruzioni in questo gruppo:

Istruzioni per eseguire un'operazione logica

NOT - Usato per invertire ogni bit di un byte o di una parola.

AND - Utilizzato per aggiungere ogni bit in un byte / parola con il bit corrispondente in un altro byte / parola.

OR - Utilizzato per moltiplicare ogni bit in un byte / parola con il bit corrispondente in un altro byte / parola.

XOR - Usato per eseguire un'operazione di OR esclusivo su ogni bit in un byte / parola con il bit corrispondente in un altro byte / parola.

TEST - Utilizzato per aggiungere operandi per aggiornare i flag, senza influire sugli operandi.

Istruzioni per eseguire operazioni su turni

SHL/SAL - Usato per spostare i bit di un byte / parola verso sinistra e inserire zero (S) negli LSB.

SHR - Usato per spostare i bit di un byte / parola verso destra e mettere zero (S) in MSB.

SAR - Usato per spostare i bit di un byte / parola verso destra e copiare il vecchio MSB nel nuovo MSB.

Istruzioni per eseguire operazioni di rotazione

ROL - Utilizzato per ruotare i bit di byte / parola verso sinistra, cioè MSB su LSB e su Carry Flag [CF].

ROR - Utilizzato per ruotare i bit di byte / parola verso destra, cioè da LSB a MSB e a Carry Flag [CF].

RCR - Utilizzato per ruotare i bit di byte / parola verso destra, cioè da LSB a CF e da CF a MSB.

RCL - Utilizzato per ruotare i bit di byte / parola verso sinistra, ovvero MSB in CF e CF in LSB.

Istruzioni per le stringhe

La stringa è un gruppo di byte / parole e la loro memoria è sempre allocata in ordine sequenziale.

Di seguito è riportato l'elenco delle istruzioni in questo gruppo:

REP - Usato per ripetere l'istruzione data fino a CX ≠ 0.

REPE/REPZ - Usato per ripetere l'istruzione data fino a quando CX = 0 o zero flag ZF = 1.

REPNE/REPNZ - Usato per ripetere l'istruzione data fino a quando CX = 0 o zero flag ZF = 1.

MOVS/MOVSB/MOVSW - Utilizzato per spostare il byte / parola da una stringa all'altra.

COMS/COMPSB/COMPSW - Utilizzato per confrontare due byte / parole di stringa.

INS/INSB/INSW - Utilizzato come stringa / byte / parola di ingresso dalla porta I / O alla posizione di memoria fornita.

OUTS/OUTSB/OUTSW - Utilizzato come stringa / byte / parola di output dalla posizione di memoria fornita alla porta I / O.

SCAS/SCASB/SCASW - Usato per scansionare una stringa e confrontare il suo byte con un byte in AL o una parola stringa con una parola in AX.

LODS/LODSB/LODSW - Utilizzato per memorizzare il byte della stringa in AL o la parola della stringa in AX.

Istruzioni di trasferimento dell'esecuzione del programma (istruzioni branch e loop)

Queste istruzioni vengono utilizzate per trasferire / ramificare le istruzioni durante un'esecuzione. Include le seguenti istruzioni:

Istruzioni per trasferire l'istruzione durante un'esecuzione senza alcuna condizione -

CALL - Usato per chiamare una procedura e salvare il loro indirizzo di ritorno nello stack.

RET - Usato per tornare dalla procedura al programma principale.

JMP - Utilizzato per saltare all'indirizzo fornito per procedere all'istruzione successiva.

Istruzioni per trasferire l'istruzione durante un'esecuzione con alcune condizioni -

JA/JNBE - Usato per saltare se le istruzioni sopra / non sotto / uguale soddisfano.

JAE/JNB - Usato per saltare se le istruzioni sopra / non sotto soddisfano.

JBE/JNA - Usato per saltare se l'istruzione inferiore / uguale / non superiore soddisfa.

JC - Usato per saltare se carry flag CF = 1

JE/JZ - Usato per saltare se flag uguale / zero ZF = 1

JG/JNLE - Usato per saltare se l'istruzione maggiore / non minore / uguale soddisfa.

JGE/JNL - Usato per saltare se maggiore / uguale / non minore dell'istruzione soddisfa.

JL/JNGE - Usato per saltare se l'istruzione minore / non maggiore / uguale soddisfa.

JLE/JNG - Usato per saltare se minore / uguale / se non maggiore dell'istruzione soddisfa.

JNC - Usato per saltare se non c'è flag di riporto (CF = 0)

JNE/JNZ - Usato per saltare se non uguale / zero flag ZF = 0

JNO - Usato per saltare se nessun flag di overflow OF = 0

JNP/JPO - Usato per saltare se non parità / parità dispari PF = 0

JNS - Usato per saltare se non segno SF = 0

JO - Usato per saltare se il flag di overflow OF = 1

JP/JPE - Usato per saltare se parità / parità anche PF = 1

JS - Usato per saltare se il flag di segno SF = 1

Istruzioni per il controllo del processore

Queste istruzioni vengono utilizzate per controllare l'azione del processore impostando / ripristinando i valori dei flag.

Di seguito sono riportate le istruzioni in questo gruppo:

STC - Usato per impostare carry flag CF su 1

CLC - Usato per cancellare / resettare il flag di carry CF su 0

CMC - Usato per mettere il complemento allo stato di carry flag CF.

STD - Usato per impostare il flag di direzione DF su 1

CLD - Usato per cancellare / ripristinare il flag di direzione DF su 0

STI - Utilizzato per impostare il flag di abilitazione interrupt su 1, ovvero abilitare l'ingresso INTR.

CLI - Usato per cancellare il flag di abilitazione interrupt a 0, cioè disabilitare l'ingresso INTR.

Istruzioni per il controllo dell'iterazione

Queste istruzioni vengono utilizzate per eseguire le istruzioni fornite per il numero di volte. Di seguito è riportato l'elenco delle istruzioni in questo gruppo:

LOOP - Utilizzato per eseguire il ciclo di un gruppo di istruzioni fino a quando la condizione non è soddisfatta, ovvero CX = 0

LOOPE/LOOPZ - Usato per ripetere un gruppo di istruzioni finché non soddisfa ZF = 1 e CX = 0

LOOPNE/LOOPNZ - Utilizzato per eseguire il ciclo di un gruppo di istruzioni finché non soddisfa ZF = 0 e CX = 0

JCXZ - Utilizzato per saltare all'indirizzo fornito se CX = 0

Istruzioni di interruzione

Queste istruzioni vengono utilizzate per richiamare l'interrupt durante l'esecuzione del programma.

INT - Utilizzato per interrompere il programma durante l'esecuzione e la chiamata del servizio specificato.

INTO - Utilizzato per interrompere il programma durante l'esecuzione se OF = 1

IRET - Usato per tornare dal servizio di interruzione al programma principale

Interruptè il metodo per creare un arresto temporaneo durante l'esecuzione del programma e consente ai dispositivi periferici di accedere al microprocessore. Il microprocessore risponde a quell'interruzione con unISR (Interrupt Service Routine), che è un breve programma per istruire il microprocessore su come gestire l'interruzione.

L'immagine seguente mostra i tipi di interrupt che abbiamo in un microprocessore 8086 -

Interrupt hardware

L'interruzione hardware è causata da qualsiasi dispositivo periferico inviando un segnale attraverso un pin specificato al microprocessore.

L'8086 ha due pin di interrupt hardware, cioè NMI e INTR. NMI è un interrupt non mascherabile e INTR è un interrupt mascherabile con priorità inferiore. Un altro pin di interrupt associato è INTA chiamato riconoscimento dell'interrupt.

NMI

È un singolo pin di interrupt non mascherabile (NMI) con priorità più alta del pin di richiesta di interrupt mascherabile (INTR) ed è di tipo 2 interrupt.

Quando viene attivato questo interrupt, vengono eseguite queste azioni:

Completa l'istruzione corrente in corso.

Inserisce i valori del registro Flag nello stack.

Inserisce nello stack il valore CS (segmento di codice) e il valore IP (puntatore dell'istruzione) dell'indirizzo di ritorno.

L'IP viene caricato dal contenuto della posizione della parola 00008H.

CS viene caricato dal contenuto della posizione della parola successiva 0000AH.

Il flag di interrupt e il flag trap vengono reimpostati su 0.

INTR

L'INTR è un interrupt mascherabile perché il microprocessore verrà interrotto solo se gli interrupt sono abilitati utilizzando l'istruzione set interrupt flag. Non dovrebbe essere abilitato usando l'istruzione Clear interrupt Flag.

L'interrupt INTR viene attivato da una porta I / O. Se l'interrupt è abilitato e NMI è disabilitato, il microprocessore completa prima l'esecuzione corrente e invia due volte "0" sul pin INTA. Il primo "0" significa che INTA informa il dispositivo esterno di prepararsi e durante il secondo "0" il microprocessore riceve gli 8 bit, diciamo X, dal controller di interrupt programmabile.

Queste azioni vengono eseguite dal microprocessore:

Prima completa l'istruzione corrente.

Attiva l'uscita INTA e riceve il tipo di interrupt, ad esempio X.

Il valore del registro flag, il valore CS dell'indirizzo di ritorno e il valore IP dell'indirizzo di ritorno vengono inseriti nello stack.

Il valore IP viene caricato dal contenuto della posizione della parola X × 4

CS viene caricato dal contenuto della posizione della parola successiva.

Il flag di interrupt e il flag trap vengono reimpostati su 0

Interruzioni software

Alcune istruzioni vengono inserite nella posizione desiderata nel programma per creare interruzioni. Queste istruzioni di interrupt possono essere utilizzate per testare il funzionamento di vari gestori di interrupt. Include:

INT- Istruzione di interrupt con numero di tipo

È un'istruzione a 2 byte. Il primo byte fornisce il codice operativo e il secondo byte fornisce il numero del tipo di interrupt. Ci sono 256 tipi di interrupt in questo gruppo.

La sua esecuzione include i seguenti passaggi:

Il valore del registro flag viene inserito nello stack.

Il valore CS dell'indirizzo di ritorno e il valore IP dell'indirizzo di ritorno vengono inseriti nello stack.

L'IP viene caricato dal contenuto della parola location 'type number' × 4

CS viene caricato dal contenuto della posizione della parola successiva.

Flag di interruzione e Flag di trap vengono reimpostati su 0

L'indirizzo iniziale per l'interrupt di tipo 0 è 000000H, per l'interrupt di tipo1 è 00004H allo stesso modo per il tipo2 è 00008H e …… così via. I primi cinque puntatori sono puntatori di interrupt dedicati. cioè -

TYPE 0 l'interrupt rappresenta la divisione per zero situazione.

TYPE 1 l'interrupt rappresenta l'esecuzione in un unico passaggio durante il debug di un programma.

TYPE 2 l'interrupt rappresenta un interrupt NMI non mascherabile.

TYPE 3 interrupt rappresenta l'interruzione del punto di interruzione.

TYPE 4 l'interrupt rappresenta l'interrupt di overflow.

Gli interrupt dal tipo 5 al tipo 31 sono riservati ad altri microprocessori avanzati e gli interrupt dal 32 al tipo 255 sono disponibili per gli interrupt hardware e software.

INT Istruzione di interruzione a 3 punti di interruzione

È un'istruzione da 1 byte con codice operativo CCH. Queste istruzioni vengono inserite nel programma in modo che quando il processore vi raggiunge, interrompe la normale esecuzione del programma e segue la procedura del punto di interruzione.

La sua esecuzione include i seguenti passaggi:

Il valore del registro flag viene inserito nello stack.

Il valore CS dell'indirizzo di ritorno e il valore IP dell'indirizzo di ritorno vengono inseriti nello stack.

L'IP viene caricato dal contenuto della posizione della parola 3 × 4 = 0000CH

CS viene caricato dal contenuto della posizione della parola successiva.

Flag di interruzione e Flag di trap vengono reimpostati su 0

INTO - Interruzione su istruzione di overflow

È un'istruzione di 1 byte e il loro mnemonico INTO. Il codice operativo per questa istruzione è CEH. Come suggerisce il nome, è un'istruzione di interrupt condizionale, cioè è attiva solo quando il flag di overflow è impostato su 1 e si dirama al gestore di interrupt il cui numero di tipo di interrupt è 4. Se il flag di overflow viene ripristinato, l'esecuzione continua al prossima istruzione.

La sua esecuzione include i seguenti passaggi:

I valori del registro flag vengono inseriti nello stack.

Il valore CS dell'indirizzo di ritorno e il valore IP dell'indirizzo di ritorno vengono inseriti nello stack.

L'IP viene caricato dal contenuto della posizione della parola 4 × 4 = 00010H

CS viene caricato dal contenuto della posizione della parola successiva.

Il flag di interrupt e il flag di trap vengono reimpostati su 0

I diversi modi in cui un operando sorgente è indicato in un'istruzione sono noti come addressing modes. Ci sono 8 diverse modalità di indirizzamento nella programmazione 8086 -

Modalità di indirizzamento immediato

La modalità di indirizzamento in cui l'operando dei dati fa parte dell'istruzione stessa è nota come modalità di indirizzamento immediato.

Esempio

MOV CX, 4929 H, ADD AX, 2387 H, MOV AL, FFHRegistra la modalità di indirizzamento

Significa che il registro è la sorgente di un operando per un'istruzione.

Esempio

MOV CX, AX ; copies the contents of the 16-bit AX register into

; the 16-bit CX register),

ADD BX, AXModalità di indirizzamento diretto

La modalità di indirizzamento in cui l'indirizzo effettivo della posizione di memoria viene scritto direttamente nell'istruzione.

Esempio

MOV AX, [1592H], MOV AL, [0300H]Registra la modalità di indirizzamento indiretto

Questa modalità di indirizzamento consente ai dati di essere indirizzati in qualsiasi posizione di memoria tramite un indirizzo di offset contenuto in uno dei seguenti registri: BP, BX, DI e SI.

Esempio

MOV AX, [BX] ; Suppose the register BX contains 4895H, then the contents

; 4895H are moved to AX

ADD CX, {BX}Modalità di indirizzamento basata

In questa modalità di indirizzamento, l'indirizzo di offset dell'operando è dato dalla somma dei contenuti dei registri BX / BP e dello spostamento a 8 bit / 16 bit.

Esempio

MOV DX, [BX+04], ADD CL, [BX+08]Modalità di indirizzamento indicizzato

In questa modalità di indirizzamento, l'indirizzo di offset degli operandi viene trovato aggiungendo il contenuto del registro SI o DI e gli spostamenti a 8 bit / 16 bit.

Esempio

MOV BX, [SI+16], ADD AL, [DI+16]Modalità di indirizzamento basato su indice

In questa modalità di indirizzamento, l'indirizzo di offset dell'operando viene calcolato sommando il registro di base al contenuto di un registro di indice.

Esempio

ADD CX, [AX+SI], MOV AX, [AX+DI]Basato indicizzato con modalità di spostamento

In questa modalità di indirizzamento, l'offset degli operandi viene calcolato aggiungendo il contenuto del registro di base. Un indice registra i contenuti e lo spostamento a 8 o 16 bit.

Esempio

MOV AX, [BX+DI+08], ADD CX, [BX+SI+16]Multiprocessore indica un insieme multiplo di processori che esegue le istruzioni contemporaneamente. Sono disponibili tre configurazioni multiprocessore di base.

- Configurazione del coprocessore

- Configurazione strettamente accoppiata

- Configurazione liberamente accoppiata

Configurazione del coprocessore

Un coprocessore è un circuito appositamente progettato sul chip del microprocessore che può eseguire molto rapidamente lo stesso compito che il microprocessore esegue. Riduce il carico di lavoro del processore principale. Il coprocessore condivide la stessa memoria, sistema IO, bus, logica di controllo e generatore di clock. Il coprocessore gestisce compiti specializzati come calcoli matematici, visualizzazione grafica sullo schermo, ecc.

L'8086 e l'8088 possono eseguire la maggior parte delle operazioni ma il loro set di istruzioni non è in grado di eseguire operazioni matematiche complesse, quindi in questi casi il microprocessore richiede il coprocessore matematico come il coprocessore matematico Intel 8087, che può eseguire facilmente queste operazioni molto rapidamente.

Schema a blocchi della configurazione del coprocessore

Come sono collegati il coprocessore e il processore?

Il coprocessore e il processore sono collegati tramite i segnali TEST, RQ- / GT- e QS 0 e QS 1 .

Il segnale TEST è collegato al pin BUSY del coprocessore e i restanti 3 pin sono collegati ai 3 pin del coprocessore con lo stesso nome.

Il segnale TEST si occupa dell'attività del coprocessore, cioè il coprocessore è occupato o inattivo.

RT- / GT-viene utilizzato per l'arbitrato del bus.

Il coprocessore utilizza QS 0 e QS 1 per tenere traccia dello stato della coda del processore host.

Configurazione ad accoppiamento stretto

La configurazione strettamente accoppiata è simile alla configurazione del coprocessore, ovvero condividono entrambi la stessa memoria, bus di sistema I / O, logica di controllo e generatore di controllo con il processore host. Tuttavia, il coprocessore e il processore host recuperano ed eseguono le proprie istruzioni. Il bus di sistema è controllato indipendentemente dal coprocessore e dal processore host.

Diagramma a blocchi della configurazione strettamente accoppiata

Come sono collegati il processore e il processore indipendente?

La comunicazione tra l'host e il processore indipendente avviene tramite lo spazio di memoria.

Nessuna delle istruzioni viene utilizzata per la comunicazione, come WAIT, ESC, ecc.

Il processore host gestisce la memoria e riattiva il processore indipendente inviando comandi a una delle sue porte.

Quindi il processore indipendente accede alla memoria per eseguire l'attività.

Dopo il completamento dell'attività, invia un riconoscimento al processore host utilizzando il segnale di stato o una richiesta di interruzione.

Configurazione ad accoppiamento lasco

La configurazione ad accoppiamento libero è costituita dal numero di moduli dei sistemi basati su microprocessore, che sono collegati tramite un bus di sistema comune. Ogni modulo è costituito dal proprio generatore di clock, memoria, dispositivi I / O e sono collegati tramite un bus locale.

Schema a blocchi della configurazione ad accoppiamento lasco

Vantaggi

Avere più di un processore si traduce in una maggiore efficienza.

Ciascuno dei processori ha il proprio bus locale per accedere alla memoria locale / ai dispositivi I / O. Ciò semplifica il raggiungimento dell'elaborazione parallela.

La struttura del sistema è flessibile, ovvero il guasto di un modulo non influisce sull'intero guasto del sistema; il modulo difettoso può essere sostituito in seguito.

Il processore di dati numerici 8087 è anche noto come Math co-processor, Numeric processor extension e Floating point unit. È stato il primo coprocessore matematico progettato da Intel per l'accoppiamento con 8086/8088 risultando in un calcolo più semplice e veloce.

Una volta che le istruzioni sono state identificate dal processore 8086/8088, vengono assegnate al coprocessore 8087 per un'ulteriore esecuzione.

I tipi di dati supportati da 8087 sono:

- Numeri interi binari

- Numeri decimali imballati

- Numeri reali

- Formato reale temporaneo

Le caratteristiche più importanti del processore di dati numerici 8087 sono le seguenti:

Supporta dati di tipo integer, float e real che vanno da 2 a 10 byte.

La velocità di elaborazione è così elevata che può calcolare la moltiplicazione di due numeri reali a 64 bit in ~ 27 µs e può anche calcolare la radice quadrata in ~ 35 µs.

Segue gli standard in virgola mobile IEEE.

8087 Architecture

8087 Architecture è diviso in due gruppi, ovvero Control Unit (CU) e Numeric Extension Unit (NEU).

Il control unit gestisce tutta la comunicazione tra il processore e la memoria come riceve e decodifica istruzioni, legge e scrive operandi di memoria, mantiene la coda parallela, ecc. Tutte le istruzioni del coprocessore sono istruzioni ESC, cioè iniziano con 'F', il solo coprocessore esegue le istruzioni ESC mentre le altre istruzioni vengono eseguite dal microprocessore.

Il numeric extension unitgestisce tutte le istruzioni del processore numerico come le istruzioni aritmetiche, logiche, trascendentali e di trasferimento dati. Ha 8 stack di registri, che contengono gli operandi per le istruzioni ei loro risultati.

L'architettura del coprocessore 8087 è la seguente:

Descrizione pin 8087

Diamo prima un'occhiata al diagramma dei pin di 8087 -

Il seguente elenco fornisce la descrizione dei pin di 8087 -

AD0 – AD15 - Queste sono le linee di indirizzo / dati multiplexate nel tempo, che trasportano indirizzi durante il primo ciclo di clock e dati dal secondo ciclo di clock in poi.

A19 / S6 – A16/S- Queste righe sono le righe indirizzo / stato multiplexate nel tempo. Funziona in modo simile ai corrispondenti pin di 8086. S 6 , S 4 e S3 sono permanentemente alti, mentre S 5 è permanentemente basso.

$\overline{BHE}$/S7 - Durante il primo ciclo di clock, il $\overline{BHE}$/ S 7 viene utilizzato per abilitare i dati sul byte più alto del bus dati 8086 e successivamente funziona come linea di stato S 7 .

QS1, QS0 - Questi sono segnali di ingresso di stato della coda che forniscono lo stato della coda di istruzioni, le loro condizioni come mostrato nella tabella seguente -

| QS 0 | QS 1 | Stato |

|---|---|---|

| 0 | 0 | Nessuna operazione |

| 0 | 1 | Primo byte di codice operativo dalla coda |

| 1 | 0 | Svuota la coda |

| 1 | 1 | Byte successivo dalla coda |

INT - È un segnale di interruzione, che diventa alto quando viene ricevuta un'eccezione non mascherata durante l'esecuzione.

BUSY - È un segnale di uscita, quando è alto indica uno stato occupato alla CPU.

READY - È un segnale di ingresso utilizzato per informare il coprocessore se il bus è pronto a ricevere dati oppure no.

RESET - È un segnale di ingresso utilizzato per rifiutare le attività interne del coprocessore e prepararlo per un'ulteriore esecuzione quando richiesto dalla CPU.

CLK - L'ingresso CLK fornisce le temporizzazioni di base per il funzionamento del processore.

VCC - È un segnale di alimentazione, che richiede un'alimentazione di + 5V per il funzionamento del circuito.

S0, S1, S2- Questi sono i segnali di stato che forniscono lo stato dell'operazione che viene utilizzato dal Bus Controller 8087 per generare memoria e segnali di controllo I / O. Questi segnali sono attivi durante il quarto ciclo di clock.

| S 2 | S 1 | S 0 | Stato della coda |

|---|---|---|---|

| 0 | X | X | Inutilizzato |

| 1 | 0 | 0 | Inutilizzato |

| 1 | 0 | 1 | Lettura della memoria |

| 1 | 1 | 0 | Scrittura in memoria |

| 1 | 1 | 1 | Passivo |

RQ/GT1 & RQ/GT0 - Questi sono i file Request/Grant segnali utilizzati dai processori 8087 per ottenere il controllo del bus dal processore host 8086/8088 per i trasferimenti di operandi.

In questo capitolo, discuteremo di interfaccia di memoria e interfaccia di I / O con 8085.

Interfaceè il percorso per la comunicazione tra due componenti. L'interfacciamento è di due tipi, interfaccia di memoria e interfaccia di I / O.

Interfaccia di memoria

Quando stiamo eseguendo un'istruzione, abbiamo bisogno che il microprocessore acceda alla memoria per leggere i codici di istruzione e i dati memorizzati nella memoria. Per questo, sia la memoria che il microprocessore richiedono alcuni segnali da leggere e scrivere nei registri.

Il processo di interfacciamento include alcuni fattori chiave da abbinare ai requisiti di memoria e ai segnali del microprocessore. Il circuito di interfaccia, quindi, dovrebbe essere progettato in modo tale che corrisponda ai requisiti del segnale di memoria con i segnali del microprocessore.

Interfacciamento IO

Esistono vari dispositivi di comunicazione come la tastiera, il mouse, la stampante, ecc. Quindi, è necessario interfacciare la tastiera e altri dispositivi con il microprocessore utilizzando latch e buffer. Questo tipo di interfaccia è noto come interfaccia I / O.

Diagramma a blocchi di memoria e interfaccia I / O

8085 perni di interfacciamento

Di seguito è riportato l'elenco dei 8085 pin utilizzati per l'interfacciamento con altri dispositivi:

- A 15 - A 8 (bus indirizzi superiori)

- AD 7 - AD 0 (indirizzo inferiore / bus dati)

- ALE

- RD

- WR

- READY

Modi di comunicazione - Microprocessore con il mondo esterno?

Esistono due modi di comunicazione in cui il microprocessore può connettersi con il mondo esterno.

- Interfaccia di comunicazione seriale

- Interfaccia di comunicazione parallela

Serial Communication Interface - In questo tipo di comunicazione, l'interfaccia riceve un singolo byte di dati dal microprocessore e lo invia bit per bit all'altro sistema in modo seriale e viceversa.

Parallel Communication Interface - In questo tipo di comunicazione, l'interfaccia riceve un byte di dati dal microprocessore e lo invia bit per bit agli altri sistemi in modo simultaneo (o) parallelo e viceversa.

Il controller programmabile per tastiera / display 8279 è progettato da Intel che interfaccia una tastiera con la CPU. La tastiera esegue prima la scansione della tastiera e identifica se è stato premuto un tasto. Quindi invia la relativa risposta del tasto premuto alla CPU e viceversa.

In quanti modi la tastiera è interfacciata con la CPU?

La tastiera può essere interfacciata sia in modalità interrupt che polled. NelInterrupt mode, al processore viene richiesto il servizio solo se viene premuto un tasto qualsiasi, altrimenti la CPU continuerà con il suo compito principale.

Nel Polled mode, la CPU legge periodicamente un flag interno di 8279 per verificare se viene premuto o meno un tasto con la pressione del tasto.

Come funziona la tastiera 8279?

La tastiera è composta da un massimo di 64 tasti, che si interfacciano con la CPU tramite i codici dei tasti. Questi codici chiave vengono rimossi dal bounce e memorizzati in una FIFORAM a 8 byte, a cui può accedere la CPU. Se nel FIFO vengono immessi più di 8 caratteri, significa che vengono premuti più di otto tasti alla volta. Questo è quando viene impostato lo stato di overrun.

Se un FIFO contiene una voce di chiave valida, la CPU viene interrotta in modalità interrupt altrimenti la CPU controlla lo stato in polling per leggere la voce. Una volta che la CPU legge un'immissione di chiave, il FIFO viene aggiornato e l'immissione di chiave viene espulsa dal FIFO per generare spazio per nuove voci.

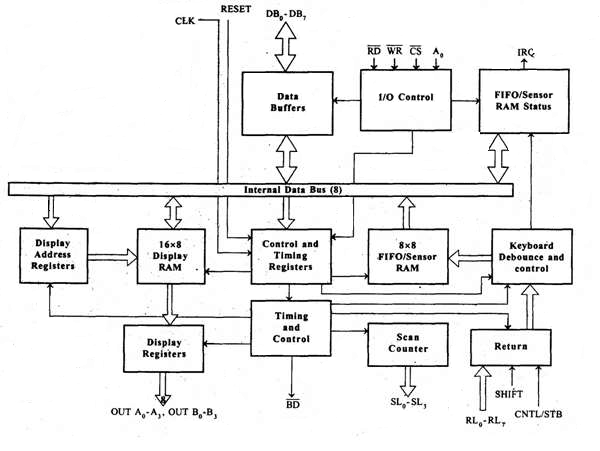

Architettura e descrizione

Controllo I / O e buffer dati

Questa unità controlla il flusso di dati attraverso il microprocessore. È abilitato solo quando D è basso. Il suo buffer dati interfaccia il bus esterno del sistema con il bus interno del microprocessore. I pin A0, RD e WR vengono utilizzati per operazioni di comando, stato o lettura / scrittura dei dati.

Registro di controllo e temporizzazione e controllo della temporizzazione

Questa unità contiene registri per memorizzare la tastiera, le modalità di visualizzazione e altre operazioni programmate dalla CPU. La centralina di temporizzazione e controllo gestisce le temporizzazioni per il funzionamento del circuito.

Contatore di scansione

Ha due modalità, ad es Encoded modee modalità decodificata. Nella modalità codificata, il contatore fornisce il conteggio binario che deve essere decodificato esternamente per fornire le linee di scansione per la tastiera e il display.

Nel decoded scan mode, il contatore decodifica internamente i 2 bit meno significativi e fornisce una scansione decodificata 1 su 4 su SL 0 -SL 3 .

Buffer di ritorno, antirimbalzo della tastiera e controllo

Questa unità esegue prima la scansione della chiusura della chiave per riga, se trovata, l'unità antirimbalzo della tastiera rimuove l'immissione della chiave. Nel caso in cui venga rilevata la stessa chiave, il codice di quella chiave viene trasferito direttamente alla RAM del sensore insieme allo stato della chiave SHIFT & CONTROL.

FIFO / Sensor RAM e Status Logic

Questa unità funge da RAM FIFO (first-in-first-out) a 8 byte in cui il codice chiave di ogni tasto premuto viene inserito nella RAM secondo la loro sequenza. La logica di stato genera una richiesta di interruzione dopo ogni operazione di lettura FIFO finché il FIFO non si svuota.

Nella modalità matrice del sensore scansionata, questa unità funge da RAM del sensore in cui ogni riga viene caricata con lo stato della riga corrispondente di sensori nella matrice. Quando il sensore cambia il suo stato, la linea IRQ diventa alta e interrompe la CPU.

Visualizza i registri degli indirizzi e visualizza la RAM

Questa unità è costituita da registri degli indirizzi di visualizzazione che contengono gli indirizzi della parola attualmente letta / scritta dalla CPU nella / dalla RAM del display.

8279 - Descrizione pin

La figura seguente mostra il diagramma dei pin di 8279 -

Linee bus dati, DB 0 - DB 7

Si tratta di 8 linee bus dati bidirezionali utilizzate per trasferire i dati alla / dalla CPU.

CLK

L'ingresso di clock viene utilizzato per generare le temporizzazioni interne richieste dal microprocessore.

RIPRISTINA

Come suggerisce il nome, questo pin viene utilizzato per ripristinare il microprocessore.

CS Chip Select

Quando questo pin è impostato su basso, consente operazioni di lettura / scrittura, altrimenti questo pin dovrebbe essere impostato su alto.

A 0

Questo pin indica il trasferimento delle informazioni di comando / stato. Quando è basso, indica il trasferimento di dati.

RD, WR

Questo pin di lettura / scrittura consente al buffer di dati di inviare / ricevere dati sul bus dati.

IRQ

Questa linea di uscita di interrupt diventa alta quando sono presenti dati nella RAM del sensore FIFO. La linea di interrupt diventa bassa con ogni operazione di lettura della RAM FIFO. Tuttavia, se la RAM FIFO contiene ulteriormente qualsiasi voce di codice chiave che deve essere letta dalla CPU, questo pin torna alto per generare un interrupt alla CPU.

V ss , V cc

Queste sono le linee di massa e di alimentazione del microprocessore.

SL 0 - SL 3

Queste sono le linee di scansione utilizzate per scansionare la matrice della tastiera e visualizzare le cifre. Queste linee possono essere programmate come codificate o decodificate, utilizzando il registro di controllo della modalità.

RL 0 - RL 7

Queste sono le linee di ritorno che sono collegate a un terminale di chiavi, mentre l'altro terminale delle chiavi è collegato alle linee di scansione decodificate. Queste righe sono impostate su 0 quando viene premuto un tasto qualsiasi.

CAMBIO

Lo stato della riga di input Shift viene memorizzato insieme a ogni codice tasto in FIFO nella modalità tastiera scansionata. Finché non viene abbassato con una chiusura a chiave, viene tirato verso l'alto internamente per mantenerlo alto

CNTL / STB - Modalità CONTROL / STROBED I / P

In modalità tastiera, questa riga viene utilizzata come ingresso di controllo e memorizzata in FIFO alla chiusura di un tasto. La linea è una linea stroboscopica che immette i dati nella RAM FIFO, nella modalità di immissione in modalità strobo. Ha un pull up interno. La linea si abbassa con una chiusura a chiave.

BD

Sta per display vuoto. Viene utilizzato per oscurare il display durante la commutazione delle cifre.

OUTA 0 - OUTA 3 e OUTB 0 - OUTB 3

Queste sono le porte di uscita per due registri interni di aggiornamento del display 16x4 o 16x8. I dati di queste linee vengono sincronizzati con le linee di scansione per eseguire la scansione del display e della tastiera.

Modalità operative di 8279

Ci sono due modalità di funzionamento sull'8279: Input Mode e Output Mode.

Modalità di immissione

Questa modalità si occupa dell'input fornito dalla tastiera e questa modalità è ulteriormente classificata in 3 modalità.

Scanned Keyboard Mode- In questa modalità, la matrice di chiavi può essere interfacciata utilizzando scansioni codificate o decodificate. Nella scansione codificata, una tastiera 8 × 8 o nella scansione decodificata, può essere interfacciata una tastiera 4 × 8. Il codice del tasto premuto con SHIFT e lo stato CONTROL viene memorizzato nella FIFO RAM.

Scanned Sensor Matrix- In questa modalità, un array di sensori può essere interfacciato con il processore utilizzando scansioni encoder o decoder. Nella scansione encoder, è possibile interfacciare la matrice del sensore 8 × 8 o con la scansione del decoder la matrice del sensore 4 × 8.

Strobed Input - In questa modalità, quando la linea di controllo è impostata a 0, i dati sulle linee di ritorno vengono memorizzati nel FIFO byte per byte.

Modalità di uscita

Questa modalità si occupa delle operazioni relative alla visualizzazione. Questa modalità è ulteriormente classificata in due modalità di output.

Display Scan - Questa modalità consente di organizzare i display multiplex da 8/16 caratteri come unità di visualizzazione doppie a 4 bit / singole a 8 bit.

Display Entry - Questa modalità consente di inserire i dati per la visualizzazione sia dal lato destro che dal lato sinistro.

DMA è l'acronimo di Direct Memory Access. È progettato da Intel per trasferire i dati alla velocità più elevata. Consente al dispositivo di trasferire i dati direttamente dalla / alla memoria senza alcuna interferenza della CPU.

Utilizzando un controller DMA, il dispositivo richiede alla CPU di conservare i suoi dati, indirizzo e bus di controllo, quindi il dispositivo è libero di trasferire dati direttamente da / verso la memoria. Il trasferimento dei dati DMA viene avviato solo dopo aver ricevuto il segnale HLDA dalla CPU.

Come vengono eseguite le operazioni DMA?

Di seguito è riportata la sequenza delle operazioni eseguite da un DMA:

Inizialmente, quando un dispositivo deve inviare dati tra il dispositivo e la memoria, il dispositivo deve inviare una richiesta DMA (DRQ) al controller DMA.

Il controller DMA invia una richiesta di sospensione (HRQ) alla CPU e attende che la CPU asserisca l'HLDA.

Quindi il microprocessore triplica tutti i bus dati, bus indirizzi e bus di controllo. La CPU lascia il controllo sul bus e conferma la richiesta HOLD tramite il segnale HLDA.

Ora la CPU è in stato HOLD e il controller DMA deve gestire le operazioni sui bus tra CPU, memoria e dispositivi I / O.

Caratteristiche di 8257

Ecco un elenco di alcune delle caratteristiche principali di 8257:

Dispone di quattro canali che possono essere utilizzati su quattro dispositivi I / O.

Ogni canale ha un indirizzo a 16 bit e un contatore a 14 bit.

Ogni canale può trasferire dati fino a 64kb.

Ogni canale può essere programmato indipendentemente.

Ogni canale può eseguire il trasferimento in lettura, il trasferimento in scrittura e verificare le operazioni di trasferimento.

Genera il segnale MARK al dispositivo periferico che 128 byte sono stati trasferiti.

Richiede un orologio monofase.

La sua frequenza varia da 250Hz a 3MHz.

Funziona in 2 modalità, ovvero Master mode e Slave mode.

8257 Architecture

L'immagine seguente mostra l'architettura di 8257 -

Descrizione pin 8257

L'immagine seguente mostra il diagramma dei pin di un controller DMA 8257 -

DRQ 0 −DRQ3

Questi sono i quattro ingressi di richiesta DMA dei canali individuali, che vengono utilizzati dai dispositivi periferici per l'utilizzo dei servizi DMA. Quando è selezionata la modalità a priorità fissa, DRQ 0 ha la priorità più alta e DRQ 3 ha la priorità più bassa tra di loro.

DACK o - DACK 3