마이크로 프로세서-퀵 가이드

마이크로 프로세서는 ALU (Arithmetic Logical Unit) 작업을 수행하고 여기에 연결된 다른 장치와 통신 할 수있는 작은 칩으로 제작 된 마이크로 컴퓨터의 제어 장치입니다.

마이크로 프로세서는 ALU, 레지스터 어레이 및 제어 장치로 구성됩니다. ALU는 메모리 또는 입력 장치에서받은 데이터에 대해 산술 및 논리 연산을 수행합니다. 레지스터 배열은 B, C, D, E, H, L 및 누산기와 같은 문자로 식별되는 레지스터로 구성됩니다. 제어 장치는 컴퓨터 내의 데이터 및 지침의 흐름을 제어합니다.

기본 마이크로 컴퓨터의 블록 다이어그램

마이크로 프로세서는 어떻게 작동합니까?

마이크로 프로세서는 Fetch, Decode, Execute의 순서를 따릅니다.

처음에는 명령이 순차적으로 메모리에 저장됩니다. 마이크로 프로세서는 메모리에서 해당 명령어를 가져온 다음이를 디코딩하고 STOP 명령어에 도달 할 때까지 해당 명령어를 실행합니다. 나중에 결과를 이진 형식으로 출력 포트로 보냅니다. 이러한 프로세스 사이에서 레지스터는 임시 데이터를 저장하고 ALU는 컴퓨팅 기능을 수행합니다.

마이크로 프로세서에서 사용되는 용어 목록

다음은 마이크로 프로세서에서 자주 사용되는 용어 목록입니다.

Instruction Set − 마이크로 프로세서가 이해할 수있는 일련의 명령어입니다.

Bandwidth − 단일 명령어에서 처리되는 비트 수입니다.

Clock Speed− 프로세서가 수행 할 수있는 초당 작업 수를 결정합니다. 메가 헤르츠 (MHz) 또는 기가 헤르츠 (GHz)로 표시되며 클럭 속도라고도합니다.

Word Length− 내부 데이터 버스, 레지스터, ALU 등의 너비에 따라 다릅니다. 8 비트 마이크로 프로세서는 한 번에 8 비트 데이터를 처리 할 수 있습니다. 단어 길이는 마이크로 컴퓨터의 유형에 따라 4 비트에서 64 비트까지 다양합니다.

Data Types − 마이크로 프로세서에는 이진, BCD, ASCII, 부호있는 숫자 및 부호없는 숫자와 같은 여러 데이터 유형 형식이 있습니다.

마이크로 프로세서의 특징

다음은 모든 마이크로 프로세서의 가장 두드러진 기능 목록입니다.

Cost-effective − 마이크로 프로세서 칩은 저렴한 가격으로 제공되며 그 결과 비용이 저렴합니다.

Size − 마이크로 프로세서는 작은 크기의 칩이므로 휴대가 가능합니다.

Low Power Consumption − 마이크로 프로세서는 전력 소모가 적은 금속 산화물 반도체 기술을 사용하여 제조됩니다.

Versatility − 마이크로 프로세서는 소프트웨어 프로그램을 구성하여 여러 응용 프로그램에서 동일한 칩을 사용할 수 있기 때문에 다목적입니다.

Reliability − 마이크로 프로세서의 IC 고장률이 매우 낮으므로 신뢰할 수 있습니다.

마이크로 프로세서는 세 가지 범주로 분류 할 수 있습니다.

RISC 프로세서

RISC는 Reduced Instruction Set Computer. 컴퓨터의 명령어 세트를 단순화하여 실행 시간을 단축하도록 설계되었습니다. RISC 프로세서를 사용하면 각 명령어는 실행 시간이 균일 한 결과를 실행하는 데 단 하나의 클럭 사이클 만 필요합니다. 이렇게하면 코드 줄이 많아 지므로 효율성이 감소하므로 명령을 저장하는 데 더 많은 RAM이 필요합니다. 컴파일러는 또한 고급 언어 명령을 기계 코드로 변환하기 위해 더 많은 작업을해야합니다.

RISC 프로세서 중 일부는-

- 파워 PC : 601, 604, 615, 620

- DEC 알파 : 210642, 211066, 21068, 21164

- MIPS : TS (R10000) RISC 프로세서

- PA-RISC : HP 7100LC

RISC의 아키텍처

RISC 마이크로 프로세서 아키텍처는 고도로 최적화 된 명령어 세트를 사용합니다. 전력 효율성으로 인해 Apple iPod과 같은 휴대용 장치에 사용됩니다.

RISC의 특징

RISC 프로세서의 주요 특징은 다음과 같습니다.

간단한 지침으로 구성됩니다.

다양한 데이터 형식을 지원합니다.

파이프 라이닝을 위해 간단한 주소 지정 모드와 고정 길이 명령을 사용합니다.

모든 컨텍스트에서 사용할 레지스터를 지원합니다.

한 사이클 실행 시간.

"LOAD"및 "STORE"명령은 메모리 위치에 액세스하는 데 사용됩니다.

더 많은 수의 레지스터로 구성됩니다.

적은 수의 트랜지스터로 구성됩니다.

CISC 프로세서

CISC는 Complex Instruction Set Computer. 명령어 당 사이클 수를 무시하고 프로그램 당 명령어 수를 최소화하도록 설계되었습니다. 복잡한 명령을 하드웨어에 직접 구축하는 데 중점을 둡니다.

컴파일러는 코드의 길이가 비교적 짧기 때문에 고수준 언어를 어셈블리 수준 언어 / 기계 코드로 변환하는 작업을 거의 수행하지 않아도되므로 명령어를 저장하는 데 RAM이 거의 필요하지 않습니다.

CISC 프로세서 중 일부는-

- IBM 370/168

- VAX 11/780

- 인텔 80486

CISC의 아키텍처

이 아키텍처는 더 큰 프로그램에 더 많은 스토리지가 필요하여 메모리 비용이 높아지기 때문에 메모리 비용을 줄 이도록 설계되었습니다. 이를 해결하기 위해 단일 명령어에 연산 수를 포함하여 프로그램 당 명령어 수를 줄일 수 있습니다.

CISC의 특징

- 다양한 주소 지정 모드.

- 더 많은 수의 명령.

- 다양한 길이의 명령어 형식.

- 하나의 명령어를 실행하려면 여러 사이클이 필요할 수 있습니다.

- 명령어 디코딩 로직은 복잡합니다.

- 여러 주소 지정 모드를 지원하려면 하나의 명령어가 필요합니다.

특수 프로세서

이들은 특별한 목적을 위해 설계된 프로세서입니다. 몇 가지 특수 프로세서에 대해 간략하게 설명합니다.

보조 프로세서

코 프로세서는 특수 설계된 마이크로 프로세서로, 일반 마이크로 프로세서보다 몇 배 더 빠르게 특정 기능을 처리 할 수 있습니다.

For example − 수학 보조 프로세서.

일부 인텔 수학 보조 프로세서는 다음과 같습니다.

- 8087-8086과 함께 사용

- 80287-80286과 함께 사용

- 80387-80386과 함께 사용

입력 / 출력 프로세서

그것은 최소한의 CPU 개입으로 I / O 장치를 제어하는 데 사용되는 자체 로컬 메모리를 가진 특별히 설계된 마이크로 프로세서입니다.

For example −

- DMA (직접 메모리 액세스) 컨트롤러

- 키보드 / 마우스 컨트롤러

- 그래픽 디스플레이 컨트롤러

- SCSI 포트 컨트롤러

Transputer (트랜지스터 컴퓨터)

변환기는 자체 로컬 메모리가 있고 프로세서 간 통신을 위해 하나의 변환기를 다른 변환기에 연결하는 링크가있는 특수 설계된 마이크로 프로세서입니다. Inmos가 1980 년에 처음 설계했으며 VLSI 기술 활용을 목표로합니다.

트랜스 퓨터는 단일 프로세서 시스템으로 사용하거나 외부 링크에 연결하여 건설 비용을 줄이고 성능을 높일 수 있습니다.

For example − 16 비트 T212, 32 비트 T425, 부동 소수점 (T800, T805 및 T9000) 프로세서.

DSP (디지털 신호 프로세서)

이 프로세서는 아날로그 신호를 디지털 형식으로 처리하도록 특별히 설계되었습니다. 이것은 일정한 시간 간격으로 전압 레벨을 샘플링하고 그 순간의 전압을 디지털 형식으로 변환하여 수행됩니다. 이 프로세스는 아날로그-디지털 변환기, A-D 변환기 또는 ADC라고하는 회로에 의해 수행됩니다.

DSP는 다음 구성 요소를 포함합니다-

Program Memory − DSP가 데이터 처리에 사용할 프로그램을 저장합니다.

Data Memory − 처리 할 정보를 저장합니다.

Compute Engine − 프로그램 메모리의 프로그램과 데이터 메모리의 데이터에 액세스하여 수학적 처리를 수행합니다.

Input/Output − 외부 세계와 연결됩니다.

그 응용 프로그램은-

- 사운드 및 음악 합성

- 오디오 및 비디오 압축

- 비디오 신호 처리

- 2D 및 3D 그래픽 가속.

For example − Texas Instruments의 TMS 320 시리즈 (예 : TMS 320C40, TMS320C50).

8085는 "8-8"마이크로 프로세서로 발음됩니다. NMOS 기술을 사용하여 1977 년 Intel에서 설계 한 8 비트 마이크로 프로세서입니다.

다음과 같은 구성이 있습니다.

- 8 비트 데이터 버스

- 최대 64KB 주소를 지정할 수있는 16 비트 주소 버스

- 16 비트 프로그램 카운터

- 16 비트 스택 포인터

- 쌍으로 배열 된 6 개의 8 비트 레지스터 : BC, DE, HL

- 3.2MHz 단상 클록에서 작동하려면 + 5V 전원이 필요합니다.

세탁기, 전자 레인지, 휴대폰 등에 사용됩니다.

8085 마이크로 프로세서 – 기능 유닛

8085는 다음과 같은 기능 단위로 구성됩니다.

어큐뮬레이터

산술, 논리, I / O 및 LOAD / STORE 작업을 수행하는 데 사용되는 8 비트 레지스터입니다. 내부 데이터 버스 및 ALU에 연결됩니다.

산술 및 논리 장치

이름에서 알 수 있듯이 8 비트 데이터에 대해 더하기, 빼기, AND, OR 등과 같은 산술 및 논리 연산을 수행합니다.

범용 레지스터

8085 프로세서에는 6 개의 범용 레지스터, 즉 B, C, D, E, H & L이 있습니다. 각 레지스터는 8 비트 데이터를 보유 할 수 있습니다.

이 레지스터는 16 비트 데이터를 보관하기 위해 쌍으로 작동 할 수 있으며 이들의 쌍 조합은 BC, DE 및 HL과 같습니다.

프로그램 카운터

실행할 다음 명령어의 메모리 주소 위치를 저장하는 데 사용되는 16 비트 레지스터입니다. 마이크로 프로세서는 명령어가 실행될 때마다 프로그램을 증가시켜 프로그램 카운터가 실행될 다음 명령어의 메모리 주소를 가리 킵니다.

스택 포인터

또한 16 비트 레지스터는 스택처럼 작동하며 푸시 및 팝 작업 중에 항상 2 씩 증가 / 감소됩니다.

임시 등록

산술 및 논리 연산의 임시 데이터를 보유하는 8 비트 레지스터입니다.

플래그 레지스터

이는 누산기에 저장된 결과에 따라 0 또는 1을 보유하는 5 개의 1 비트 플립 플롭이있는 8 비트 레지스터입니다.

이것들은 5 개의 플립 플롭 세트입니다.

- 표지판)

- 제로 (Z)

- 보조 캐리 (AC)

- 패리티 (P)

- 캐리 (C)

비트 위치는 다음 표에 나와 있습니다.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| 에스 | 지 | AC | 피 | CY |

명령 레지스터 및 디코더

8 비트 레지스터입니다. 명령어가 메모리에서 페치되면 명령어 레지스터에 저장됩니다. 명령어 디코더는 명령어 레지스터에있는 정보를 디코딩합니다.

타이밍 및 제어 장치

마이크로 프로세서에 타이밍 및 제어 신호를 제공하여 작업을 수행합니다. 다음은 외부 및 내부 회로를 제어하는 타이밍 및 제어 신호입니다.

- 제어 신호 : READY, RD ', WR', ALE

- 상태 신호 : S0, S1, IO / M '

- DMA 신호 : HOLD, HLDA

- RESET 신호 : RESET IN, RESET OUT

인터럽트 제어

이름에서 알 수 있듯이 프로세스 중에 인터럽트를 제어합니다. 마이크로 프로세서가 주 프로그램을 실행할 때 인터럽트가 발생할 때마다 마이크로 프로세서는 들어오는 요청을 처리하기 위해 주 프로그램에서 제어를 전환합니다. 요청이 완료되면 제어가 메인 프로그램으로 돌아갑니다.

8085 마이크로 프로세서에는 INTR, RST 7.5, RST 6.5, RST 5.5, TRAP의 5 가지 인터럽트 신호가 있습니다.

직렬 입력 / 출력 제어

SID (시리얼 입력 데이터)와 SOD (시리얼 출력 데이터)의 두 가지 명령어를 사용하여 시리얼 데이터 통신을 제어합니다.

주소 버퍼 및 주소 데이터 버퍼

스택 포인터와 프로그램 카운터에 저장된 내용은 CPU와 통신하기 위해 주소 버퍼와 주소 데이터 버퍼에로드됩니다. 메모리 및 I / O 칩은이 버스에 연결됩니다. CPU는 원하는 데이터를 메모리 및 I / O 칩과 교환 할 수 있습니다.

주소 버스 및 데이터 버스

데이터 버스는 저장할 데이터를 전달합니다. 이는 양방향이지만 주소 버스는 저장되어야하는 위치를 전달하며 단방향입니다. 데이터 및 주소 I / O 장치를 전송하는 데 사용됩니다.

8085 아키텍처

우리는 다음 이미지로 8085의 아키텍처를 묘사하려고했습니다.

다음 이미지는 8085 마이크로 프로세서의 핀 다이어그램을 보여줍니다.

8085 마이크로 프로세서의 핀은 7 개 그룹으로 분류 할 수 있습니다.

주소 버스

A15-A8, 가장 중요한 8 비트 메모리 / IO 주소를 전달합니다.

데이터 버스

AD7-AD0, 최하위 8 비트 주소 및 데이터 버스를 전달합니다.

제어 및 상태 신호

이러한 신호는 작동의 특성을 식별하는 데 사용됩니다. 3 개의 제어 신호와 3 개의 상태 신호가 있습니다.

세 가지 제어 신호는 RD, WR 및 ALE입니다.

RD −이 신호는 선택한 IO 또는 메모리 장치를 읽을 것이며 데이터 버스에서 사용 가능한 데이터를받을 준비가되었음을 나타냅니다.

WR −이 신호는 데이터 버스의 데이터가 선택된 메모리 또는 IO 위치에 기록 될 것임을 나타냅니다.

ALE− 마이크로 프로세서에 의해 새로운 작업이 시작될 때 생성되는 양의 진행 펄스입니다. 펄스가 높으면 주소를 나타냅니다. 펄스가 내려 가면 데이터를 나타냅니다.

세 가지 상태 신호는 IO / M, S0 및 S1입니다.

IO / M

이 신호는 IO와 메모리 작동을 구별하는 데 사용됩니다. 즉, 높으면 IO 작동을 나타내고 낮 으면 메모리 작동을 나타냅니다.

S1 및 S0

이 신호는 현재 작동 유형을 식별하는 데 사용됩니다.

전원 공급

전원 공급 장치 신호에는 VCC 및 VSS가 있습니다. VCC는 + 5v 전원 공급 장치를 나타내고 VSS는 접지 신호를 나타냅니다.

클록 신호

3 개의 클럭 신호, 즉 X1, X2, CLK OUT이 있습니다.

X1, X2− 크리스탈 (RC, LC N / W)이이 두 핀에 연결되어 내부 클록 발생기의 주파수를 설정하는 데 사용됩니다. 이 주파수는 내부적으로 2로 나뉩니다.

CLK OUT −이 신호는 마이크로 프로세서에 연결된 장치의 시스템 클럭으로 사용됩니다.

인터럽트 및 외부에서 시작된 신호

인터럽트는 마이크로 프로세서가 작업을 수행하도록 요청하기 위해 외부 장치가 생성하는 신호입니다. 인터럽트 신호는 TRAP, RST 7.5, RST 6.5, RST 5.5, INTR의 5 가지가 있습니다. 인터럽트에 대해서는 인터럽트 섹션에서 자세히 설명합니다.

INTA − 인터럽트 확인 신호입니다.

RESET IN −이 신호는 프로그램 카운터를 0으로 설정하여 마이크로 프로세서를 재설정하는 데 사용됩니다.

RESET OUT −이 신호는 마이크로 프로세서가 재설정 될 때 연결된 모든 장치를 재설정하는 데 사용됩니다.

READY−이 신호는 장치가 데이터를 송수신 할 준비가되었음을 나타냅니다. READY가 낮 으면 CPU는 READY가 높아질 때까지 기다려야합니다.

HOLD −이 신호는 다른 마스터가 주소 및 데이터 버스의 사용을 요청하고 있음을 나타냅니다.

HLDA (HOLD Acknowledge)− CPU가 HOLD 요청을 수신했으며 다음 클럭 사이클에서 버스를 포기할 것임을 나타냅니다. HOLD 신호가 제거 된 후 HLDA가 로우로 설정됩니다.

직렬 I / O 신호

2 개의 직렬 신호, 즉 SID와 SOD가 있으며 이러한 신호는 직렬 통신에 사용됩니다.

SOD (직렬 출력 데이터 라인) − 출력 SOD는 SIM 명령에 지정된대로 설정 / 리셋됩니다.

SID (직렬 입력 데이터 라인) −이 라인의 데이터는 RIM 명령이 실행될 때마다 누산기에로드됩니다.

이제 8085 마이크로 프로세서의 주소 지정 모드에 대해 설명하겠습니다.

8085의 주소 지정 모드

이는 내용을 변경하지 않고 한 레지스터에서 다른 레지스터로, 메모리에서 레지스터로, 레지스터에서 메모리로 데이터를 전송하는 데 사용되는 명령입니다. 8085의 주소 지정 모드는 5 개 그룹으로 분류됩니다.

즉시 주소 지정 모드

이 모드에서 8/16 비트 데이터는 명령어 자체에 피연산자 중 하나로 지정됩니다. For example: MVI K, 20F : 20F가 레지스터 K에 복사됨을 의미합니다.

주소 지정 모드 등록

이 모드에서 데이터는 한 레지스터에서 다른 레지스터로 복사됩니다. For example: MOV K, B : 레지스터 B의 데이터가 레지스터 K로 복사됨을 의미합니다.

직접 주소 지정 모드

이 모드에서 데이터는 주어진 주소에서 레지스터로 직접 복사됩니다. For example: LDB 5000K : 주소 5000K의 데이터가 레지스터 B에 복사됨을 의미합니다.

간접 주소 지정 모드

이 모드에서 데이터는 레지스터가 가리키는 주소를 사용하여 한 레지스터에서 다른 레지스터로 전송됩니다. For example: MOV K, B : 레지스터가 가리키는 메모리 주소에서 레지스터 K로 데이터가 전송됨을 의미합니다.

암시 적 주소 지정 모드

이 모드에는 피연산자가 필요하지 않습니다. 데이터는 opcode 자체에 의해 지정됩니다.For example: CMP.

8085에서 인터럽트

인터럽트는 마이크로 프로세서가 작업을 수행하도록 요청하기 위해 외부 장치가 생성하는 신호입니다. 인터럽트 신호는 TRAP, RST 7.5, RST 6.5, RST 5.5, INTR의 5 가지가 있습니다.

인터럽트는 매개 변수에 따라 다음 그룹으로 분류됩니다.

Vector interrupt −이 유형의 인터럽트에서 인터럽트 주소는 프로세서에 알려져 있습니다. For example: RST7.5, RST6.5, RST5.5, 트랩.

Non-Vector interrupt − 이러한 유형의 인터럽트에서 인터럽트 주소는 프로세서에 알려지지 않으므로 인터럽트를 수행하려면 장치가 인터럽트 주소를 외부로 보내야합니다. For example: INTR.

Maskable interrupt − 이런 종류의 인터럽트에서는 프로그램에 몇 가지 명령을 작성하여 인터럽트를 비활성화 할 수 있습니다. For example: RST7.5, RST6.5, RST5.5.

Non-Maskable interrupt − 이런 종류의 인터럽트에서는 프로그램에 몇 가지 명령을 써서 인터럽트를 비활성화 할 수 없습니다. For example: 덫.

Software interrupt− 이러한 유형의 인터럽트에서 프로그래머는 인터럽트를 실행하기 위해 프로그램에 명령어를 추가해야합니다. 8085에는 8 개의 소프트웨어 인터럽트, 즉 RST0, RST1, RST2, RST3, RST4, RST5, RST6 및 RST7이 있습니다.

Hardware interrupt − 8085에는 하드웨어 인터럽트로 사용되는 5 개의 인터럽트 핀 (예 : TRAP, RST7.5, RST6.5, RST5.5, INTA)이 있습니다.

Note− NTA는 인터럽트가 아니며 마이크로 프로세서에서 승인을 보내는 데 사용됩니다. TRAP이 가장 높은 우선 순위를 가지며 그 다음에는 RST7.5 등이 있습니다.

ISR (인터럽트 서비스 루틴)

실행될 때 해당 인터럽트 소스를 서비스하는 작은 프로그램 또는 루틴을 ISR이라고합니다.

덫

모든 인터럽트 중에서 가장 높은 우선 순위를 갖는 마스크 불가능한 인터럽트입니다. 기본적으로 확인 될 때까지 활성화됩니다. 장애가 발생하면 ISR로 실행하여 데이터를 백업 메모리로 보냅니다. 이 인터럽트는 제어를 0024H 위치로 전송합니다.

RST7.5

모든 인터럽트 중에서 두 번째로 높은 우선 순위를 갖는 마스크 가능한 인터럽트입니다. 이 인터럽트가 실행되면 프로세서는 PC 레지스터의 내용을 스택에 저장하고 003CH 주소로 분기합니다.

RST 6.5

모든 인터럽트 중에서 세 번째로 높은 우선 순위를 갖는 마스크 가능한 인터럽트입니다. 이 인터럽트가 실행되면 프로세서는 PC 레지스터의 내용을 스택에 저장하고 0034H 주소로 분기합니다.

RST 5.5

마스크 가능한 인터럽트입니다. 이 인터럽트가 실행되면 프로세서는 PC 레지스터의 내용을 스택에 저장하고 002CH 주소로 분기합니다.

INTR

모든 인터럽트 중에서 우선 순위가 가장 낮은 마스크 가능한 인터럽트입니다. 마이크로 프로세서를 재설정하여 비활성화 할 수 있습니다.

언제 INTR signal goes high, 다음 이벤트가 발생할 수 있습니다-

마이크로 프로세서는 각 명령을 실행하는 동안 INTR 신호의 상태를 확인합니다.

INTR 신호가 높으면 마이크로 프로세서는 현재 명령을 완료하고 활성 로우 인터럽트 승인 신호를 보냅니다.

명령어가 수신되면 마이크로 프로세서는 다음 명령어의 주소를 스택에 저장하고 수신 된 명령어를 실행합니다.

8085 마이크로 프로세서의 프로그래밍을 살펴 보겠습니다.

명령어 세트는 일부 작업을 수행하기위한 명령어 코드입니다. 다섯 가지 범주로 분류됩니다.

| S. 아니. | 지침 및 설명 |

|---|---|

| 1 | 제어 지침 다음은 그 의미와 함께 제어 명령 목록을 보여주는 표입니다. |

| 2 | 논리적 지침 다음은 해당 의미와 함께 논리 명령어 목록을 보여주는 표입니다. |

| 삼 | 분기 지침 다음은 의미와 함께 분기 명령어 목록을 보여주는 표입니다. |

| 4 | 산술 지침 다음은 의미와 함께 산술 명령어 목록을 보여주는 표입니다. |

| 5 | 데이터 전송 지침 다음은 의미와 함께 데이터 전송 명령어 목록을 보여주는 표입니다. |

8085 – 데모 프로그램

이제 위의 지침을 사용하여 몇 가지 프로그램 데모를 살펴 보겠습니다.

두 개의 8 비트 숫자 더하기

3005H 및 3006H 메모리 위치에 데이터를 추가하는 프로그램을 작성하고 결과를 3007H 메모리 위치에 저장합니다.

Problem demo −

(3005H) = 14H

(3006H) = 89HResult −

14 시간 + 89 시간 = 9 일

프로그램 코드는 다음과 같이 작성할 수 있습니다.

LXI H 3005H : "HL points 3005H"

MOV A, M : "Getting first operand"

INX H : "HL points 3006H"

ADD M : "Add second operand"

INX H : "HL points 3007H"

MOV M, A : "Store result at 3007H"

HLT : "Exit program"메모리 위치 교환

5000M 및 6000M 메모리 위치에서 데이터를 교환하는 프로그램을 작성하십시오.

LDA 5000M : "Getting the contents at5000M location into accumulator"

MOV B, A : "Save the contents into B register"

LDA 6000M : "Getting the contents at 6000M location into accumulator"

STA 5000M : "Store the contents of accumulator at address 5000M"

MOV A, B : "Get the saved contents back into A register"

STA 6000M : "Store the contents of accumulator at address 6000M"오름차순으로 번호 정렬

메모리 주소 3000H에서 처음 10 개의 숫자를 오름차순으로 배열하는 프로그램을 작성합니다.

MVI B, 09 :"Initialize counter"

START :"LXI H, 3000H: Initialize memory pointer"

MVI C, 09H :"Initialize counter 2"

BACK: MOV A, M :"Get the number"

INX H :"Increment memory pointer"

CMP M :"Compare number with next number"

JC SKIP :"If less, don’t interchange"

JZ SKIP :"If equal, don’t interchange"

MOV D, M

MOV M, A

DCX H

MOV M, D

INX H :"Interchange two numbers"

SKIP:DCR C :"Decrement counter 2"

JNZ BACK :"If not zero, repeat"

DCR B :"Decrement counter 1"

JNZ START

HLT :"Terminate program execution"8086 마이크로 프로세서는 1976 년 인텔에서 설계 한 8085 마이크로 프로세서의 향상된 버전입니다. 최대 1MB의 스토리지를 제공하는 20 개의 주소 라인과 16 개의 데이터 라인이있는 16 비트 마이크로 프로세서입니다. 강력한 명령어 세트로 구성되어 곱셈 및 나눗셈과 같은 연산을 쉽게 제공합니다.

최대 모드와 최소 모드의 두 가지 작동 모드를 지원합니다. 최대 모드는 다중 프로세서가있는 시스템에 적합하고 최소 모드는 단일 프로세서가있는 시스템에 적합합니다.

8086의 특징

8086 마이크로 프로세서의 가장 두드러진 특징은 다음과 같습니다.

메모리에서 6 개의 명령어 바이트를 저장할 수있는 명령어 대기열이있어 처리 속도가 빨라집니다.

16 비트 ALU, 16 비트 레지스터, 내부 데이터 버스 및 16 비트 외부 데이터 버스를 갖춘 최초의 16 비트 프로세서로 처리 속도가 빨라졌습니다.

작동 빈도에 따라 3 가지 버전으로 제공됩니다.

8086 → 5MHz

8086-2 → 8MHz

(c) 8086-1 → 10MHz

두 단계의 파이프 라이닝, 즉 Fetch Stage와 Execute Stage를 사용하여 성능을 향상시킵니다.

Fetch 스테이지는 최대 6 바이트의 명령어를 프리 페치하고 큐에 저장할 수 있습니다.

실행 단계는 이러한 명령을 실행합니다.

256 개의 벡터 인터럽트가 있습니다.

29,000 개의 트랜지스터로 구성됩니다.

8085 및 8086 마이크로 프로세서 비교

Size − 8085는 8 비트 마이크로 프로세서이고 8086은 16 비트 마이크로 프로세서입니다.

Address Bus − 8085에는 16 비트 주소 버스가 있고 8086에는 20 비트 주소 버스가 있습니다.

Memory − 8085는 최대 64Kb에 액세스 할 수있는 반면 8086은 최대 1Mb의 메모리에 액세스 할 수 있습니다.

Instruction − 8085에는 명령 대기열이없는 반면 8086에는 명령 대기열이 있습니다.

Pipelining − 8085는 파이프 라인 아키텍처를 지원하지 않는 반면 8086은 파이프 라인 아키텍처를 지원합니다.

I/O − 8085는 2 ^ 8 = 256 I / O를 처리 할 수있는 반면 8086은 2 ^ 16 = 65,536 I / O에 액세스 할 수 있습니다.

Cost − 8085의 비용은 낮은 반면 8086의 비용은 높습니다.

8086의 아키텍처

다음 다이어그램은 8086 마이크로 프로세서의 아키텍처를 보여줍니다.

8086 마이크로 프로세서는 두 개의 기능 단위로 나뉩니다. EU (실행 단위) 및 BIU (버스 인터페이스 장치).

EU (실행 단위)

실행 단위는 데이터를 가져올 위치를 알려주는 명령을 BIU에 제공 한 다음 해당 명령을 디코딩하고 실행합니다. 그 기능은 명령 디코더 및 ALU를 사용하여 데이터에 대한 작업을 제어하는 것입니다. EU는 위의 그림과 같이 시스템 버스와 직접 연결되지 않으며 BIU를 통해 데이터에 대한 작업을 수행합니다.

이제 8086 마이크로 프로세서의 기능적 부분에 대해 살펴 보겠습니다.

ALU

+, −, ×, /, OR, AND, NOT 연산과 같은 모든 산술 및 논리 연산을 처리합니다.

플래그 등록

플립 플롭처럼 동작하는 16 비트 레지스터입니다. 즉 누산기에 저장된 결과에 따라 상태가 변경됩니다. 9 개의 플래그가 있으며 조건부 플래그와 제어 플래그라는 두 그룹으로 나뉩니다.

조건부 플래그

마지막으로 실행 된 산술 또는 논리 명령어의 결과를 나타냅니다. 다음은 조건부 플래그 목록입니다-

Carry flag −이 플래그는 산술 연산에 대한 오버플로 조건을 나타냅니다.

Auxiliary flag− ALU에서 작업이 수행되면 하위 니블 (예 : D0 – D3)에서 상위 니블 (예 : D4 – D7)으로 캐리 / 배로 우가 발생합니다. 그러면이 플래그가 설정됩니다. AF 플래그. 프로세서는이 플래그를 사용하여 바이너리에서 BCD 로의 변환을 수행합니다.

Parity flag−이 플래그는 결과의 패리티를 표시하는 데 사용됩니다. 즉, 결과의 하위 8 비트에 1이 짝수 인 경우 패리티 플래그가 설정됩니다. 홀수 1의 경우 패리티 플래그가 재설정됩니다.

Zero flag −이 플래그는 산술 또는 논리 연산의 결과가 0 일 때 1로 설정되고, 그렇지 않으면 0으로 설정됩니다.

Sign flag −이 플래그는 결과의 부호를 보유합니다. 즉, 연산 결과가 음수이면 부호 플래그가 1로 설정되고 그렇지 않으면 0으로 설정됩니다.

Overflow flag −이 플래그는 시스템 용량 초과시 결과를 나타냅니다.

제어 플래그

제어 플래그는 실행 단위의 작업을 제어합니다. 다음은 제어 플래그 목록입니다-

Trap flag− 단일 스텝 제어에 사용되며 사용자가 디버깅을 위해 한 번에 하나의 명령을 실행할 수 있습니다. 설정되어 있으면 프로그램을 단일 단계 모드로 실행할 수 있습니다.

Interrupt flag− 인터럽트 활성화 / 비활성화 플래그입니다. 즉, 프로그램 중단을 허용 / 금지하는 데 사용됩니다. 인터럽트 가능 조건은 1, 인터럽트 불가능 조건은 0으로 설정됩니다.

Direction flag− 문자열 연산에 사용됩니다. 이름에서 알 수 있듯이 문자열 바이트는 상위 메모리 주소에서 하위 메모리 주소로, 그 반대의 경우에도 액세스됩니다.

범용 레지스터

8 개의 범용 레지스터 즉, AH, AL, BH, BL, CH, CL, DH 및 DL이 있습니다. 이 레지스터는 8 비트 데이터를 저장하기 위해 개별적으로 사용할 수 있으며 16 비트 데이터를 저장하기 위해 쌍으로 사용할 수 있습니다. 유효한 레지스터 쌍은 AH와 AL, BH와 BL, CH와 CL, DH와 DL입니다. 각각 AX, BX, CX 및 DX라고합니다.

AX register− 누산기 레지스터라고도합니다. 산술 연산을위한 피연산자를 저장하는 데 사용됩니다.

BX register−베이스 레지스터로 사용됩니다. 데이터 세그먼트 내 메모리 영역의 시작 기본 주소를 저장하는 데 사용됩니다.

CX register− 카운터라고합니다. 루프 카운터를 저장하기 위해 루프 명령에서 사용됩니다.

DX register −이 레지스터는 I / O 명령을위한 I / O 포트 주소를 저장하는 데 사용됩니다.

스택 포인터 레지스터

이것은 16 비트 레지스터로, 세그먼트의 시작부터 가장 최근에 스택에 저장된 단어가있는 메모리 위치까지의 주소를 보유합니다.

BIU (버스 인터페이스 장치)

BIU는 주소 전송, 메모리에서 명령 가져 오기, 포트 및 메모리에서 데이터 읽기, 포트 및 메모리에 데이터 쓰기와 같은 EU 버스의 모든 데이터 및 주소 전송을 처리합니다. EU는 시스템 버스와 방향 연결이 없으므로 BIU로 가능합니다. EU 및 BIU는 내부 버스로 연결됩니다.

그것은 다음과 같은 기능 부분을 가지고 있습니다-

Instruction queue− BIU는 명령 대기열을 포함합니다. BIU는 최대 6 바이트의 다음 명령어를 가져 와서 명령어 대기열에 저장합니다. EU가 명령어를 실행하고 다음 명령어를 준비 할 때이 명령어 대기열에서 명령어를 읽기만하면 실행 속도가 빨라집니다.

현재 명령어가 실행되는 동안 다음 명령어를 가져 오는 것이 호출됩니다. pipelining.

Segment register− BIU에는 CS, DS, SS & ES의 4 개의 세그먼트 버스가 있습니다. 프로세서가 메모리 위치에 액세스하는 데 사용하는 메모리의 명령어 및 데이터 주소를 보유합니다. 또한 EU에서 실행할 다음 명령어의 주소를 보유하는 1 개의 포인터 레지스터 IP를 포함합니다.

CS− Code Segment를 의미합니다. 실행 프로그램이 저장되는 메모리의 코드 세그먼트에서 메모리 위치를 지정하는 데 사용됩니다.

DS− 데이터 세그먼트를 의미합니다. 프로그램에서 사용하는 데이터로 구성되며 오프셋 주소 또는 오프셋 주소를 보유하는 다른 레지스터의 내용에 의해 데이터 세그먼트에서 액세스됩니다.

SS− Stack Segment를 의미합니다. 실행 중에 데이터와 주소를 저장하기 위해 메모리를 처리합니다.

ES− Extra Segment를 의미합니다. ES는 추가 데이터 세그먼트로, 추가 대상 데이터를 보유하기 위해 문자열에서 사용됩니다.

Instruction pointer − 실행될 다음 명령어의 주소를 보유하는 데 사용되는 16 비트 레지스터입니다.

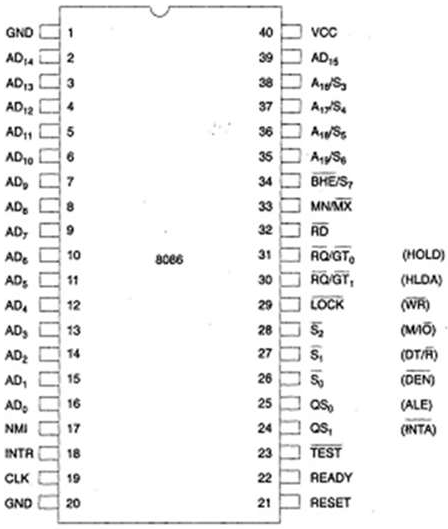

8086은 40 핀 DIP (듀얼 인라인 패키지) 칩으로 제공되는 최초의 16 비트 마이크로 프로세서였습니다. 이제 8086 마이크로 프로세서의 핀 구성에 대해 자세히 설명하겠습니다.

8086 핀 다이어그램

다음은 8086 마이크로 프로세서의 핀 다이어그램입니다.

이제 신호에 대해 자세히 살펴 보겠습니다.

Power supply and frequency signals

V CC 핀 40 에서 5V DC 공급을 사용 하고 작동을 위해 V SS 핀 1 및 20 에서 접지를 사용 합니다.

Clock signal

클럭 신호는 Pin-19를 통해 제공됩니다. 작업을 위해 프로세서에 타이밍을 제공합니다. 주파수는 버전마다 다릅니다 (예 : 5MHz, 8MHz 및 10MHz).

Address/data bus

AD0-AD15. 16 개 주소 / 데이터 버스입니다. AD0-AD7은 하위 바이트 데이터를 전달하고 AD8AD15는 상위 바이트 데이터를 전달합니다. 첫 번째 클럭 사이클 동안 16 비트 주소를 전달하고 그 후에 16 비트 데이터를 전달합니다.

Address/status bus

A16-A19 / S3-S6. 이것은 4 개의 주소 / 상태 버스입니다. 첫 번째 클럭 사이클 동안 4 비트 주소를 전달하고 나중에 상태 신호를 전달합니다.

S7/BHE

BHE는 Bus High Enable을 나타냅니다. 핀 34에서 사용할 수 있으며 데이터 버스 D8-D15를 사용하여 데이터 전송을 나타내는 데 사용됩니다. 이 신호는 첫 번째 클록 사이클 동안 낮고 그 후에 활성화됩니다.

Read($\overline{RD}$)

핀 32에서 사용할 수 있으며 읽기 작업을 위해 신호를 읽는 데 사용됩니다.

Ready

핀 22에서 사용할 수 있습니다. 데이터가 전송되는 I / O 장치의 승인 신호입니다. 액티브 하이 신호입니다. 높으면 장치가 데이터를 전송할 준비가되었음을 나타냅니다. 낮 으면 대기 상태를 나타냅니다.

RESET

핀 21에서 사용할 수 있으며 실행을 다시 시작하는 데 사용됩니다. 이로 인해 프로세서가 현재 활동을 즉시 종료합니다. 이 신호는 마이크로 프로세서를 리셋하기 위해 처음 4 클럭 사이클 동안 활성 하이입니다.

INTR

핀 18에서 사용할 수 있습니다. 이는 인터럽트 요청 신호로, 프로세서가이를 인터럽트로 간주했는지 여부를 결정하기 위해 각 명령의 마지막 클록주기 동안 샘플링됩니다.

NMI

마스크 불가능 인터럽트를 나타내며 17 번 핀에서 사용할 수 있습니다. 에지 트리거 입력으로 마이크로 프로세서에 인터럽트 요청을 발생시킵니다.

$\overline{TEST}$

이 신호는 대기 상태와 같으며 핀 23에서 사용할 수 있습니다.이 신호가 높으면 프로세서는 IDLE 상태를 기다려야하며 그렇지 않으면 실행이 계속됩니다.

MN/$\overline{MX}$

최소 / 최대를 나타내며 핀 33에서 사용할 수 있습니다. 프로세서가 작동 할 모드를 나타냅니다. 높으면 최소 모드에서 작동하고 그 반대의 경우도 마찬가지입니다.

INTA

이것은 인터럽트 승인 신호와 핀 24에서 사용 가능한 id입니다. 마이크로 프로세서가이 신호를 수신하면 인터럽트를 승인합니다.

ALE

주소 활성화 래치를 나타내며 핀 25에서 사용할 수 있습니다. 프로세서가 작업을 시작할 때마다 양의 펄스가 생성됩니다. 이 신호는 주소 / 데이터 라인에서 유효한 주소의 가용성을 나타냅니다.

DEN

데이터 활성화를 나타내며 핀 26에서 사용할 수 있습니다. 트랜시버 8286을 활성화하는 데 사용됩니다. 트랜시버는 주소 / 데이터 버스에서 데이터를 분리하는 데 사용되는 장치입니다.

DT/R

데이터 전송 / 수신 신호를 나타내며 핀 27에서 사용할 수 있습니다. 트랜시버를 통한 데이터 흐름의 방향을 결정합니다. 높으면 데이터가 전송되고 그 반대의 경우도 마찬가지입니다.

M/IO

이 신호는 메모리와 I / O 작업을 구분하는 데 사용됩니다. 높으면 I / O 동작을 나타내고, 낮 으면 메모리 동작을 나타냅니다. 핀 28에서 사용할 수 있습니다.

WR

쓰기 신호를 의미하며 29 번 핀에서 사용할 수 있습니다. M / IO 신호의 상태에 따라 메모리 또는 출력 장치에 데이터를 쓰는 데 사용됩니다.

HLDA

Hold Acknowledgment 신호를 나타내며 핀 30에서 사용할 수 있습니다.이 신호는 HOLD 신호를 인식합니다.

HOLD

이 신호는 외부 장치가 주소 / 데이터 버스에 액세스하도록 요청하고 있음을 프로세서에 알립니다. 핀 31에서 사용할 수 있습니다.

QS1 and QS0

이들은 대기열 상태 신호이며 핀 24 및 25에서 사용할 수 있습니다. 이러한 신호는 명령 대기열의 상태를 제공합니다. 그들의 조건은 다음 표에 나와 있습니다.

| QS 0 | 질문 1 | 상태 |

|---|---|---|

| 0 | 0 | 작동하지 않음 |

| 0 | 1 | 대기열의 첫 번째 opcode 바이트 |

| 1 | 0 | 대기열 비우기 |

| 1 | 1 | 큐의 후속 바이트 |

S0, S1, S2

이것은 작동 상태를 제공하는 상태 신호이며, 버스 컨트롤러 8288에서 메모리 및 I / O 제어 신호를 생성하는 데 사용됩니다. 핀 26, 27, 28에서 사용할 수 있습니다. 다음은 상태를 보여주는 표입니다.

| S 2 | S 1 | S 0 | 상태 |

|---|---|---|---|

| 0 | 0 | 0 | 인터럽트 승인 |

| 0 | 0 | 1 | I / O 읽기 |

| 0 | 1 | 0 | I / O 쓰기 |

| 0 | 1 | 1 | 정지 |

| 1 | 0 | 0 | Opcode 가져 오기 |

| 1 | 0 | 1 | 메모리 읽기 |

| 1 | 1 | 0 | 메모리 쓰기 |

| 1 | 1 | 1 | 수동태 |

LOCK

이 신호가 활성화되면 CPU가 시스템 버스를 떠나도록 요청하지 않도록 다른 프로세서에 알립니다. 모든 명령어에서 LOCK 접두사를 사용하여 활성화되며 핀 29에서 사용할 수 있습니다.

RQ/GT1 and RQ/GT0

이는 CPU에 시스템 버스 해제를 요청하는 다른 프로세서에서 사용하는 요청 / 부여 신호입니다. 신호가 CPU에 수신되면 승인을 보냅니다. RQ / GT 0 은 RQ / GT 1 보다 우선 순위가 높습니다 .

8086 마이크로 프로세서는 8 가지 유형의 명령어를 지원합니다.

- 데이터 전송 지침

- 산술 지침

- 비트 조작 지침

- 문자열 지침

- 프로그램 실행 전송 명령 (분기 및 루프 명령)

- 프로세서 제어 지침

- 반복 제어 지침

- 인터럽트 지침

이제 이러한 명령어 세트에 대해 자세히 설명하겠습니다.

데이터 전송 지침

이러한 명령어는 소스 피연산자에서 대상 피연산자로 데이터를 전송하는 데 사용됩니다. 다음은이 그룹의 지침 목록입니다.

단어 전달 지침

MOV − 제공된 소스에서 제공된 대상으로 바이트 또는 단어를 복사하는 데 사용됩니다.

PPUSH − 스택 맨 위에 단어를 넣는 데 사용됩니다.

POP − 스택 상단에서 제공된 위치로 단어를 가져 오는 데 사용됩니다.

PUSHA − 모든 레지스터를 스택에 넣는 데 사용됩니다.

POPA − 스택에서 모든 레지스터로 단어를 가져 오는 데 사용됩니다.

XCHG − 두 위치에서 데이터를 교환하는 데 사용됩니다.

XLAT − 메모리의 테이블을 사용하여 AL의 바이트를 번역하는 데 사용됩니다.

입력 및 출력 포트 전송 지침

IN − 제공된 포트에서 누산기로 바이트 또는 단어를 읽는 데 사용됩니다.

OUT − 누산기에서 제공된 포트로 바이트 또는 단어를 보내는 데 사용됩니다.

주소 이전 지침

LEA − 제공된 레지스터에 오퍼랜드의 주소를로드하는 데 사용됩니다.

LDS − 메모리에서 DS 레지스터 및 기타 제공된 레지스터를로드하는 데 사용됩니다.

LES − ES 레지스터 및 기타 제공된 레지스터를 메모리에서로드하는 데 사용됩니다.

플래그 레지스터 전송 지침

LAHF − 플래그 레지스터의 하위 바이트로 AH를로드하는 데 사용됩니다.

SAHF − AH 레지스터를 플래그 레지스터의 하위 바이트에 저장하는 데 사용됩니다.

PUSHF − 스택 맨 위에있는 플래그 레지스터를 복사하는 데 사용됩니다.

POPF − 스택 맨 위에있는 단어를 플래그 레지스터로 복사하는 데 사용됩니다.

산술 지침

이 명령어는 더하기, 빼기, 곱하기, 나누기 등과 같은 산술 연산을 수행하는 데 사용됩니다.

다음은이 그룹의 지침 목록입니다.

추가 수행 지침

ADD − 제공된 바이트를 바이트 단위로 / 워드 단위로 추가 할 때 사용합니다.

ADC − 캐리와 함께 추가하는 데 사용됩니다.

INC − 제공된 바이트 / 워드를 1 씩 증가시키는 데 사용됩니다.

AAA − 추가 후 ASCII 조정에 사용합니다.

DAA − 더하기 / 빼기 연산 후 소수점을 조정하는 데 사용됩니다.

빼기를 수행하는 지침

SUB − 워드에서 바이트 / 워드에서 바이트를 빼는 데 사용됩니다.

SBB − 차용으로 빼기를 수행하는 데 사용됩니다.

DEC − 제공된 바이트 / 워드를 1 씩 감소시키는 데 사용됩니다.

NPG − 제공된 바이트 / 워드의 각 비트를 부정하고 1/2의 보수를 추가하는 데 사용됩니다.

CMP − 제공된 2 바이트 / 워드를 비교하는 데 사용됩니다.

AAS − 빼기 후 ASCII 코드를 조정하는 데 사용됩니다.

DAS − 빼기 후 소수점 조정에 사용합니다.

곱셈 수행 지침

MUL − 부호없는 바이트를 바이트 / 워드로 곱하는 데 사용됩니다.

IMUL − 부호있는 바이트를 바이트 / 워드로 곱하는 데 사용됩니다.

AAM − 곱셈 후 ASCII 코드를 조정하는 데 사용됩니다.

분할 수행 지침

DIV − 부호없는 단어를 바이트로 나누거나 부호없는 더블 단어를 단어로 나누는 데 사용됩니다.

IDIV − 부호있는 단어를 바이트로 나누거나 부호있는 더블 단어를 단어로 나누는 데 사용됩니다.

AAD − 분할 후 ASCII 코드 조정에 사용합니다.

CBW − 하위 바이트의 부호 비트 사본으로 단어의 상위 바이트를 채우는 데 사용됩니다.

CWD − 더블 워드의 상위 단어를 하위 단어의 부호 비트로 채울 때 사용합니다.

비트 조작 지침

이러한 명령어는 데이터 비트가 관련된 작업, 즉 논리, 시프트 등과 같은 작업을 수행하는 데 사용됩니다.

다음은이 그룹의 지침 목록입니다.

논리 연산 수행 지침

NOT − 바이트 또는 워드의 각 비트를 반전하는 데 사용됩니다.

AND − 바이트 / 워드의 각 비트를 다른 바이트 / 워드의 해당 비트와 추가하는 데 사용됩니다.

OR − 바이트 / 워드의 각 비트를 다른 바이트 / 워드의 해당 비트와 곱하는 데 사용됩니다.

XOR − 다른 바이트 / 워드의 해당 비트와 함께 바이트 / 워드의 각 비트에 대해 Exclusive-OR 연산을 수행하는 데 사용됩니다.

TEST − 피연산자에 영향을주지 않고 플래그를 업데이트하기 위해 피연산자를 추가하는 데 사용됩니다.

교대 작업 수행 지침

SHL/SAL − 바이트 / 워드의 비트를 왼쪽으로 이동하고 LSB에 0 (S)을 넣는 데 사용됩니다.

SHR − 바이트 / 워드의 비트를 오른쪽으로 이동하고 MSB에 0 (S)을 넣는 데 사용됩니다.

SAR − 바이트 / 워드의 비트를 오른쪽으로 이동하고 이전 MSB를 새 MSB에 복사하는 데 사용됩니다.

회전 작업 수행 지침

ROL − 바이트 / 워드의 비트를 왼쪽으로 회전하는 데 사용됩니다. 즉, MSB에서 LSB로, 캐리 플래그 [CF]로.

ROR − 바이트 / 워드 비트를 오른쪽으로 회전하는 데 사용됩니다. 즉 LSB에서 MSB로, 캐리 플래그 [CF]로.

RCR − 바이트 / 워드 비트를 오른쪽으로 회전하는 데 사용됩니다. 즉, LSB에서 CF로, CF에서 MSB로.

RCL − MSB에서 CF로, CF에서 LSB로 바이트 / 워드의 비트를 왼쪽으로 회전하는 데 사용됩니다.

문자열 지침

문자열은 바이트 / 워드 그룹이며 해당 메모리는 항상 순차적 인 순서로 할당됩니다.

다음은이 그룹의 지침 목록입니다.

REP − CX ≠ 0이 될 때까지 주어진 명령을 반복하는 데 사용됩니다.

REPE/REPZ − CX = 0 또는 제로 플래그 ZF = 1이 될 때까지 주어진 명령을 반복하는 데 사용됩니다.

REPNE/REPNZ − CX = 0 또는 제로 플래그 ZF = 1이 될 때까지 주어진 명령을 반복하는 데 사용됩니다.

MOVS/MOVSB/MOVSW − 한 문자열에서 다른 문자열로 바이트 / 워드를 이동하는 데 사용됩니다.

COMS/COMPSB/COMPSW − 두 문자열 바이트 / 단어를 비교하는 데 사용됩니다.

INS/INSB/INSW − I / O 포트에서 제공된 메모리 위치까지 입력 문자열 / 바이트 / 워드로 사용됩니다.

OUTS/OUTSB/OUTSW − 제공된 메모리 위치에서 I / O 포트로 출력 문자열 / 바이트 / 워드로 사용됩니다.

SCAS/SCASB/SCASW − 문자열을 스캔하고 해당 바이트를 AL의 바이트와 비교하거나 문자열 단어를 AX의 단어와 비교하는 데 사용됩니다.

LODS/LODSB/LODSW − 문자열 바이트를 AL에 저장하거나 문자열 단어를 AX에 저장하는 데 사용됩니다.

프로그램 실행 전송 명령 (분기 및 루프 명령)

이러한 명령어는 실행 중에 명령어를 전송 / 분기하는 데 사용됩니다. 다음 지침이 포함되어 있습니다.

조건없이 실행하는 동안 명령을 전송하는 명령-

CALL − 프로 시저를 호출하고 반환 주소를 스택에 저장하는 데 사용됩니다.

RET − 절차에서 메인 프로그램으로 돌아가는 데 사용됩니다.

JMP − 다음 명령으로 진행하기 위해 제공된 주소로 점프하는 데 사용됩니다.

일부 조건에서 실행하는 동안 명령을 전송하는 명령-

JA/JNBE − 초과 / 미만 / 동등 명령이 충족되면 점프하는 데 사용됩니다.

JAE/JNB − 위 / 아래가 아닌 명령어가 만족하는 경우 점프하는 데 사용됩니다.

JBE/JNA − 아래 / 같음 / 위가 아닌 명령어가 만족하는 경우 점프하는 데 사용됩니다.

JC − 캐리 플래그 CF = 1 인 경우 점프에 사용

JE/JZ − 동일 / 제로 플래그 ZF = 1 인 경우 점프하는 데 사용됩니다.

JG/JNLE − 크거나 작지 않은 / 같음 명령이 만족하는 경우 점프하는 데 사용됩니다.

JGE/JNL − 명령어보다 크거나 같거나 작지 않은 경우 점프하는 데 사용됩니다.

JL/JNGE −보다 작거나 크지 않은 / 같음 명령이 만족하는 경우 점프하는 데 사용됩니다.

JLE/JNG − 명령보다 작거나 같거나 크지 않으면 점프하는 데 사용됩니다.

JNC − 캐리 플래그가없는 경우 점프에 사용 (CF = 0)

JNE/JNZ − 같지 않거나 0이 아닌 경우 점프하는 데 사용 플래그 ZF = 0

JNO − 오버플로 플래그가없는 경우 점프에 사용 OF = 0

JNP/JPO − 패리티 / 패리티 홀수 PF = 0이 아닌 경우 점프하는 데 사용됩니다.

JNS − SF = 0에 서명하지 않으면 점프하는 데 사용됩니다.

JO − 오버플로 플래그 OF = 1 인 경우 점프하는 데 사용됩니다.

JP/JPE − 패리티 / 패리티 PF = 1 인 경우 점프하는 데 사용

JS − 표시 플래그 SF = 1 인 경우 점프에 사용

프로세서 제어 지침

이러한 명령어는 플래그 값을 설정 / 재설정하여 프로세서 작업을 제어하는 데 사용됩니다.

다음은이 그룹의 지침입니다.

STC − 캐리 플래그 CF를 1로 설정하는 데 사용됩니다.

CLC − 캐리 플래그 CF를 0으로 클리어 / 리셋하는 데 사용

CMC − 캐리 플래그 CF 상태에서 보수를 넣는 데 사용됩니다.

STD − 방향 플래그 DF를 1로 설정하는 데 사용됩니다.

CLD − 방향 플래그 DF를 0으로 지우거나 재설정하는 데 사용됩니다.

STI − 인터럽트 활성화 플래그를 1로 설정하는 데 사용됩니다. 즉, INTR 입력을 활성화합니다.

CLI − 인터럽트 활성화 플래그를 0으로 지우는 데 사용됩니다. 즉, INTR 입력을 비활성화합니다.

반복 제어 지침

이러한 명령어는 주어진 명령어를 여러 번 실행하는 데 사용됩니다. 다음은이 그룹의 지침 목록입니다.

LOOP − 조건이 충족 될 때까지 명령 그룹을 반복하는 데 사용됩니다 (예 : CX = 0).

LOOPE/LOOPZ − ZF = 1 & CX = 0을 만족할 때까지 명령어 그룹을 반복하는 데 사용됩니다.

LOOPNE/LOOPNZ − ZF = 0 & CX = 0을 만족할 때까지 명령어 그룹을 반복하는 데 사용됩니다.

JCXZ − CX = 0 인 경우 제공된 주소로 점프하는 데 사용됩니다.

인터럽트 지침

이 명령어는 프로그램 실행 중에 인터럽트를 호출하는 데 사용됩니다.

INT − 지정된 서비스를 실행하고 호출하는 동안 프로그램을 중단하는 데 사용됩니다.

INTO − OF = 1 인 경우 실행 중 프로그램 중단에 사용

IRET − 인터럽트 서비스에서 메인 프로그램으로 복귀하는데 사용

Interrupt프로그램 실행 중에 임시 정지를 생성하는 방법이며 주변 장치가 마이크로 프로세서에 액세스 할 수 있도록합니다. 마이크로 프로세서는 해당 인터럽트에ISR (Interrupt Service Routine)은 마이크로 프로세서에 인터럽트 처리 방법을 지시하는 짧은 프로그램입니다.

다음 이미지는 8086 마이크로 프로세서에있는 인터럽트 유형을 보여줍니다.

하드웨어 인터럽트

하드웨어 인터럽트는 지정된 핀을 통해 마이크로 프로세서로 신호를 보내 주변 장치에 의해 발생합니다.

8086에는 두 개의 하드웨어 인터럽트 핀, 즉 NMI와 INTR이 있습니다. NMI는 마스크 불가능한 인터럽트이고 INTR은 낮은 우선 순위를 갖는 마스크 가능한 인터럽트입니다. 연관된 인터럽트 핀 하나는 인터럽트 승인이라고하는 INTA입니다.

NMI

마스킹 가능한 인터럽트 요청 핀 (INTR)보다 우선 순위가 높은 단일 비 마스크 가능한 인터럽트 핀 (NMI)이며 유형 2 인터럽트입니다.

이 인터럽트가 활성화되면 다음 작업이 수행됩니다.

진행중인 현재 명령을 완료합니다.

플래그 레지스터 값을 스택에 푸시합니다.

반환 주소의 CS (코드 세그먼트) 값과 IP (명령 포인터) 값을 스택에 푸시합니다.

단어 위치 00008H의 내용에서 IP를로드합니다.

CS는 다음 단어 위치 0000AH의 내용에서로드됩니다.

인터럽트 플래그와 트랩 플래그가 0으로 재설정됩니다.

INTR

인터럽트 플래그 설정 명령을 사용하여 인터럽트가 활성화 된 경우에만 마이크로 프로세서가 인터럽트되므로 INTR은 마스크 가능한 인터럽트입니다. 인터럽트 플래그 지우기 명령을 사용하여 활성화해서는 안됩니다.

INTR 인터럽트는 I / O 포트에 의해 활성화됩니다. 인터럽트가 활성화되고 NMI가 비활성화되면 마이크로 프로세서는 먼저 현재 실행을 완료하고 INTA 핀에 '0'을 두 번 보냅니다. 첫 번째 '0'은 INTA가 외부 장치에 준비를 알리고 두 번째 '0'동안 마이크로 프로세서가 프로그래밍 가능한 인터럽트 컨트롤러로부터 8 비트 (예 : X)를 수신함을 의미합니다.

이러한 조치는 마이크로 프로세서에 의해 수행됩니다.

먼저 현재 명령을 완료합니다.

INTA 출력을 활성화하고 X와 같은 인터럽트 유형을 수신합니다.

플래그 레지스터 값, 반환 주소의 CS 값 및 반환 주소의 IP 값이 스택에 푸시됩니다.

IP 값은 단어 위치 X × 4의 내용에서로드됩니다.

CS는 다음 단어 위치의 내용에서로드됩니다.

인터럽트 플래그 및 트랩 플래그가 0으로 재설정됩니다.

소프트웨어 인터럽트

일부 명령은 인터럽트를 생성하기 위해 프로그램의 원하는 위치에 삽입됩니다. 이러한 인터럽트 명령어는 다양한 인터럽트 핸들러의 작동을 테스트하는 데 사용할 수 있습니다. 그것은 포함합니다-

INT- 유형 번호가있는 인터럽트 명령어

2 바이트 명령어입니다. 첫 번째 바이트는 연산 코드를 제공하고 두 번째 바이트는 인터럽트 유형 번호를 제공합니다. 이 그룹에는 256 개의 인터럽트 유형이 있습니다.

실행에는 다음 단계가 포함됩니다.

플래그 레지스터 값이 스택으로 푸시됩니다.

반환 주소의 CS 값과 반환 주소의 IP 값이 스택으로 푸시됩니다.

IP는 단어 위치 '유형 번호'× 4의 내용에서로드됩니다.

CS는 다음 단어 위치의 내용에서로드됩니다.

인터럽트 플래그 및 트랩 플래그가 0으로 재설정됩니다.

type0 인터럽트의 시작 주소는 000000H이고 type1 인터럽트의 경우 00004H는 type2의 경우와 유사하게 00008H이고 …… 처음 5 개의 포인터는 전용 인터럽트 포인터입니다. 즉-

TYPE 0 인터럽트는 0으로 나누는 상황을 나타냅니다.

TYPE 1 인터럽트는 프로그램 디버깅 중 단일 단계 실행을 나타냅니다.

TYPE 2 인터럽트는 마스크 불가능한 NMI 인터럽트를 나타냅니다.

TYPE 3 인터럽트는 중단 점 인터럽트를 나타냅니다.

TYPE 4 인터럽트는 오버플로 인터럽트를 나타냅니다.

유형 5에서 유형 31까지의 인터럽트는 다른 고급 마이크로 프로세서 용으로 예약되어 있으며 32에서 유형 255까지의 인터럽트는 하드웨어 및 소프트웨어 인터럽트에 사용할 수 있습니다.

INT 3- 브레이크 포인트 인터럽트 명령어

op-code가 CCH 인 1 바이트 명령어입니다. 이러한 명령어는 프로그램에 삽입되어 프로세서가 거기에 도달하면 프로그램의 정상적인 실행을 중지하고 중단 점 절차를 따릅니다.

실행에는 다음 단계가 포함됩니다.

플래그 레지스터 값이 스택으로 푸시됩니다.

반환 주소의 CS 값과 반환 주소의 IP 값이 스택으로 푸시됩니다.

단어 위치 3 × 4 = 0000CH의 내용에서 IP를로드합니다.

CS는 다음 단어 위치의 내용에서로드됩니다.

인터럽트 플래그 및 트랩 플래그가 0으로 재설정됩니다.

INTO-오버 플로우 명령어 인터럽트

1 바이트 명령어와 니모닉 INTO. 이 명령어의 연산 코드는 CEH입니다. 이름에서 알 수 있듯이 조건부 인터럽트 명령입니다. 즉, 오버플로 플래그가 1로 설정된 경우에만 활성화되고 인터럽트 유형 번호가 4 인 인터럽트 핸들러로 분기됩니다. 오버플로 플래그가 재설정되면 실행은 계속됩니다. 다음 지시.

실행에는 다음 단계가 포함됩니다.

플래그 레지스터 값은 스택으로 푸시됩니다.

반환 주소의 CS 값과 반환 주소의 IP 값이 스택으로 푸시됩니다.

IP는 단어 위치 4 × 4 = 00010H의 내용에서로드됩니다.

CS는 다음 단어 위치의 내용에서로드됩니다.

인터럽트 플래그 및 트랩 플래그가 0으로 재설정됩니다.

소스 피연산자가 명령어에서 표시되는 여러 가지 방법은 다음과 같습니다. addressing modes. 8086 프로그래밍에는 8 가지 주소 지정 모드가 있습니다.

즉시 주소 지정 모드

데이터 피연산자가 명령어 자체의 일부인 주소 지정 모드를 즉시 주소 지정 모드라고합니다.

예

MOV CX, 4929 H, ADD AX, 2387 H, MOV AL, FFH주소 지정 모드 등록

이는 레지스터가 명령어에 대한 피연산자의 소스임을 의미합니다.

예

MOV CX, AX ; copies the contents of the 16-bit AX register into

; the 16-bit CX register),

ADD BX, AX직접 주소 지정 모드

메모리 위치의 유효 주소가 명령어에 직접 기록되는 주소 지정 모드입니다.

예

MOV AX, [1592H], MOV AL, [0300H]간접 주소 지정 모드 등록

이 주소 지정 모드를 사용하면 BP, BX, DI 및 SI 레지스터에있는 오프셋 주소를 통해 모든 메모리 위치에서 데이터 주소를 지정할 수 있습니다.

예

MOV AX, [BX] ; Suppose the register BX contains 4895H, then the contents

; 4895H are moved to AX

ADD CX, {BX}기반 주소 지정 모드

이 주소 지정 모드에서 피연산자의 오프셋 주소는 BX / BP 레지스터의 내용과 8 비트 / 16 비트 변위의 합으로 제공됩니다.

예

MOV DX, [BX+04], ADD CL, [BX+08]인덱싱 된 주소 지정 모드

이 주소 지정 모드에서 피연산자 오프셋 주소는 SI 또는 DI 레지스터의 내용과 8 비트 / 16 비트 변위를 추가하여 찾습니다.

예

MOV BX, [SI+16], ADD AL, [DI+16]기반 인덱스 주소 지정 모드

이 주소 지정 모드에서 피연산자의 오프셋 주소는 기준 레지스터를 인덱스 레지스터의 내용에 합산하여 계산됩니다.

예

ADD CX, [AX+SI], MOV AX, [AX+DI]변위 모드로 색인 된 기반

이 주소 지정 모드에서 피연산자 오프셋은 기본 레지스터 내용을 추가하여 계산됩니다. 인덱스는 내용과 8 비트 또는 16 비트 변위를 등록합니다.

예

MOV AX, [BX+DI+08], ADD CX, [BX+SI+16]멀티 프로세서는 명령을 동시에 실행하는 여러 프로세서 세트를 의미합니다. 세 가지 기본 다중 프로세서 구성이 있습니다.

- 코 프로세서 구성

- 밀접하게 연결된 구성

- 느슨하게 결합 된 구성

코 프로세서 구성

코 프로세서는 마이크로 프로세서가 수행하는 동일한 작업을 매우 빠르게 수행 할 수있는 마이크로 프로세서 칩에 특별히 설계된 회로입니다. 메인 프로세서의 작업 부하를 줄입니다. 코 프로세서는 동일한 메모리, IO 시스템, 버스, 제어 로직 및 클록 생성기를 공유합니다. 코 프로세서는 수학적 계산, 화면의 그래픽 표시 등과 같은 특수 작업을 처리합니다.

8086 및 8088은 대부분의 연산을 수행 할 수 있지만 명령어 세트는 복잡한 수학적 연산을 수행 할 수 없으므로 이러한 경우 마이크로 프로세서에는 이러한 연산을 매우 빠르게 수행 할 수있는 Intel 8087 수학 보조 프로세서와 같은 수학 보조 프로세서가 필요합니다.

코 프로세서 구성의 블록 다이어그램

코 프로세서와 프로세서는 어떻게 연결되어 있습니까?

코 프로세서와 프로세서는 TEST, RQ- / GT- 및 QS 0 및 QS 1 신호 를 통해 연결됩니다 .

TEST 신호는 보조 프로세서의 BUSY 핀에 연결되고 나머지 3 개의 핀은 동일한 이름의 보조 프로세서의 3 개 핀에 연결됩니다.

TEST 신호는 보조 프로세서의 활동을 처리합니다. 즉, 보조 프로세서가 사용 중이거나 유휴 상태입니다.

RT- / GT-는 버스 중재에 사용됩니다.

코 프로세서는 QS 0 및 QS 1 을 사용 하여 호스트 프로세서의 대기열 상태를 추적합니다.

밀접하게 결합 된 구성

밀접하게 결합 된 구성은 코 프로세서 구성과 유사합니다. 즉, 둘 다 호스트 프로세서와 동일한 메모리, I / O 시스템 버스, 제어 로직 및 제어 생성기를 공유합니다. 그러나 보조 프로세서와 호스트 프로세서는 자체 명령을 가져와 실행합니다. 시스템 버스는 코 프로세서와 호스트 프로세서에 의해 독립적으로 제어됩니다.

밀접하게 결합 된 구성의 블록 다이어그램

프로세서와 독립 프로세서는 어떻게 연결되어 있습니까?

호스트와 독립 프로세서 간의 통신은 메모리 공간을 통해 이루어집니다.

WAIT, ESC 등과 같은 통신에 사용되는 명령은 없습니다.

호스트 프로세서는 메모리를 관리하고 포트 중 하나에 명령을 보내 독립 프로세서를 깨 웁니다.

그런 다음 독립 프로세서가 메모리에 액세스하여 작업을 실행합니다.

작업이 완료된 후 상태 신호 또는 인터럽트 요청을 사용하여 호스트 프로세서에 승인을 보냅니다.

느슨하게 결합 된 구성

느슨하게 결합 된 구성은 공통 시스템 버스를 통해 연결된 마이크로 프로세서 기반 시스템의 모듈 수로 구성됩니다. 각 모듈은 자체 클럭 생성기, 메모리, I / O 장치로 구성되며 로컬 버스를 통해 연결됩니다.

느슨하게 결합 된 구성의 블록 다이어그램

장점

둘 이상의 프로세서를 사용하면 효율성이 향상됩니다.

각 프로세서에는 로컬 메모리 / I / O 장치에 액세스하기위한 자체 로컬 버스가 있습니다. 이렇게하면 병렬 처리를 쉽게 수행 할 수 있습니다.

시스템 구조는 유연합니다. 즉, 한 모듈의 고장이 전체 시스템 고장에 영향을주지 않습니다. 결함이있는 모듈은 나중에 교체 할 수 있습니다.

8087 숫자 데이터 프로세서는 Math co-processor, Numeric processor extension 과 Floating point unit. 인텔이 8086/8088과 쌍을 이루도록 설계 한 최초의 수학 보조 프로세서로 더 쉽고 빠른 계산이 가능합니다.

명령이 8086/8088 프로세서에 의해 식별되면 추가 실행을 위해 8087 코 프로세서에 할당됩니다.

8087에서 지원하는 데이터 유형은 다음과 같습니다.

- 이진 정수

- 패킹 된 십진수

- 실수

- 임시 실제 형식

8087 숫자 데이터 프로세서의 가장 눈에 띄는 기능은 다음과 같습니다-

정수형, 부동 형, 2-10 바이트 범위의 실수 형 데이터를 지원합니다.

처리 속도가 너무 빨라서 2 개의 64 비트 실수의 곱셈을 ~ 27µs에서 계산할 수 있고 제곱근을 ~ 35µs에서 계산할 수도 있습니다.

IEEE 부동 소수점 표준을 따릅니다.

8087 아키텍처

8087 아키텍처는 두 그룹으로 나뉩니다. Control Unit (CU) 및 Numeric Extension Unit (NEU).

그만큼 control unit 명령을 수신 및 디코딩하고, 메모리 피연산자를 읽고 쓰고, 병렬 대기열을 유지하는 등 프로세서와 메모리 간의 모든 통신을 처리합니다. 모든 보조 프로세서 명령은 ESC 명령입니다. 즉, 보조 프로세서 만 'F'로 시작합니다. 다른 명령은 마이크로 프로세서에 의해 실행되는 동안 ESC 명령을 실행합니다.

그만큼 numeric extension unit산술, 논리, 초월 및 데이터 전송 명령과 같은 모든 숫자 프로세서 명령을 처리합니다. 명령어와 그 결과에 대한 피연산자를 보유하는 8 개의 레지스터 스택이 있습니다.

8087 코 프로세서의 아키텍처는 다음과 같습니다.

8087 핀 설명

먼저 8087의 핀 다이어그램을 살펴 보겠습니다.

다음 목록은 8087의 핀 설명을 제공합니다.

AD0 – AD15 − 이들은 시간 다중화 된 주소 / 데이터 라인으로, 첫 번째 클록 사이클 동안 주소를 전달하고 두 번째 클록 사이클 이후의 데이터를 전달합니다.

A19 / S6 – A16/S−이 라인은 시간 다중화 된 주소 / 상태 라인입니다. 8086의 해당 핀과 유사한 방식으로 작동합니다. S 6 , S 4 및 S3는 영구적으로 높고 S 5 는 영구적으로 낮습니다.

$\overline{BHE}$/S7 − 첫 번째 클럭주기 동안 $\overline{BHE}$/ S 7 은 8086 데이터 버스의 상위 바이트에 데이터를 활성화하는 데 사용되며 그 이후 상태 라인 S 7 로 작동합니다 .

QS1, QS0 − 다음 표에 표시된대로 명령어 대기열의 상태와 해당 조건을 제공하는 대기열 상태 입력 신호입니다.

| QS 0 | 질문 1 | 상태 |

|---|---|---|

| 0 | 0 | 작동하지 않음 |

| 0 | 1 | 대기열의 첫 번째 opcode 바이트 |

| 1 | 0 | 대기열 비우기 |

| 1 | 1 | 큐의 후속 바이트 |

INT − 실행 중에 마스크되지 않은 예외가 수신되면 high로 변경되는 인터럽트 신호입니다.

BUSY − 출력 신호이며 높으면 CPU에 사용 중임을 나타냅니다.

READY − 버스가 데이터를 수신 할 준비가되었는지 여부를 코 프로세서에 알리는 데 사용되는 입력 신호입니다.

RESET − 코 프로세서의 내부 활동을 거부하고 CPU에서 필요할 때마다 추가 실행을 준비하는 데 사용되는 입력 신호입니다.

CLK − CLK 입력은 프로세서 작동을위한 기본 타이밍을 제공합니다.

VCC − 전원 공급 신호이며 회로 작동을 위해 + 5V 공급이 필요합니다.

S0, S1, S2− 이들은 메모리 및 I / O 제어 신호를 생성하기 위해 버스 컨트롤러 8087에 의해 사용되는 작동 상태를 제공하는 상태 신호입니다. 이러한 신호는 네 번째 클럭주기 동안 활성화됩니다.

| S 2 | S 1 | S 0 | 대기열 상태 |

|---|---|---|---|

| 0 | 엑스 | 엑스 | 미사용 |

| 1 | 0 | 0 | 미사용 |

| 1 | 0 | 1 | 메모리 읽기 |

| 1 | 1 | 0 | 메모리 쓰기 |

| 1 | 1 | 1 | 수동태 |

RQ/GT1 & RQ/GT0 − 이것들은 Request/Grant 피연산자 전송을 위해 호스트 프로세서 8086/8088에서 버스를 제어하기 위해 8087 프로세서가 사용하는 신호.

이 장에서는 8085를 사용한 메모리 인터페이싱 및 IO 인터페이싱에 대해 설명합니다.

Interface두 구성 요소 간의 통신 경로입니다. 인터페이싱은 메모리 인터페이싱과 I / O 인터페이싱의 두 가지 유형입니다.

메모리 인터페이스

명령을 실행할 때 명령 코드와 메모리에 저장된 데이터를 읽기 위해 메모리에 액세스하려면 마이크로 프로세서가 필요합니다. 이를 위해 메모리와 마이크로 프로세서 모두 레지스터에서 읽고 쓰는 데 약간의 신호가 필요합니다.

인터페이싱 프로세스에는 메모리 요구 사항 및 마이크로 프로세서 신호와 일치하는 몇 가지 핵심 요소가 포함됩니다. 따라서 인터페이스 회로는 메모리 신호 요구 사항을 마이크로 프로세서의 신호와 일치시키는 방식으로 설계되어야합니다.

IO 인터페이스

키보드, 마우스, 프린터 등과 같은 다양한 통신 장치가 있습니다. 따라서 래치와 버퍼를 사용하여 키보드 및 기타 장치를 마이크로 프로세서와 인터페이스해야합니다. 이러한 유형의 인터페이싱을 I / O 인터페이싱이라고합니다.

메모리 및 I / O 인터페이스의 블록 다이어그램

8085 인터페이스 핀

다음은 다른 장치와의 인터페이스에 사용되는 8085 핀 목록입니다.

- A 15 -A 8 (상위 주소 버스)

- AD 7 -AD 0 (하위 주소 / 데이터 버스)

- ALE

- RD

- WR

- READY

통신 방법-외부 세계와의 마이크로 프로세서?

마이크로 프로세서가 외부 세계와 연결할 수있는 통신 방법에는 두 가지가 있습니다.

- 직렬 통신 인터페이스

- 병렬 통신 인터페이스

Serial Communication Interface − 이러한 유형의 통신에서 인터페이스는 마이크로 프로세서에서 단일 바이트의 데이터를 가져 와서 비트 단위로 다른 시스템에 직렬로 또는 그 반대로 전송합니다.

Parallel Communication Interface − 이러한 유형의 통신에서 인터페이스는 마이크로 프로세서로부터 데이터 바이트를 가져 와서 동시에 (또는) 병렬 방식으로 또는 그 반대로 비트 단위로 다른 시스템에 전송합니다.

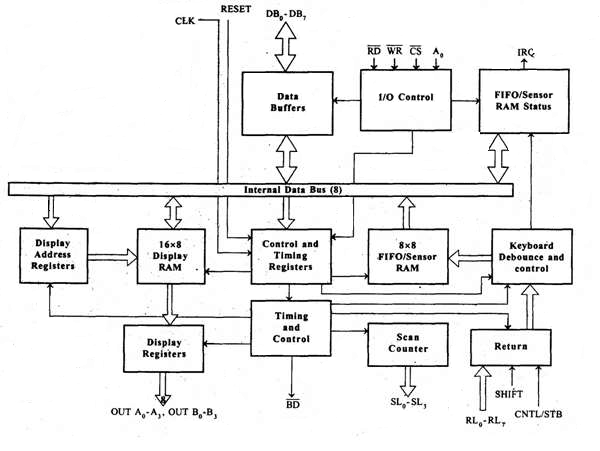

8279 프로그래밍 가능 키보드 / 디스플레이 컨트롤러는 키보드와 CPU를 연결하는 Intel에서 설계했습니다. 키보드는 먼저 키보드를 스캔하여 키가 눌 렸는지 확인합니다. 그런 다음 누른 키의 상대 응답을 CPU로 전송하고 그 반대의 경우도 마찬가지입니다.

키보드는 CPU와 몇 가지 방식으로 인터페이스됩니까?

키보드는 인터럽트 또는 폴링 모드에서 인터페이스 할 수 있습니다. 에서Interrupt mode, 프로세서는 키를 눌렀을 때만 서비스를 요청합니다. 그렇지 않으면 CPU가 주 작업을 계속합니다.

에서 Polled mode, CPU는 주기적으로 8279의 내부 플래그를 읽고 키 압력으로 키를 눌렀는지 여부를 확인합니다.

8279 키보드는 어떻게 작동합니까?

키보드는 최대 64 개의 키로 구성되며 키 코드를 사용하여 CPU와 인터페이스됩니다. 이러한 키 코드는 디 바운스되고 CPU에서 액세스 할 수있는 8 바이트 FIFORAM에 저장됩니다. FIFO에 8 개 이상의 문자가 입력 된 경우 한 번에 8 개 이상의 키를 눌렀 음을 의미합니다. 오버런 상태가 설정되었을 때입니다.

FIFO에 유효한 키 항목이 포함되어 있으면 CPU가 인터럽트 모드에서 중단되고 그렇지 않으면 CPU가 항목을 읽기 위해 폴링 상태를 확인합니다. CPU가 키 항목을 읽으면 FIFO가 업데이트되고 새 항목을위한 공간을 생성하기 위해 키 항목이 FIFO 밖으로 푸시됩니다.

아키텍처 및 설명

I / O 제어 및 데이터 버퍼

이 장치는 마이크로 프로세서를 통한 데이터 흐름을 제어합니다. D가 낮을 때만 활성화됩니다. 데이터 버퍼는 시스템의 외부 버스와 마이크로 프로세서의 내부 버스를 연결합니다. 핀 A0, RD 및 WR은 명령, 상태 또는 데이터 읽기 / 쓰기 작업에 사용됩니다.

제어 및 타이밍 레지스터 및 타이밍 제어

이 장치에는 키보드, 디스플레이 모드 및 CPU에 의해 프로그래밍 된 기타 작업을 저장하는 레지스터가 포함되어 있습니다. 타이밍 및 제어 장치는 회로 작동을위한 타이밍을 처리합니다.

카운터 스캔

두 가지 모드가 있습니다. Encoded mode및 디코딩 모드. 인코딩 모드에서 카운터는 키보드 및 디스플레이에 대한 스캔 라인을 제공하기 위해 외부에서 디코딩 할 이진 카운트를 제공합니다.

에서 decoded scan mode카운터는 내부의 최하위 2 개 비트를 디코딩하고, 디코딩 한 주사 SL에 4에서 제공 0 -SL 3 .

리턴 버퍼, 키보드 디 바운스 및 제어

이 장치는 먼저 키 클로저를 행 방향으로 스캔하고 발견되면 키보드 디 바운스 장치가 키 입력을 디 바운스합니다. 동일한 키가 감지되면 해당 키의 코드가 SHIFT & CONTROL 키 상태와 함께 센서 RAM으로 직접 전송됩니다.

FIFO / 센서 RAM 및 상태 로직

이 장치는 8 바이트 FIFO (First-in-First-Out) RAM으로 작동하며, 누른 모든 키의 키 코드가 순서에 따라 RAM에 입력됩니다. 상태 로직은 FIFO가 비워 질 때까지 각 FIFO 읽기 작업 후에 인터럽트 요청을 생성합니다.

스캔 된 센서 매트릭스 모드에서이 장치는 각 행이 해당 센서 행의 상태와 함께 매트릭스에로드되는 센서 RAM 역할을합니다. 센서가 상태를 변경하면 IRQ 라인이 high로 변경되고 CPU가 중단됩니다.

주소 레지스터 표시 및 RAM 표시

이 장치는 현재 CPU가 디스플레이 RAM에서 읽고 쓰는 워드의 주소를 보유하는 디스플레이 주소 레지스터로 구성됩니다.

8279 − 핀 설명

다음 그림은 8279의 핀 다이어그램을 보여줍니다.

데이터 버스 라인, DB 0 -DB 7

이들은 CPU와 데이터를주고받는 데 사용되는 8 개의 양방향 데이터 버스 라인입니다.

CLK

클록 입력은 마이크로 프로세서에 필요한 내부 타이밍을 생성하는 데 사용됩니다.

초기화

이름에서 알 수 있듯이이 핀은 마이크로 프로세서를 재설정하는 데 사용됩니다.

CS 칩 선택

이 핀이 로우로 설정되면 읽기 / 쓰기 작업이 가능하며, 그렇지 않으면이 핀을 하이로 설정해야합니다.

A 0

이 핀은 명령 / 상태 정보의 전송을 나타냅니다. 낮 으면 데이터 전송을 나타냅니다.

RD, WR

이 읽기 / 쓰기 핀은 데이터 버퍼가 데이터 버스를 통해 데이터를 송수신 할 수 있도록합니다.

IRQ

이 인터럽트 출력 라인은 FIFO 센서 RAM에 데이터가있을 때 하이가됩니다. 인터럽트 라인은 각 FIFO RAM 읽기 작업과 함께 낮아집니다. 그러나 FIFO RAM에 CPU가 읽을 키 코드 항목이 더 포함되어 있으면이 핀이 다시 높아져 CPU에 인터럽트를 생성합니다.

V ss , V cc

이들은 마이크로 프로세서의 접지 및 전원 공급 라인입니다.

SL 0 ~ SL 3

키보드 매트릭스를 스캔하고 숫자를 표시하는 데 사용되는 스캔 라인입니다. 이러한 라인은 모드 제어 레지스터를 사용하여 인코딩 또는 디코딩으로 프로그래밍 할 수 있습니다.

RL 0 ~ RL 7

이들은 키의 한 터미널에 연결된 리턴 라인이고 키의 다른 터미널은 디코딩 된 스캔 라인에 연결됩니다. 이 행은 아무 키나 누르면 0으로 설정됩니다.

시프트

Shift 입력 라인 상태는 스캔 된 키보드 모드에서 FIFO의 모든 키 코드와 함께 저장됩니다. 키 잠금으로 낮게 당겨질 때까지 내부적으로 당겨서 높게 유지합니다.

CNTL / STB-CONTROL / STROBED I / P 모드

키보드 모드에서이 라인은 컨트롤 입력으로 사용되며 키를 닫을 때 FIFO에 저장됩니다. 라인은 스트로브 입력 모드에서 FIFO RAM에 데이터를 입력하는 스트로브 라인입니다. 내부 풀업이 있습니다. 라인은 키 클로저로 당겨집니다.

BD

빈 디스플레이를 의미합니다. 숫자 전환 중에 디스플레이를 비우는 데 사용됩니다.

OUTA 0 – OUTA 3 및 OUTB 0 – OUTB 3

이것은 2 개의 16x4 또는 1 개의 16x8 내부 디스플레이 새로 고침 레지스터에 대한 출력 포트입니다. 이 라인의 데이터는 스캔 라인과 동기화되어 디스플레이와 키보드를 스캔합니다.

8279의 작동 모드

8279에는 두 가지 작동 모드가 있습니다. Input Mode 과 Output Mode.

입력 모드

이 모드는 키보드로 입력되는 입력을 처리하며이 모드는 세 가지 모드로 더 분류됩니다.

Scanned Keyboard Mode−이 모드에서 키 매트릭스는 인코딩 또는 디코딩 된 스캔을 사용하여 인터페이스 될 수 있습니다. 인코딩 된 스캔, 8x8 키보드 또는 디코딩 된 스캔에서 4x8 키보드가 인터페이스 될 수 있습니다. SHIFT 및 CONTROL 상태로 누른 키의 코드는 FIFO RAM에 저장됩니다.

Scanned Sensor Matrix−이 모드에서 센서 어레이는 인코더 또는 디코더 스캔을 사용하여 프로세서와 인터페이스 할 수 있습니다. 인코더 스캔에서 8x8 센서 매트릭스 또는 디코더 스캔 4x8 센서 매트릭스를 인터페이스 할 수 있습니다.

Strobed Input −이 모드에서 제어 라인이 0으로 설정되면 리턴 라인의 데이터가 FIFO byte 단위로 저장됩니다.

출력 모드

이 모드는 디스플레이 관련 작업을 다룹니다. 이 모드는 두 가지 출력 모드로 더 분류됩니다.

Display Scan −이 모드에서는 8/16 문자 다중 디스플레이를 듀얼 4 비트 / 단일 8 비트 디스플레이 장치로 구성 할 수 있습니다.

Display Entry −이 모드에서는 데이터를 오른쪽 / 왼쪽에서 표시하기 위해 입력 할 수 있습니다.

DMA는 Direct Memory Access를 나타냅니다. 인텔에서 가장 빠른 속도로 데이터를 전송하도록 설계되었습니다. 이를 통해 장치는 CPU의 간섭없이 메모리와 직접 데이터를 전송할 수 있습니다.

DMA 컨트롤러를 사용하여 장치는 CPU에 데이터, 주소 및 제어 버스를 보유하도록 요청하므로 장치는 메모리에서 직접 데이터를 자유롭게 전송할 수 있습니다. DMA 데이터 전송은 CPU에서 HLDA 신호를 수신 한 후에 만 시작됩니다.

DMA 작업은 어떻게 수행됩니까?

다음은 DMA에 의해 수행되는 일련의 작업입니다.

처음에는 장치가 장치와 메모리간에 데이터를 보내야 할 때 장치가 DMA 컨트롤러에 DMA 요청 (DRQ)을 보내야합니다.

DMA 컨트롤러는 CPU에 HRQ (Hold request)를 보내고 CPU가 HLDA를 선언 할 때까지 기다립니다.

그런 다음 마이크로 프로세서는 모든 데이터 버스, 주소 버스 및 제어 버스를 3 중 상태로 만듭니다. CPU는 버스 제어를 떠나 HLDA 신호를 통해 HOLD 요청을 승인합니다.

이제 CPU는 HOLD 상태에 있으며 DMA 컨트롤러는 CPU, 메모리 및 I / O 장치 간의 버스를 통한 작업을 관리해야합니다.

8257의 특징

다음은 8257의 눈에 띄는 기능의 목록입니다.

4 개의 I / O 장치에서 사용할 수있는 4 개의 채널이 있습니다.

각 채널에는 16 비트 주소와 14 비트 카운터가 있습니다.

각 채널은 최대 64kb의 데이터를 전송할 수 있습니다.

각 채널은 독립적으로 프로그래밍 할 수 있습니다.

각 채널은 읽기 전송, 쓰기 전송을 수행하고 전송 작업을 확인할 수 있습니다.

128 바이트가 전송 된 주변기기에 MARK 신호를 생성합니다.

단상 클럭이 필요합니다.

주파수 범위는 250Hz에서 3MHz입니다.

2 가지 모드로 작동합니다. Master mode 과 Slave mode.

8257 아키텍처

다음 이미지는 8257의 아키텍처를 보여줍니다-

8257 핀 설명

다음 이미지는 8257 DMA 컨트롤러의 핀 다이어그램을 보여줍니다.

DRQ 0 -DRQ3

이는 4 개의 개별 채널 DMA 요청 입력으로, 주변 장치에서 DMA 서비스를 사용하는 데 사용됩니다. 고정 우선 순위 모드를 선택하면 DRQ 0 이 가장 높은 우선 순위를 가지며 DRQ 3 이 가장 낮은 우선 순위를 갖습니다.

DACK o -DACK 3

이들은 CPU에 의한 요청 상태에 대한 요청 주변 장치를 업데이트하는 액티브 로우 DMA 승인 라인입니다. 이러한 라인은 요청 장치에 대한 스트로브 라인으로도 작동 할 수 있습니다.

D o − D 7

시스템 버스를 DMA 컨트롤러의 내부 데이터 버스와 인터페이스하는 데 사용되는 양방향 데이터 라인입니다. Slave 모드에서는 명령어를 8257로, 상태 어를 8257로 전달합니다. 마스터 모드에서이 라인은 생성 된 주소의 상위 바이트를 래치로 전송하는 데 사용됩니다. 이 주소는 ADSTB 신호를 사용하여 추가로 래치됩니다.

IOR

이는 CPU가 슬레이브 모드에서 8257의 내부 레지스터를 읽는 데 사용하는 액티브 로우 양방향 3 상태 입력 라인입니다. 마스터 모드에서는 메모리 쓰기주기 동안 주변 장치에서 데이터를 읽는 데 사용됩니다.

IOW

데이터 버스의 내용을 8 비트 모드 레지스터 또는 16 비트 DMA 주소 레지스터 또는 터미널 카운트 레지스터의 상위 / 하위 바이트로로드하는 데 사용되는 활성 낮은 양방향 3 상태 라인입니다. 마스터 모드에서는 DMA 메모리 읽기주기 동안 주변 장치에 데이터를로드하는 데 사용됩니다.

CLK

8257의 내부 동작에 필요한 클럭 주파수 신호입니다.

초기화

이 신호는 모든 DMA 채널을 비활성화하여 DMA 컨트롤러를 재설정하는 데 사용됩니다.

A o -A 3

4 개의 최하위 주소 행입니다. 슬레이브 모드에서는 읽기 또는 쓰기 할 레지스터 중 하나를 선택하는 입력 역할을합니다. 마스터 모드에서는 8257에 의해 생성 된 4 개의 최하위 메모리 주소 출력 라인입니다.

CS

액티브 로우 칩 셀렉트 라인입니다. 슬레이브 모드에서는 8257과의 읽기 / 쓰기 작업을 활성화합니다. 마스터 모드에서는 8257과의 읽기 / 쓰기 작업을 비활성화합니다.

4 - 7

이들은 마스터 모드에서 DMA에 의해 생성 된 하위 바이트 주소의 상위 니블입니다.

준비된

대기 상태를 삽입하여 DMA를 준비하는 액티브 하이 비동기 입력 신호입니다.

HRQ

이 신호는 출력 장치에서 보류 요청 신호를 수신하는 데 사용됩니다. 슬레이브 모드에서는 DRQ 입력 라인 8257과 연결됩니다. 마스터 모드에서는 CPU의 HOLD 입력과 연결됩니다.

HLDA

1로 설정된 경우 CPU가 요청하는 주변 장치에 버스를 부여했음을 DMA 컨트롤러에 표시하는 보류 확인 신호입니다.

MEMR

DMA 읽기주기 동안 주소 지정된 메모리 위치에서 데이터를 읽는 데 사용되는 낮은 메모리 읽기 신호입니다.

MEMW

DMA 쓰기 작업 중에 주소가 지정된 메모리 위치에 데이터를 쓰는 데 사용되는 액티브 로우 3 상태 신호입니다.

ADST

이 신호는 DMA 컨트롤러에 의해 생성 된 메모리 주소의 상위 바이트를 래치로 변환하는 데 사용됩니다.

AEN

이 신호는 주소 버스 / 데이터 버스를 비활성화하는 데 사용됩니다.

TC

현재 주변 장치에 대한 현재 DMA주기를 나타내는 'Terminal Count'를 의미합니다.

표

마크는 처음부터 각 128 사이클 또는 적분 배수 후에 활성화됩니다. 현재 DMA 사이클이 선택한 주변 장치에 대한 이전 MARK 출력 이후 128 번째 사이클임을 나타냅니다.

V cc

회로 작동에 필요한 전원 신호입니다.

ㅏ microcontroller 마이크로파 정보 표시, 원격 신호 수신 등과 같은 임베디드 시스템의 특정 작업을 수행하도록 설계된 작고 저렴한 마이크로 컴퓨터입니다.

일반 마이크로 컨트롤러는 프로세서, 메모리 (RAM, ROM, EPROM), 직렬 포트, 주변 장치 (타이머, 카운터) 등으로 구성됩니다.

마이크로 프로세서와 마이크로 컨트롤러의 차이점

다음 표는 마이크로 프로세서와 마이크로 컨트롤러의 차이점을 강조합니다.

| 마이크로 컨트롤러 | 마이크로 프로세서 |

|---|---|

| 마이크로 컨트롤러는 애플리케이션 내에서 단일 작업을 실행하는 데 사용됩니다. | 마이크로 프로세서는 대형 애플리케이션에 사용됩니다. |

| 설계 및 하드웨어 비용이 저렴합니다. | 설계 및 하드웨어 비용이 높습니다. |

| 교체가 쉽습니다. | 교체하기가 쉽지 않습니다. |

| 작동하는 데 필요한 전력이 적은 CMOS 기술로 제작되었습니다. | 전체 시스템을 제어해야하기 때문에 전력 소모가 높습니다. |

| CPU, RAM, ROM, I / O 포트로 구성됩니다. | RAM, ROM, I / O 포트로 구성되지 않습니다. 핀을 사용하여 주변 장치에 인터페이스합니다. |

마이크로 컨트롤러의 유형

마이크로 컨트롤러는 메모리, 아키텍처, 비트 및 명령어 세트에 따라 다양한 범주로 나뉩니다. 다음은 유형의 목록입니다-

비트

비트 구성에 따라 마이크로 컨트롤러는 세 가지 범주로 더 나뉩니다.

8-bit microcontroller −이 유형의 마이크로 컨트롤러는 더하기, 빼기, 곱하기 나누기 등과 같은 산술 및 논리 연산을 실행하는 데 사용됩니다. 예를 들어, Intel 8031 및 8051은 8 비트 마이크로 컨트롤러입니다.

16-bit microcontroller−이 유형의 마이크로 컨트롤러는 더 높은 정확도와 성능이 필요한 산술 및 논리 연산을 수행하는 데 사용됩니다. 예를 들어 Intel 8096은 16 비트 마이크로 컨트롤러입니다.

32-bit microcontroller −이 유형의 마이크로 컨트롤러는 일반적으로 자동 작동 기계, 의료 기기 등과 같은 자동 제어 기기에 사용됩니다.

기억

메모리 구성에 따라 마이크로 컨트롤러는 두 가지 범주로 더 나뉩니다.

External memory microcontroller−이 유형의 마이크로 컨트롤러는 칩에 프로그램 메모리가없는 방식으로 설계되었습니다. 따라서 외부 메모리 마이크로 컨트롤러로 명명됩니다. 예 : Intel 8031 마이크로 컨트롤러.

Embedded memory microcontroller−이 유형의 마이크로 컨트롤러는 마이크로 컨트롤러가 모든 프로그램과 데이터 메모리, 카운터 및 타이머, 인터럽트, I / O 포트가 칩에 내장되도록 설계되었습니다. 예 : Intel 8051 마이크로 컨트롤러.

명령어 세트

명령 세트 구성에 따라 마이크로 컨트롤러는 두 가지 범주로 더 나뉩니다.

CISC− CISC는 복잡한 명령어 세트 컴퓨터를 나타냅니다. 이를 통해 사용자는 여러 간단한 명령 대신 단일 명령을 삽입 할 수 있습니다.

RISC− RISC는 Reduced Instruction Set Computers를 의미합니다. 명령어 당 클럭 사이클을 단축하여 작동 시간을 단축합니다.

마이크로 컨트롤러의 응용

마이크로 컨트롤러는 다음과 같은 다양한 장치에서 널리 사용됩니다.

LED와 같은 빛 감지 및 제어 장치.

전자 레인지, 굴뚝과 같은 온도 감지 및 제어 장치.

화재 경보와 같은 화재 감지 및 안전 장치.

전압계와 같은 측정 장치.

8051 마이크로 컨트롤러는 1981 년 인텔에서 설계했습니다. 이것은 8 비트 마이크로 컨트롤러입니다. 40 핀 DIP (듀얼 인라인 패키지), 4kb의 ROM 스토리지 및 128 바이트의 RAM 스토리지, 2 개의 16 비트 타이머로 제작되었습니다. 4 개의 병렬 8 비트 포트로 구성되어 있으며 요구 사항에 따라 프로그래밍 및 주소 지정이 가능합니다. 온칩 수정 발진기는 수정 주파수가 12MHz 인 마이크로 컨트롤러에 통합되어 있습니다.

이제 8051 마이크로 컨트롤러의 아키텍처를 살펴 보겠습니다.

다음 다이어그램에서 시스템 버스는 모든 지원 장치를 CPU에 연결합니다. 시스템 버스는 8 비트 데이터 버스, 16 비트 주소 버스 및 버스 제어 신호로 구성됩니다. 프로그램 메모리, 포트, 데이터 메모리, 직렬 인터페이스, 인터럽트 제어, 타이머 및 CPU와 같은 다른 모든 장치는 모두 시스템 버스를 통해 함께 인터페이스됩니다.

8051 마이크로 컨트롤러의 핀 다이어그램은 다음과 같습니다.

Pins 1 to 8−이 핀은 포트 1로 알려져 있습니다.이 포트는 다른 기능을 제공하지 않습니다. 내부적으로 풀업 된 양방향 I / O 포트입니다.

Pin 9 − 마이크로 컨트롤러를 초기 값으로 재설정하는 데 사용되는 RESET 핀입니다.

Pins 10 to 17 −이 핀을 포트 3이라고합니다.이 포트는 인터럽트, 타이머 입력, 제어 신호, 직렬 통신 신호 RxD 및 TxD 등과 같은 일부 기능을 제공합니다.

Pins 18 & 19 −이 핀은 시스템 클록을 얻기 위해 외부 크리스털을 인터페이스하는 데 사용됩니다.

Pin 20 −이 핀은 회로에 전원을 공급합니다.

Pins 21 to 28−이 핀을 포트 2라고합니다. I / O 포트 역할을합니다. 고차 주소 버스 신호도이 포트를 사용하여 다중화됩니다.

Pin 29− 이것은 Program Store Enable을 나타내는 PSEN 핀입니다. 외부 프로그램 메모리에서 신호를 읽는 데 사용됩니다.

Pin 30− 외부 액세스 입력을 나타내는 EA 핀입니다. 외부 메모리 인터페이스를 활성화 / 비활성화하는 데 사용됩니다.

Pin 31− Address Latch Enable을 나타내는 ALE 핀입니다. 포트의 주소-데이터 신호를 역 다중화하는데 사용됩니다.

Pins 32 to 39−이 핀은 포트 0으로 알려져 있습니다. I / O 포트 역할을합니다. 하위 주소 및 데이터 버스 신호는이 포트를 사용하여 다중화됩니다.

Pin 40 −이 핀은 회로에 전원을 공급하는 데 사용됩니다.

8051 마이크로 컨트롤러에는 입력 또는 출력으로 구성 할 수있는 각각 8 비트의 I / O 포트가 4 개 있습니다. 따라서 총 32 개의 입력 / 출력 핀을 사용하여 마이크로 컨트롤러를 주변 장치와 연결할 수 있습니다.

Pin configuration즉, 핀은 로직 상태에 따라 입력 용 1과 출력용 0으로 구성 할 수 있습니다.

Input/Output (I/O) pin − 마이크로 컨트롤러 내의 모든 회로는 풀업 저항이 내장되어 있지 않으므로 P0 포트를 제외한 핀 중 하나에 연결해야합니다.

Input pin− 로직 1은 P 레지스터의 비트에 적용됩니다. 출력 FE 트랜지스터는 꺼지고 다른 핀은 높은 저항의 풀업 저항을 통해 전원 공급 장치 전압에 연결된 상태로 유지됩니다.

Port 0 − P0 (영) 포트는 두 가지 기능이 특징입니다 −

외부 메모리를 사용하면 하위 주소 바이트 (주소 A0A7)가 적용되고, 그렇지 않으면이 포트의 모든 비트가 입 / 출력으로 구성됩니다.

P0 포트가 출력으로 구성되고 풀업 저항이 내장 된 핀으로 구성된 다른 포트가 끝으로 5V 전원 공급 장치에 연결된 경우이 포트의 핀에는이 저항이 제외됩니다.

입력 구성

이 포트의 핀이 입력으로 구성되면 "부동"하는 것처럼 작동합니다. 즉, 입력에 무제한 입력 저항과 결정된 전위가 있습니다.

출력 구성

핀이 출력으로 구성되면 "오픈 드레인"으로 작동합니다. 로직 0을 포트 비트에 적용하면 해당 핀이 접지 (0V)에 연결되고 로직 1을 적용하면 외부 출력이 "플로팅"상태를 유지합니다.

이 출력 핀에 로직 1 (5V)을 적용하려면 외부 풀업 저항을 구축해야합니다.

포트 1

P1은 P0에서와 같이 대체 기능이 없기 때문에 진정한 I / O 포트이지만이 포트는 일반 I / O로만 구성 할 수 있습니다. 풀업 저항이 내장되어 있으며 TTL 회로와 완벽하게 호환됩니다.

포트 2

P2는 외부 메모리를 사용할 때 P0과 유사합니다. 이 포트의 핀은 외부 메모리 칩용 주소를 차지합니다. 이 포트는 주소가 A8-A15 인 상위 주소 바이트에 사용할 수 있습니다. 메모리가 추가되지 않은 경우이 포트는 포트 1과 유사한 일반 입출력 포트로 사용할 수 있습니다.

포트 3

이 포트에서 기능은 로직 1이 P3 레지스터의 적절한 비트에 적용되어야한다는 점을 제외하면 다른 포트와 유사합니다.

핀 전류 제한

핀이 출력 (예 : 로직 0)으로 구성되면 단일 포트 핀은 10mA의 전류를 수신 할 수 있습니다.

이러한 핀이 입력 (예 : 로직 1)으로 구성되면 내장 풀업 저항이 매우 약한 전류를 제공하지만 LS 시리즈의 TTL 입력을 최대 4 개까지 활성화 할 수 있습니다.

포트의 8 비트가 모두 활성화 된 경우 총 전류는 15mA (포트 P0 : 26mA)로 제한되어야합니다.

모든 포트 (32 비트)가 활성화 된 경우 총 최대 전류는 71mA로 제한되어야합니다.

인터럽트는 주 프로그램을 일시적으로 중단하고 제어를 외부 소스로 전달하고 작업을 실행하는 이벤트입니다. 그런 다음 중단 된 주 프로그램으로 제어를 전달합니다.

8051에는 INT0, TFO, INT1, TF1, RI / TI의 5 가지 인터럽트 신호가 있습니다. 각 인터럽트는 IE 레지스터의 비트를 설정하여 활성화 또는 비활성화 할 수 있으며 전체 인터럽트 시스템은 동일한 레지스터의 EA 비트를 삭제하여 비활성화 할 수 있습니다.

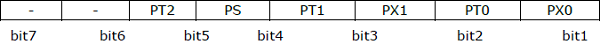

IE (Interrupt Enable) 레지스터

이 레지스터는 인터럽트를 활성화 및 비활성화하는 역할을합니다. EA 레지스터는 인터럽트를 활성화하려면 1로 설정되고 인터럽트를 비활성화하려면 0으로 설정됩니다. 다음 그림은 비트 시퀀스와 의미를 보여줍니다.

| EA | IE.7 | 모든 인터럽트를 비활성화합니다. EA = 0이면 인터럽트가 인식되지 않고 EA = 1은 인터럽트를 개별적으로 활성화합니다. |

| - | IE.6 | 향후 사용을 위해 예약되었습니다. |

| - | IE.5 | 향후 사용을 위해 예약되었습니다. |

| ES | IE.4 | 직렬 포트 인터럽트를 활성화 / 비활성화합니다. |

| ET1 | IE.3 | timer1 오버플로 인터럽트를 활성화 / 비활성화합니다. |

| EX1 | IE.2 | 외부 인터럽트 1을 활성화 / 비활성화합니다. |

| ET0 | IE.1 | timer0 오버플로 인터럽트를 활성화 / 비활성화합니다. |

| EX0 | IE.0 | 외부 인터럽트 0을 활성화 / 비활성화합니다. |

IP (Interrupt Priority) 레지스터

다음 그림과 같이 IP (인터럽트 우선 순위) 레지스터에서 해당 비트를 변경하여 인터럽트의 우선 순위 수준을 변경할 수 있습니다.

낮은 우선 순위 인터럽트는 높은 우선 순위 인터럽트에 의해서만 인터럽트 될 수 있으며 다른 낮은 우선 순위 인터럽트에 의해 인터럽트되지 않습니다.

서로 다른 우선 순위 레벨의 두 인터럽트가 동시에 수신되면 더 높은 우선 순위 레벨의 요청이 제공됩니다.

동일한 우선 순위 레벨의 요청이 동시에 수신되는 경우 내부 폴링 시퀀스는 서비스 할 요청을 결정합니다.

| - | IP.6 | 향후 사용을 위해 예약되었습니다. |

| - | IP.5 | 향후 사용을 위해 예약되었습니다. |

| 추신 | IP.4 | 직렬 포트 인터럽트 우선 순위 수준을 정의합니다. |

| PT1 | IP.3 | 1 우선 순위의 타이머 인터럽트를 정의합니다. |

| PX1 | IP.2 | 외부 인터럽트 우선 순위 레벨을 정의합니다. |

| PT0 | IP.1 | 그것은 timer0 인터럽트 우선 순위 레벨을 정의합니다. |

| PX0 | IP.0 | 0 우선 순위 레벨의 외부 인터럽트를 정의합니다. |

TCON 등록

TCON 레지스터는 마이크로 컨트롤러에 대한 외부 인터럽트 유형을 지정합니다.

8255A는 필요에 따라 특정 조건에서 I / O에서 인터럽트 I / O로 데이터를 전송하도록 설계된 범용 프로그래밍 가능 I / O 장치입니다. 거의 모든 마이크로 프로세서와 함께 사용할 수 있습니다.

요구 사항에 따라 구성 할 수있는 3 개의 8 비트 양방향 I / O 포트 (24I / O 라인)로 구성됩니다.

8255A의 포트

8255A에는 PORT A, PORT B 및 PORT C의 세 개의 포트가 있습니다.

Port A 8 비트 출력 래치 / 버퍼 1 개와 8 비트 입력 버퍼 1 개를 포함합니다.

Port B PORT A와 유사합니다.

Port C 제어 단어에 의해 PORT C 하부 (PC0-PC3)와 PORT C 상부 (PC7-PC4)의 두 부분으로 나눌 수 있습니다.

이 세 포트는 두 그룹으로 더 나뉩니다. 즉 그룹 A에는 PORT A와 상위 PORT C가 포함됩니다. 그룹 B에는 PORT B와 하위 PORT C가 포함됩니다.이 두 그룹은 세 가지 모드로 프로그래밍 할 수 있습니다. 즉, 첫 번째 모드는 모드로 명명됩니다. 0이면 두 번째 모드는 모드 1로 명명되고 세 번째 모드는 모드 2로 명명됩니다.

작동 모드

8255A에는 세 가지 작동 모드가 있습니다.

Mode 0−이 모드에서 포트 A와 B는 2 개의 8 비트 포트로 사용되고 포트 C는 2 개의 4 비트 포트로 사용됩니다. 각 포트는 입력 모드 또는 출력이 래치되고 입력이 래치되지 않는 출력 모드로 프로그래밍 될 수 있습니다. 포트에는 인터럽트 기능이 없습니다.

Mode 1−이 모드에서 포트 A와 B는 8 비트 I / O 포트로 사용됩니다. 입력 또는 출력 포트로 구성 할 수 있습니다. 각 포트는 포트 C의 3 개 라인을 핸드 셰이크 신호로 사용합니다. 입력 및 출력이 래치됩니다.

Mode 2−이 모드에서 포트 A는 모드 0 또는 모드 1에서 양방향 포트 및 포트 B로 구성 될 수 있습니다. 포트 A는 데이터 전송을위한 핸드 셰이크 신호로 포트 C의 5 개 신호를 사용합니다. 포트 C의 나머지 세 신호는 단순 I / O 또는 포트 B의 핸드 셰이크로 사용할 수 있습니다.

8255A의 특징

8255A의 두드러진 특징은 다음과 같습니다-

3 개의 8 비트 IO 포트 즉, PA, PB 및 PC로 구성됩니다.

주소 / 데이터 버스는 외부에서 demux 처리되어야합니다.

TTL과 호환됩니다.

DC 구동 능력이 향상되었습니다.

8255 아키텍처

다음 그림은 8255A의 아키텍처를 보여줍니다-

먼저 Intel 8255A의 핀 다이어그램을 살펴 보겠습니다.

이제 8255A에서 핀의 기능 설명에 대해 논의하겠습니다.

데이터 버스 버퍼

마이크로 프로세서를 시스템 데이터 버스에 연결하는 데 사용되는 3 상태 8 비트 버퍼입니다. 데이터는 CPU의 명령에 따라 버퍼에 의해 전송되거나 수신됩니다. 제어 단어 및 상태 정보도이 버스를 사용하여 전송됩니다.

읽기 / 쓰기 제어 로직

이 블록은 데이터 / 제어 / 상태 워드의 내부 / 외부 전송을 제어합니다. CPU 주소와 제어 버스의 입력을 받아 두 제어 그룹에 차례로 명령을 내립니다.

CS

Chip Select의 약자입니다. 이 입력의 LOW는 칩을 선택하고 8255A와 CPU 간의 통신을 활성화합니다. 디코딩 된 주소에 연결되고 A 0 & A 1 은 마이크로 프로세서 주소 라인에 연결됩니다.

결과는 다음 조건에 따라 다릅니다.

| CS | A 1 | A 0 | 결과 |

|---|---|---|---|

| 0 | 0 | 0 | 포트 A |

| 0 | 0 | 1 | 포트 B |

| 0 | 1 | 0 | 포트 C |

| 0 | 1 | 1 | 제어 레지스터 |

| 1 | 엑스 | 엑스 | 선택 없음 |

WR

쓰기를 의미합니다. 이 제어 신호는 쓰기 작업을 가능하게합니다. 이 신호가 낮아지면 마이크로 프로세서는 선택된 I / O 포트 또는 제어 레지스터에 기록합니다.

초기화

이것은 액티브 하이 신호입니다. 제어 레지스터를 지우고 모든 포트를 입력 모드로 설정합니다.

RD

읽기를 의미합니다. 이 제어 신호는 읽기 작업을 가능하게합니다. 신호가 낮 으면 마이크로 프로세서는 8255의 선택된 I / O 포트에서 데이터를 읽습니다.

A 0 및 A 1

이러한 입력 신호는 RD, WR 및 제어 신호 중 하나와 함께 작동합니다. 다음은 결과와 함께 다양한 신호를 보여주는 표입니다.

| A 1 | A 0 | RD | WR | CS | 결과 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | Input Operation 포트 A → 데이터 버스 |

| 0 | 1 | 0 | 1 | 0 | 포트 B → 데이터 버스 |

| 1 | 0 | 0 | 1 | 0 | 포트 C → 데이터 버스 |

| 0 | 0 | 1 | 0 | 0 | Output Operation 데이터 버스 → PORT A |

| 0 | 1 | 1 | 0 | 0 | 데이터 버스 → PORT A |

| 1 | 0 | 1 | 0 | 0 | 데이터 버스 → PORT B |

| 1 | 1 | 1 | 0 | 0 | 데이터 버스 → PORT D |

Intel 8253 및 8254는 마이크로 프로세서가 3 개의 16 비트 레지스터를 사용하여 타이밍 및 카운팅 기능을 수행하도록 설계된 PTI (Programmable Interval Timer)입니다. 각 카운터에는 클럭 및 게이트와 같은 2 개의 입력 핀과 "OUT"출력용 1 개의 핀이 있습니다. 카운터를 작동하기 위해 16 비트 카운트가 레지스터에로드됩니다. 명령시 0에 도달 할 때까지 카운트를 줄이기 시작하고 CPU를 중단하는 데 사용할 수있는 펄스를 생성합니다.

8253과 8254의 차이점

다음 표는 8253과 8254의 기능을 구분합니다.

| 8253 | 8254 |

|---|---|

| 작동 주파수는 0 ~ 2.6MHz입니다. | 작동 주파수는 0 ~ 10MHz입니다. |

| N-MOS 기술을 사용합니다. | H-MOS 기술을 사용합니다. |

| Read-Back 명령을 사용할 수 없습니다. | Read-Back 명령을 사용할 수 있습니다. |

| 동일한 카운터의 읽기 및 쓰기는 인터리브 될 수 없습니다. | 동일한 카운터의 읽기 및 쓰기를 인터리브 할 수 있습니다. |

8253/54의 특징

8253/54의 가장 눈에 띄는 기능은 다음과 같습니다.

3 개의 독립적 인 16 비트 다운 카운터가 있습니다.

DC에서 10MHz까지의 입력을 처리 할 수 있습니다.

이 세 카운터는 바이너리 또는 BCD 카운트로 프로그래밍 할 수 있습니다.

거의 모든 마이크로 프로세서와 호환됩니다.

8254에는 READ BACK 명령이라는 강력한 명령이있어 사용자가 카운트 값, 프로그래밍 된 모드, 현재 모드 및 카운터의 현재 상태를 확인할 수 있습니다.

8254 아키텍처

8254의 아키텍처는 다음과 같습니다.

8254 핀 설명

다음은 8254의 핀 다이어그램입니다.

위 그림에는 세 개의 카운터, 데이터 버스 버퍼, 읽기 / 쓰기 제어 로직 및 제어 레지스터가 있습니다. 각 카운터에는 두 개의 입력 신호 (CLOCK & GATE)와 하나의 출력 신호 (OUT)가 있습니다.

데이터 버스 버퍼

3 상태, 양방향, 8 비트 버퍼로 8253/54를 시스템 데이터 버스에 인터페이스하는 데 사용됩니다. 세 가지 기본 기능이 있습니다.

- 8253/54의 모드 프로그래밍.

- 카운트 레지스터를로드합니다.

- 카운트 값 읽기.

논리 읽기 / 쓰기

여기에는 5 개의 신호, 즉 RD, WR, CS 및 주소 라인 A 0 & A 1이 포함 됩니다. 주변기기 I / O 모드에서 RD 및 WR 신호는 각각 IOR 및 IOW에 연결됩니다. 메모리 매핑 된 I / O 모드에서 이들은 MEMR 및 MEMW에 연결됩니다.

CPU의 주소 라인 A 0 및 A 1 은 8253/54의 라인 A 0 및 A 1 에 연결되고 CS는 디코딩 된 주소에 연결됩니다. 제어 워드 레지스터와 카운터는 라인 A 0 & A 1 의 신호에 따라 선택됩니다 .

| A 1 | A 0 | 결과 |

|---|---|---|

| 0 | 0 | 카운터 0 |

| 0 | 1 | 카운터 1 |

| 1 | 0 | 카운터 2 |

| 1 | 1 | 제어 워드 레지스터 |

| 엑스 | 엑스 | 선택 없음 |

제어 워드 레지스터

이 레지스터는 라인 A 0 및 A 1 이 논리 1에 있을 때 액세스됩니다 . 사용할 카운터, 해당 모드 및 읽기 또는 쓰기 작업을 지정하는 명령 워드를 쓰는 데 사용됩니다. 다음 표는 다양한 제어 입력에 대한 결과를 보여줍니다.

| A 1 | A 0 | RD | WR | CS | 결과 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 카운터 0 쓰기 |

| 0 | 1 | 1 | 0 | 0 | 카운터 1 쓰기 |

| 1 | 0 | 1 | 0 | 0 | 카운터 2 쓰기 |

| 1 | 1 | 1 | 0 | 0 | 제어 워드 쓰기 |

| 0 | 0 | 0 | 1 | 0 | 카운터 0 읽기 |

| 0 | 1 | 0 | 1 | 0 | 카운터 1 읽기 |

| 1 | 0 | 0 | 1 | 0 | 카운터 2 읽기 |

| 1 | 1 | 0 | 1 | 0 | 작동하지 않음 |

| 엑스 | 엑스 | 1 | 1 | 0 | 작동하지 않음 |

| 엑스 | 엑스 | 엑스 | 엑스 | 1 | 작동하지 않음 |

카운터

각 카운터는 바이너리 또는 BCD에서 작동 할 수있는 단일 16 비트 다운 카운터로 구성됩니다. 입력 및 출력은 제어 워드 레지스터에 저장된 모드 선택에 의해 구성됩니다. 프로그래머는 처리중인 실제 카운트를 방해하지 않고 세 카운터 중 하나의 내용을 읽을 수 있습니다.

8253/54는 6 가지 모드로 작동 할 수 있습니다. 이 장에서는 이러한 작동 모드에 대해 설명합니다.

모드 0 ─ 터미널 카운트에서 인터럽트

일정 간격 후에 마이크로 프로세서에 인터럽트를 생성하는 데 사용됩니다.

모드가 설정된 후 처음에는 출력이 낮습니다. 카운트 값이 카운터에로드 된 후에도 출력은 LOW로 유지됩니다.

카운터 감소 프로세스는 터미널 카운트에 도달 할 때까지 계속됩니다. 즉, 카운트가 0이되고 출력이 HIGH가되고 새 카운트를 다시로드 할 때까지 하이 상태를 유지합니다.

GATE 신호는 정상 계수를 위해 높습니다. GATE가 낮아지면 카운팅이 종료되고 GATE가 다시 높아질 때까지 현재 카운트가 래치됩니다.

모드 1 – 프로그래밍 가능한 원샷

모노 스 테이블 멀티 바이브레이터로 사용할 수 있습니다.

이 모드에서는 게이트 입력이 트리거 입력으로 사용됩니다.

카운트가로드되고 트리거가 적용될 때까지 출력은 높게 유지됩니다.

모드 2 – 속도 생성기

출력은 일반적으로 초기화 후 높습니다.

카운트가 0이 될 때마다 출력에서 또 다른 로우 펄스가 생성되고 카운터가 다시로드됩니다.

모드 3 – 구형파 생성기

이 모드는 출력이 타이머 기간의 절반 동안 낮고 나머지 절반 동안 높게 유지된다는 점을 제외하면 모드 2와 유사합니다.

모드 4-소프트웨어 트리거 모드

이 모드에서 출력은 타이머가 0으로 카운트 될 때까지 높게 유지되며,이 지점에서 출력은 낮은 펄스를 보낸 다음 다시 높은 값이됩니다.

카운트는 GATE 신호가 LOW가되면 래치됩니다.

터미널 카운트에서 출력은 한 클럭 사이클 동안 로우가 된 다음 HIGH가됩니다. 이 낮은 펄스는 스트로브로 사용할 수 있습니다.

모드 5 – 하드웨어 트리거 모드

이 모드는 외부에서 생성 된 신호에 응답하여 스트로브를 생성합니다.

이 모드는 게이트 입력에서 신호에 의해 카운팅이 시작된다는 점을 제외하면 모드 4와 유사합니다. 즉, 소프트웨어가 트리거되는 대신 하드웨어가 트리거됩니다.

초기화 후 출력이 높아집니다.

터미널 카운트에 도달하면 출력이 한 클록 사이클 동안 낮아집니다.