펄스 회로-퀵 가이드

ㅏ Signal정보를 전달할뿐만 아니라 회로의 상태를 나타냅니다. 회로의 기능은 생성되는 신호에 의해 연구 될 수 있습니다. 따라서 신호에 대한 간략한 소개로이 튜토리얼을 시작합니다.

전자 신호

전자 신호는 무언가를 나타내거나 무언가에 대해 알려주는 일반적인 신호와 유사합니다. 전자 신호의 그래픽 표현은 신호의 진폭 또는 위상과 같은 매개 변수의 주기적 변화에 대한 정보를 제공합니다. 또한 전압, 주파수, 기간 등에 대한 정보를 제공합니다.

이 표현은 전달되는 정보 또는 수신 된 신호에 어떤 형태를 제공합니다. 특정 변화에 따라 형성 될 때 신호의 이러한 모양은 정현파 신호, 삼각 신호, 톱니 신호 및 구형파 신호 등과 같이 다른 이름을 지정할 수 있습니다.

이러한 신호는 주로 단방향 및 양방향 신호라는 두 가지 유형입니다.

Unidirectional Signal − 양 또는 음의 한 방향으로 만 흐르는 신호. 이러한 신호를 단방향 신호라고합니다.

Example − 펄스 신호.

Bidirectional Signal − 영점을 가로 지르는 양의 방향과 음의 방향으로 변경되는 신호. 이러한 신호를 양방향 신호라고합니다.

Example − 정현파 신호.

이 장에서는 펄스 신호와 그 특성에 대해 설명합니다.

펄스 신호

펄스 모양은 기준 값에서 더 높거나 낮은 레벨 값으로의 급격한 일시적인 변화로 형성되며, 특정 시간이 지나면 동일한 기준 값으로 돌아갑니다. 이러한 신호를 펄스 신호라고 할 수 있습니다.

다음 그림은 일련의 펄스를 보여줍니다.

펄스 신호는 정사각형 신호와 유사하지만 구형파와 같이 대칭이 아닌 단방향 비 정현파 신호입니다. 일련의 연속 펄스 신호를 간단히 펄스 트레인이라고합니다. 일련의 펄스는 각각 ON / OFF로 이해 될 수있는 기준 레벨에서 갑작스런 높은 레벨과 갑작스런 낮은 레벨 전환을 나타냅니다.

따라서 펄스 신호는 신호의 ON 및 OFF를 나타냅니다. 전기 스위치에 펄스 입력이 주어지면 주어진 펄스 신호에 따라 ON / OFF됩니다. 펄스 신호를 생성하는 이러한 스위치는 나중에 설명 할 수 있습니다.

펄스 신호와 관련된 용어

알아야 할 펄스 신호와 관련된 용어는 거의 없습니다. 이는 다음 그림의 도움으로 이해할 수 있습니다.

위 그림에서

Pulse width − 맥박의 길이

Period of a waveform − 한 사이클의 모든 지점에서 다음 사이클의 동일한 지점까지 측정

Duty cycle −주기에 대한 펄스 폭의 비율

Rise time − 최대 진폭의 10 %에서 90 %로 상승하는 데 걸리는 시간.

Fall time − 시간 신호는 최대 진폭의 90 %에서 10 %로 떨어집니다.

Overshoot − 파형의 선행 에지가 정상 최대 값을 초과 할 때 발생한다고합니다.

Undershoot − 파형의 트레일 링 에지가 정상 최대 값을 초과 할 때 발생한다고합니다.

Ringing − 언더 슈트와 오버 슈트 모두 링잉으로 알려진 감쇠 진동이 뒤 따릅니다.

감쇠 진동은 사용하지 않고 원하지 않는 신호의 진폭과 주파수가 감소하는 것을 나타내는 신호 변동입니다. 이러한 진동은 다음과 같은 단순한 장애입니다.ringing.

다음 장에서는 BJT를 사용하여 수행되는 전자 장치의 스위칭 개념을 설명합니다. 전자 회로 자습서에서 다이오드를 사용한 스위칭에 대해 이미 논의했습니다. 참조하시기 바랍니다.

스위치는 makes 또는 breaks회로 또는 접점. 또한 아날로그 데이터를 디지털 데이터로 변환 할 수 있습니다. 효율적인 스위치의 주요 요구 사항은 신속하고 스파크없이 전환하는 것입니다. 필수 부품은 스위치 및 관련 회로입니다.

세 가지가 있습니다 types of Switches. 그들은-

- 기계식 스위치

- 전자 기계 스위치 또는 릴레이

- 전자 스위치

기계식 스위치

기계식 스위치는 이전에 사용했던 구형 스위치입니다. 그러나 전자의 단점을 극복하기 위해 전자 기계식 스위치로 대체되었고 나중에는 일부 응용 분야에서도 전자 스위치로 대체되었습니다.

기계식 스위치의 단점은 다음과 같습니다.

- 그들은 작동 속도를 제한하는 높은 관성을 가지고 있습니다.

- 접촉을 끊는 동안 불꽃이 발생합니다.

- 스위치 접점은 더 큰 전류를 전달하기 위해 무겁게 만들어집니다.

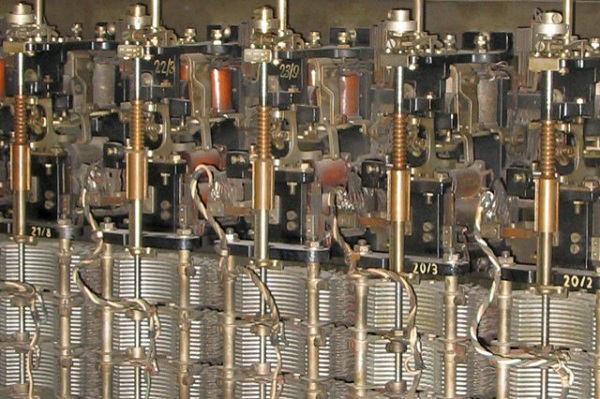

기계식 스위치는 아래 그림과 같습니다.

이러한 기계식 스위치는 작동 속도가 좋고 스파크를 줄이는 전기 기계식 스위치 또는 릴레이로 대체되었습니다.

릴레이

전기 기계 스위치는 Relays. 이 스위치는 부분적으로 기계적이고 부분적으로 전자 또는 전기적입니다. 이들은 전자 스위치보다 크기가 크고 기계식 스위치보다 크기가 작습니다.

릴레이 구성

접점을 만들어 부하에 전원을 공급하도록 릴레이가 만들어집니다. 외부 회로에는 부하 용 부하 전원 공급 장치와 릴레이 동작 제어용 코일 전원 공급 장치가 있습니다. 내부적으로 레버를 고정하기 위해 단단한 스프링이있는 철 요크에 레버가 연결되어 있습니다. 솔레노이드는 작동 코일이 감긴 요크에 연결됩니다. 이 코일은 언급 된 바와 같이 코일 전원 공급 장치와 연결됩니다.

아래 그림은 릴레이의 구성 및 작동을 설명합니다.

릴레이 작동

스위치가 닫히면 솔레노이드에 전원을 공급하는 전기 경로가 설정됩니다. 레버는 레버를 잡아 당기는 무거운 스프링으로 연결됩니다. 솔레노이드가 통전되면 스프링의 당기는 힘에 대항하여 레버를 그쪽으로 당깁니다. 레버를 당기면 움직이는 접점이 고정 접점과 만나 회로를 연결합니다. 따라서 회로 연결이 켜져 있거나 설정되어 있으며이를 나타내는 램프가 켜집니다.

스위치를 OFF로하면 솔레노이드는 전류가 흐르지 않고 전원이 차단됩니다. 이로 인해 레버가 솔레노이드쪽으로 끌리지 않게됩니다. 스프링이 레버를 위로 당겨 접촉을 끊습니다. 따라서 회로 연결이 꺼집니다.

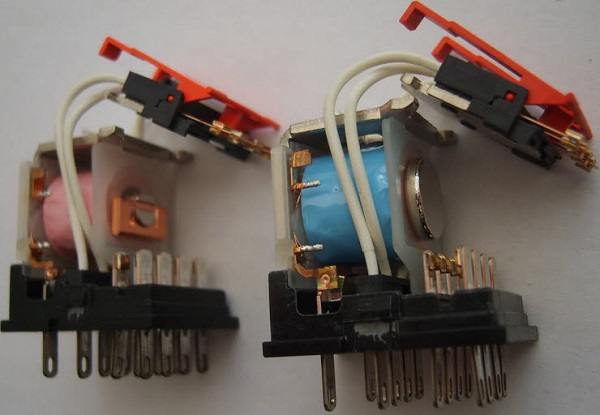

아래 그림은 실제 릴레이가 어떻게 생겼는지 보여줍니다.

이제 전자기 스위치의 장단점을 살펴 보겠습니다.

장점

- 릴레이는 부하에서 큰 전력을 처리하는 경우에도 적은 에너지를 소비합니다.

- 작업자는 고전압을 처리하기 위해 더 먼 거리에있을 수 있습니다.

- 켜거나 끄는 동안 스파크가 발생하지 않습니다.

단점

- 작동이 느림

- 부품이 마모되기 쉽습니다.

릴레이의 래치 유형

전자기 릴레이, 솔리드 스테이트 릴레이, 열 릴레이, 하이브리드 릴레이, 리드 릴레이 등과 같이 작동 모드에 따라 많은 종류의 릴레이가 있습니다.

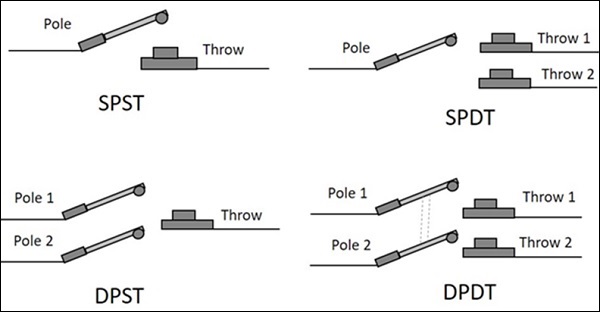

릴레이는 다음 그림과 같이 래치를 사용하여 연결합니다.

릴레이에는 4 가지 유형의 래치 연결이 있습니다. 그들은-

Single Pole Single Throw (SPST) −이 래치는 단일 폴을 가지고 있으며 연결을 위해 단일 스로우에 던져집니다.

Single Pole Double Throw (SPDT)−이 래치에는 연결을위한 단일 폴과 이중 스로우가 있습니다. 두 개의 스로우가 연결된 두 개의 다른 회로와 연결하도록 선택할 수 있습니다.

Double Pole Single Throw (DPST)−이 래치에는 연결을위한 이중 폴과 단일 스로우가 있습니다. 두 회로 중 하나를 선택하여 한 번에 사용할 수있는 회로와 연결할 수 있습니다.

Double Pole Double Throw (DPDT) −이 래치는 이중 극이 있으며 이중 던지기로 던져서 동시에 두 개의 연결을 만듭니다.

다음 그림은 네 가지 유형의 래치 연결을 모두 다이어그램으로 보여줍니다.

전자 스위치

논의 할 다음 종류의 스위치는 전자 스위치입니다. 앞서 언급했듯이 트랜지스터는 가장 많이 사용되는 전자 스위치입니다.high operating speed 과 absence of sparking.

다음 이미지는 트랜지스터가 스위치로 작동하도록 구축 된 실용적인 전자 회로를 보여줍니다.

트랜지스터는 포화 영역에서 작동 할 때 ON 상태에서 스위치로 작동합니다. 차단 영역에서 동작하면 OFF 상태에서 스위치로 동작합니다. 선형 영역에서 증폭기로 작동하며 트랜지스터 사이에 있고 차단됩니다. 이러한 작동 영역에 대한 아이디어를 얻으려면 BASIC ELECTRONICS 자습서의 트랜지스터 장을 참조하십시오.

외부 조건이 매우 견고하고 고온이 우세 할 때 단순하고 정상적인 트랜지스터는 그렇지 않습니다. 다음과 같은 특수 장치Silicon Control Rectifier, 간단히 SCR이러한 목적으로 사용됩니다. 이것은 POWER ELECTRONICS 튜토리얼에서 자세히 논의 될 것입니다.

전자 스위치의 장점

전자 스위치에는 다음과 같은 많은 장점이 있습니다.

- 더 작은 크기

- 가벼운 무게

- 반짝임 작업

- 움직이는 부품 없음

- 마모가 적음

- 소음이 적은 작동

- 더 빠른 작동

- 다른 스위치보다 저렴

- 적은 유지 보수

- 솔리드 스테이트로 인한 문제없는 서비스

ㅏ transistor작동 속도가 빠른 간단한 전자 스위치입니다. 고체 상태 장치이며 접점이 모두 간단하므로 작동 중에 스파크가 발생하지 않습니다. 다음 장에서 트랜지스터의 스위칭 동작 단계에 대해 설명합니다.

ㅏ transistor 중 하나를 구동하여 전자 스위치로 사용됩니다. saturation 또는 cut off. 이 둘 사이의 영역은 선형 영역입니다. 트랜지스터는이 영역에서 선형 증폭기로 작동합니다. 채도와 컷off 상태는 이와 관련하여 중요한 고려 사항입니다.

트랜지스터의 ON 및 OFF 상태

트랜지스터의 작동에는 두 가지 주요 영역이 있습니다. ON 과 OFF상태. 그들은 포화되고 잘립니다off상태. 이 두 가지 상태에서 트랜지스터의 동작을 살펴 보겠습니다.

차단 상태에서 작동

다음 그림은 차단 영역의 트랜지스터를 보여줍니다.

트랜지스터의베이스가 음으로 주어지면 트랜지스터는 차단 상태가됩니다. 콜렉터 전류가 없습니다. 따라서 I C = 0.

콜렉터에 적용된 전압 V CC 는 콜렉터 저항 R C 양단에 나타납니다 . 따라서,

V CE = V CC

포화 영역에서의 작업

다음 그림은 포화 영역의 트랜지스터를 보여줍니다.

베이스 전압이 양이고, 트랜지스터가 포화 상태가 될 때, I C는 R 흐른다 C .

그런 다음 V CC가 R C를 가로 질러 떨어집니다 . 출력은 0이됩니다.

$$I_C = I_{C(sat)} \: = \: \frac{V_{CC}}{R_C} \: and \: V_{CE} = 0$$

사실 이것은 이상적인 조건입니다. 실제로 약간의 누설 전류가 흐릅니다. 따라서 우리는 트랜지스터가 포화 상태로 구동 될 때 스위치 역할을하고베이스에 양 및 음 전압을 적용하여 영역을 차단한다는 것을 이해할 수 있습니다.

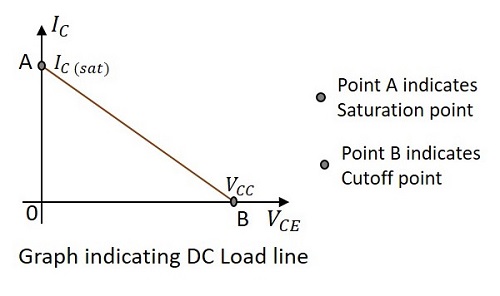

다음 그림은 더 나은 설명을 제공합니다.

I C 와 V CC 를 연결하는 dc 부하 라인을 관찰하십시오 . 트랜지스터가 포화 상태로 구동되면 I C 가 완전히 흐르고 V CE = 0으로 표시됩니다.A.

트랜지스터가 차단 상태로 구동되면 I C 는 0이되고 V CE = V CC 는 점 B로 표시됩니다. 포화 점 A와 차단 B를 연결하는 선은 다음과 같이 호출됩니다.Load line. 여기에 적용되는 전압이 dc이므로 다음과 같이 불립니다.DC Load line.

실용적인 고려 사항

위에서 언급 한 조건은 모두 설득력이 있지만 이러한 결과가 발생하는 데는 몇 가지 실질적인 제한이 있습니다.

차단 상태 중

이상적인 트랜지스터는 V CE = V CC 및 I C = 0입니다.

그러나 실제로는 더 작은 누설 전류가 컬렉터를 통해 흐릅니다.

따라서 I C 는 몇 μA가됩니다.

이것은 Collector Leakage Current 물론 무시해도됩니다.

포화 상태 동안

이상적인 트랜지스터는 V CE = 0 및 I C = I C (sat) 입니다.

그러나 실제로 V CE 는 다음과 같은 값으로 감소합니다.knee voltage.

V CE가 니 전압보다 더 많이 감소 하면 β는 급격히 감소합니다.

I C = βI B 이므로 콜렉터 전류가 감소합니다.

따라서 무릎 전압에서 V CE 를 유지 하는 최대 전류 I C 는 다음과 같이 알려져 있습니다.Saturation Collector Current.

포화 수집기 전류 = $I_{C(sat)} \: = \: \frac{V_{CC} - V_{knee}}{R_C}$

스위칭 목적으로 만 작동하도록 제작 된 트랜지스터를 Switching Transistor. 이것은 채도 또는 컷오프 영역에서 작동합니다. 포화 상태에있는 동안collector saturation current 부하를 통해 흐르고 차단 된 상태에서 collector leakage current 부하를 통해 흐릅니다.

트랜지스터의 스위칭 동작

트랜지스터에는 세 가지 작동 영역이 있습니다. 운영의 효율성을 이해하려면 실제 손실을 고려해야합니다. 이제 트랜지스터가 스위치로 얼마나 효율적으로 작동하는지에 대한 아이디어를 얻으려고합니다.

차단 (OFF) 상태 중

베이스 전류 I B = 0

콜렉터 전류 I C = I CEO (컬렉터 누수 전류)

전력 손실 = 출력 전압 × 출력 전류

$$= V_{CC} \times I_{CEO}$$

저의 CEO 가 매우 작고 V CC 도 낮기 때문에 손실은 매우 낮을 것입니다. 따라서 트랜지스터는 OFF 상태에서 효율적인 스위치로 작동합니다.

포화 (ON) 상태 중

앞서 논의했듯이

$$I_{C(sat)} = \frac{V_{CC} - V_{knee}}{R_C}$$

출력 전압은 Vknee.

전력 손실 = 출력 전압 × 출력 전류

$$= \:V_{knee} \times I_{c(sat)}$$

V의로 무릎 작은 값이 될 것입니다, 손실이 낮습니다. 따라서 트랜지스터는 ON 상태에서 효율적인 스위치로 작동합니다.

활성 지역 중

트랜지스터는 ON 및 OFF 상태 사이에 있습니다. 트랜지스터는 선형 증폭기로서 동작 여기서, 출력 전류 (ΔI의 입력 전류 원인 큰 변화의 작은 변화 C ).

전환 시간

스위칭 트랜지스터는 입력으로 펄스를 가지며 변동이 거의없는 펄스가 출력이됩니다. 스위칭 출력 펄스의 타이밍과 관련하여 알아야 할 몇 가지 용어가 있습니다. 그들을 살펴 보자.

입력 펄스 기간 = T

입력 펄스가 적용될 때 컬렉터 전류는 표유 커패시턴스로 인해 정상 상태 값에 도달하는 데 시간이 걸립니다. 다음 그림은이 개념을 설명합니다.

위 그림에서

Time delay(td) − 콜렉터 전류가 초기 값에서 최종 값의 10 %까지 도달하는 데 걸리는 시간을 Time Delay.

Rise time(tr) − 콜렉터 전류가 초기 값의 10 %에서 최종 값의 90 %까지 도달하는 데 걸리는 시간을 Rise Time.

Turn-on time (TON)− 시간 지연 (t d )과 상승 시간 (t r )의 합은 다음과 같습니다.Turn-on time.

T ON = t d + t r

Storage time (ts) − 입력 펄스의 트레일 링 에지에서 출력 최대 값의 90 %까지의 시간 간격을 Storage time.

Fall time (tf) − 콜렉터 전류가 최대 값의 90 %에서 초기 값의 10 %까지 도달하는 데 걸리는 시간을 Fall Time.

Turn-off time (TOFF)− 저장 시간 (t s )과 하강 시간 (t f )의 합은 다음과 같이 정의됩니다.Turn-off time.

T OFF = t S + t F

Pulse Width(W) − 상승 및 하강 파형의 두 50 % 레벨 사이에서 측정 된 출력 펄스의 지속 시간은 다음과 같이 정의됩니다. Pulse Width.

ㅏ multivibrator 회로는 단지 switching circuit. 사각 파, 사각 파, 톱니파 등과 같은 비 정현파를 생성합니다. 멀티 바이브레이터는 주파수 생성기, 주파수 분배기 및 시간 지연 생성기 및 컴퓨터 등의 메모리 요소로 사용됩니다.

트랜지스터는 기본적으로 선형 영역에서 증폭기로 작동합니다. 트랜지스터 증폭기 출력단이 이전 증폭기 단과 결합되면 이러한 연결이 결합된다고합니다. 이러한 증폭기 회로의 두 단계를 결합하는 데 저항이 사용되면 다음과 같이 불립니다.Resistance coupled amplifier. 자세한 내용은 AMPLIFIERS 자습서를 참조하십시오.

멀티 바이브레이터 란?

정의에 따르면 멀티 바이브레이터는 한 증폭기의 출력에서 다른 증폭기의 입력으로 포지티브 피드백이있는 2 단계 저항 결합 증폭기입니다 .

두 개의 트랜지스터가 피드백으로 연결되어 하나가 다른 하나의 상태를 제어합니다. 따라서 전체 회로의 ON 및 OFF 상태와 트랜지스터가 포화 상태로 구동되거나 차단되는 시간은 회로의 조건에 의해 제어됩니다.

다음 그림은 멀티 바이브레이터의 블록 다이어그램을 보여줍니다.

멀티 바이브레이터의 유형

멀티 바이브레이터에는 두 가지 가능한 상태가 있습니다. 첫 번째 단계에서, 트랜지스터 Q 1 동안 트랜지스터 Q를 온 2 권선 OFF. 두번째 단계에서, 트랜지스터 Q 1 트랜지스터 Q 동안 턴 OFF의 2 턴 ON. 이 두 상태는 회로 조건에 따라 특정 시간 동안 교환됩니다.

이 두 상태가 교환되는 방식에 따라 멀티 바이브레이터는 세 가지 유형으로 분류됩니다. 그들은

불안정한 멀티 바이브레이터

Astable Multivibrator는 다음과 같은 회로입니다. automatically switches작동을 위해 외부 펄스를 적용하지 않고 두 상태 사이에서 연속적으로. 이것은 연속적인 구형파 출력을 생성하기 때문에Free-running Multivibrator. DC 전원은 일반적인 요구 사항입니다.

이러한 상태의 기간은 사용 된 구성 요소의 시간 상수에 따라 달라집니다. 멀티 바이브레이터가 계속 전환 할 때 이러한 상태를 준 안정 또는 반 안정 상태라고합니다. 따라서two quasi-stable states 불안정한 멀티 바이브레이터를 위해.

단 안정 멀티 바이브레이터

단 안정 멀티 바이브레이터는 a stable state 과 a quasi-stable state. 이것은 하나의 트랜지스터에 대한 트리거 입력을 가지고 있습니다. 따라서 한 트랜지스터는 상태를 자동으로 변경하고 다른 트랜지스터는 상태를 변경하기 위해 트리거 입력이 필요합니다.

이 멀티 바이브레이터는 각 트리거 펄스에 대해 단일 출력을 생성하므로이를 One-shot Multivibrator. 이 멀티 바이브레이터는 트리거 펄스가 수신 될 때까지 안정 상태를 유지하는 동안 더 긴 기간 동안 준 안정 상태를 유지할 수 없습니다.

쌍 안정 멀티 바이브레이터

쌍 안정 멀티 바이브레이터는 two states stable. 상태를 변경하려면 두 개의 트리거 펄스를 적용해야합니다. 트리거 입력이 주어질 때까지이 멀티 바이브레이터는 상태를 변경할 수 없습니다. 그것은 또한 알려진flip-flop multivibrator.

트리거 펄스가 출력을 설정 또는 재설정하고 일부 데이터 (예 : 높음 또는 낮음)가 방해 될 때까지 저장 될 때이 멀티 바이브레이터는 Flip-flop. 플립 플롭에 대한 자세한 내용은 다음에서 DIGITAL CIRCUITS 튜토리얼을 참조하십시오.https://www.tutorialspoint.com/digital_circuits/index.htm

위의 논의에 대한 명확한 아이디어를 얻으려면 다음 그림을 살펴 보겠습니다.

이 세 가지 멀티 바이브레이터는 모두 다음 장에서 명확하게 설명됩니다.

불안정한 멀티 바이브레이터는 no stable states. 멀티 바이브레이터가 켜지면 R C 시간 상수에 의해 결정되는 특정 시간이 지나면 자체적으로 상태가 변경 됩니다. DC 전원 공급 장치 또는 V cc 가 작동을 위해 회로에 제공됩니다.

불안정한 멀티 바이브레이터 구축

Q 1 과 Q 2 라는 두 개의 트랜지스터 는 서로 피드백으로 연결됩니다. 트랜지스터 Q 1 의 컬렉터는 커패시터 C 1을 통해 트랜지스터 Q 2 의베이스에 연결 되며 그 반대의 경우도 마찬가지입니다. 두 트랜지스터의 이미 터는 접지에 연결됩니다. 콜렉터 부하 저항 R 1 및 R 4 및 바이어스 저항 R 2 및 R 3 은 동일한 값입니다. 커패시터 C 1 및 C 2 는 동일한 값입니다.

다음 그림은 Astable Multivibrator의 회로도를 보여줍니다.

불안정한 멀티 바이브레이터의 작동

V cc 가 적용되면 트랜지스터의 콜렉터 전류가 증가합니다. 콜렉터 전류는베이스 전류에 따라 달라 지므로

$$I_c = \beta I_B$$

비슷한 트랜지스터 특성이 없기 때문에 두 트랜지스터 중 하나는 Q 1 이 콜렉터 전류 증가를 가져서 전도 한다고 말합니다 . Q 1 컬렉터는 Q 2 에서 C 1 까지의베이스에 적용됩니다 . 이 연결을 통해 Q 1 의 컬렉터에서 증가 된 음의 전압 이 Q 2 의베이스에 적용되고 컬렉터 전류가 감소합니다. 이 지속적인 동작은 Q 2 의 콜렉터 전류를 더 감소시킵니다. 이 전류는 Q 1 의베이스에 적용될 때 더 음으로 만들고 누적 동작으로 Q 1 은 포화 상태가되고 Q 2 는 차단됩니다. 따라서 Q 1 의 출력 전압은 V CE (sat)가 되고 Q 2 는 V CC와 같습니다 .

커패시터 C 1 은 R 1을 통해 충전 되고 C 1 양단의 전압 이 0.7v에 도달하면 트랜지스터 Q 2 를 포화 상태 로 전환하기에 충분합니다 . 이 전압이 Q 2 의베이스에 적용 되면 포화 상태가되어 콜렉터 전류가 감소합니다. 포인트 B에서의 전압의 감소는 트랜지스터 Q의베이스에인가 한 C 내지 2 질문하게 1 역 바이어스. 이러한 일련의 동작은 트랜지스터 Q 1 을 차단하고 트랜지스터 Q 2 를 포화 상태로 만듭니다. 이제 지점 A에는 잠재적 인 V CC가 있습니다. 커패시터 C 2 는 R 2를 통해 충전됩니다 . 이 커패시터 C 2 양단의 전압이 0.7v에 도달하면 트랜지스터 Q 1 이 포화 상태가됩니다.

따라서, 출력 전압과 출력 파형은 트랜지스터 Q의 대안적인 스위칭에 의해 형성되는 1 과 Q 2 . 이러한 ON / OFF 상태의 기간은 사용 된 바이어스 저항 및 커패시터의 값, 즉 사용 된 R C 값 에 따라 달라집니다 . 두 트랜지스터가 교대로 작동하기 때문에 출력은 V CC 의 피크 진폭을 갖는 구형 파형 입니다.

파형

다음 그림은 Q 1 및 Q 2 콜렉터의 출력 파형을 보여줍니다.

진동의 빈도

트랜지스터 Q 1 의 ON 시간 또는 트랜지스터 Q 2 의 OFF 시간 은 다음과 같이 주어진다.

t 1 = 0.69R 1 C 1

유사하게, 트랜지스터 Q 1 의 OFF 시간 또는 트랜지스터 Q 2 의 ON 시간 은 다음과 같이 주어진다.

t 2 = 0.69R 2 C 2

따라서 구형파의 총 기간

t = t 1 + t 2 = 0.69 (R 1 C 1 + R 2 C 2 )

R 1 = R 2 = R 및 C 1 = C 2 = C이므로 구형파의 주파수는

$$f = \frac{1}{t} = \frac{1}{1.38 R C} = \frac{0.7}{RC}$$

장점

불안정한 멀티 바이브레이터 사용의 장점은 다음과 같습니다.

- 외부 트리거링이 필요하지 않습니다.

- 회로 설계는 간단합니다.

- Inexpensive

- 지속적으로 작동 가능

단점

불안정한 멀티 바이브레이터 사용의 단점은 다음과 같습니다.

- 에너지 흡수는 회로 내에서 더 많이 발생합니다.

- 출력 신호는 에너지가 낮습니다.

- 50 % 이하의 듀티 사이클은 달성 할 수 없습니다.

응용

Astable Multivibrators는 아마추어 무선 장비, 모스 부호 생성기, 타이머 회로, 아날로그 회로 및 TV 시스템과 같은 많은 응용 분야에서 사용됩니다.

이름에서 알 수 있듯이 단 안정 멀티 바이브레이터는 one stable state. 트랜지스터가 전도되면 다른 트랜지스터는 비전도 상태로 유지됩니다. 안정적인 상태는 외부 트리거 펄스에 의해 방해받지 않는 한 트랜지스터가 변경되지 않고 유지되는 상태입니다. Monostable은 동일한 원리로 작동하므로 다음과 같은 다른 이름이 있습니다.One-shot Multivibrator.

단 안정 멀티 바이브레이터의 구성

두 개의 트랜지스터 Q 1 및 Q 2 는 서로 피드백으로 연결됩니다. 트랜지스터 Q의 콜렉터 (1)는 , 트랜지스터 Q의베이스에 접속되어 2 캐패시터 C를 통해 1 . 베이스 Q 1 은 저항 R 2 와 커패시터 C를 통해 Q 2 의 콜렉터에 연결됩니다 . 또 다른 dc 공급 전압 –V BB 가 저항 R 3을 통해 트랜지스터 Q 1 의베이스에 제공됩니다 . 트리거 펄스는 Q의베이스에 부여되어 1 커패시터 C 내지 2 의 상태를 변경한다. R L1 및 R L2 는 Q 1 및 Q 2 의 부하 저항입니다 .

트랜지스터 중 하나는 안정적인 상태가되면 상태를 변경하기 위해 외부 트리거 펄스가 제공됩니다. 상태를 변경 한 후 트랜지스터는 RC 시정 수의 값에 의해 결정되고 이전 안정 상태로 돌아 오는 특정 기간 동안이 준 안정 상태 또는 메타 안정 상태를 유지합니다.

다음 그림은 단 안정 멀티 바이브레이터의 회로도를 보여줍니다.

단 안정 멀티 바이브레이터의 작동

회로가 ON 전환 될 때, 우선, 트랜지스터 Q 1은 OFF 상태에있을 것이고, Q (2)가 ON 상태에있을 것이다. 이것은 안정된 상태입니다. Q 1 이 OFF이면 콜렉터 전압은 A 지점에서 V CC 가되므로 C 1 이 충전됩니다. 포지티브 트리거 펄스는 트랜지스터 Q의베이스에인가 한 회전 트랜지스터 ON. 이것은 컬렉터 전압을 감소시켜 트랜지스터 Q 2를 끕니다 . 커패시터 (C) (1)는 이 시점에서 방전을 시작합니다. 트랜지스터 (Q)의 컬렉터에서 포지티브 전압이 2 트랜지스터 Q인가 도착 1 , 이는 ON 상태로 유지된다. 이것은 준 안정 상태 또는 준 안정 상태입니다.

트랜지스터 Q 2 개 커패시터 C까지 OFF 상태에 남아 1 개 방전 완전히. 그 후, 트랜지스터 Q 2 전압으로 켜지는 방전 커패시터를 통해인가. 이것은 이전 안정 상태 인 트랜지스터 Q 1을 켭니다 .

출력 파형

Q의 콜렉터에서의 출력 파형 1 과 Q 2 Q의베이스에 지정된 트리거 입력에 따라 1은 다음의 도면에 도시된다.

이 출력 펄스의 폭은 RC 시간 상수에 따라 다릅니다. 따라서 R 1 C 1 의 값에 따라 달라집니다 . 맥박의 지속 시간은 다음과 같습니다.

$$T = 0.69R_1 C_1$$

주어진 트리거 입력은 작업을 시작하기 위해 매우 짧은 기간입니다. 이것은 회로가 안정 상태에서 준 안정 또는 준 안정 또는 반 안정 상태로 상태를 변경하도록 트리거합니다.이 상태에서는 회로가 짧은 기간 동안 유지됩니다. 하나의 트리거 펄스에 대해 하나의 출력 펄스가 있습니다.

장점

단 안정 멀티 바이브레이터의 장점은 다음과 같습니다.

- 하나의 트리거 펄스로 충분합니다.

- 회로 설계는 간단합니다.

- Inexpensive

단점

단 안정 멀티 바이브레이터를 사용할 때의 가장 큰 단점은 트리거 펄스 T의 적용 사이의 시간이 회로의 RC 시정 수보다 커야한다는 것입니다.

응용

단 안정 멀티 바이브레이터는 텔레비전 회로 및 제어 시스템 회로와 같은 애플리케이션에 사용됩니다.

쌍 안정 멀티 바이브레이터는 two stable states. 회로는 두 가지 안정 상태 중 하나를 유지합니다. 외부 트리거 펄스가 제공되지 않는 한 해당 상태에서 계속됩니다. 이 멀티 바이브레이터는Flip-flop. 이 회로는 간단히Binary.

쌍 안정 멀티 바이브레이터에는 몇 가지 유형이 있습니다. 다음 그림과 같습니다.

쌍 안정 멀티 바이브레이터 구축

부하 저항 R L1 및 R L2 가있는 두 개의 유사한 트랜지스터 Q 1 및 Q 2 는 서로 피드백으로 연결됩니다. 기본 저항기 R 3 및 R 4 는 공통 소스 –V BB에 연결 됩니다. 피드백 저항 R 1 및 R 2 는 다음 과 같이 알려진 커패시터 C 1 및 C 2에 의해 분류 됩니다.Commutating Capacitors. 트랜지스터 Q 1 은 커패시터 C 3을 통해베이스에서 트리거 입력이 제공 되고 트랜지스터 Q 2 는 커패시터 C 4를 통해베이스에서 트리거 입력이 제공 됩니다.

커패시터 C 1 및 C 2 는 다음 과 같이 알려져 있습니다.Speed-up Capacitors, 그들이 감소함에 따라 transition time, 이는 한 트랜지스터에서 다른 트랜지스터로 전도를 전달하는 데 걸리는 시간을 의미합니다.

다음 그림은 자체 바이어스 쌍 안정 멀티 바이브레이터의 회로도를 보여줍니다.

쌍 안정 멀티 바이브레이터 작동

회로가 켜지면 Astable에서와 같이 일부 회로 불균형으로 인해 트랜지스터 중 하나, 즉 Q 1 이 켜지고 트랜지스터 Q 2 가 꺼집니다. 이것은 Bistable Multivibrator의 안정적인 상태입니다.

트랜지스터 Q의베이스에 부정적인 트리거를인가함으로써 1 또는 트랜지스터 Q의베이스에 양의 트리거 펄스를인가하여 2 이 안정 상태는 불변이다. 따라서 트랜지스터 Q 1 의베이스에서 음의 펄스를 고려하여 이것을 이해합시다 . 결과적으로 콜렉터 전압이 증가하여 트랜지스터 Q 2 를 순방향 바이어스합니다 . Q 1 의베이스에 적용된 Q 2 의 콜렉터 전류 , 역 바이어스 Q 1 및이 누적 동작은 트랜지스터 Q 1 OFF 및 트랜지스터 Q 2 ON을 만듭니다. 이것은 Multivibrator의 또 다른 안정적인 상태입니다.

이제이 안정 상태를 다시 변경해야하는 경우 트랜지스터 Q 2 의 음의 트리거 펄스 또는 트랜지스터 Q 1 의 양의 트리거 펄스 가 적용됩니다.

출력 파형

Q W 및 Q 2 의베이스에 제공된 트리거 입력과 함께 Q 1 및 Q 2 콜렉터의 출력 파형 이 다음 그림에 나와 있습니다.

장점

쌍 안정 멀티 바이브레이터 사용의 장점은 다음과 같습니다.

- 방해받지 않는 한 이전 출력을 저장합니다.

- 회로 설계는 간단합니다.

단점

쌍 안정 멀티 바이브레이터의 단점은 다음과 같습니다.

- 두 종류의 트리거 펄스가 필요합니다.

- 다른 멀티 바이브레이터보다 약간 비쌉니다.

응용

쌍 안정 멀티 바이브레이터는 펄스 생성 및 이진 정보의 계수 및 저장과 같은 디지털 작업과 같은 애플리케이션에 사용됩니다.

고정 바이어스 바이너리

고정 바이어스 바이너리 회로는 Astable Multivibrator와 유사하지만 간단한 SPDT 스위치가 있습니다. 두 개의 트랜지스터는 두 개의 저항으로 피드백으로 연결되며 하나의 컬렉터가 다른 하나의베이스에 연결됩니다. 아래 그림은 고정 바이어스 바이너리의 회로도를 보여줍니다.

작동을 이해하기 위해 스위치가 위치 1에 있다고 생각해 보겠습니다. 이제 베이스가 접지 되면 트랜지스터 Q 1 이 꺼집니다. 출력 단자 V O1 의 콜렉터 전압 은 트랜지스터 Q 2를 ON 으로하는 V CC 와 같습니다 . 단자 V O2 의 출력 은 LOW가됩니다. 이것은 외부 트리거에 의해서만 변경 될 수있는 안정된 상태입니다. 스위치를 위치 2로 변경하면 트리거로 작동합니다.

스위치가 변경되면 트랜지스터 Q 2 의베이스 가 접지되어 OFF 상태가됩니다. V O2 의 컬렉터 전압은 트랜지스터 Q 1 에 인가 된 V CC 와 동일합니다 . 이것은 다른 안정 상태입니다. 트리거링은 SPDT 스위치의 도움으로이 회로에서 이루어집니다.

이진 회로에 제공되는 두 가지 주요 유형의 트리거가 있습니다. 그들은

- 대칭 트리거링

- 비대칭 트리거링

슈미트 트리거

논의해야 할 또 다른 유형의 이진 회로는 Emitter Coupled Binary회로. 이 회로는Schmitt Trigger회로. 이 회로는 해당 응용 분야의 특수 유형으로 간주됩니다.

이 회로의 구성에서의 주요 차이점은, 출력 C의 결합이다 (2) 상기 제 1 트랜지스터의베이스 B1에 상기 제 2 트랜지스터의 누락 및 그 피드백 저항 R을 통해 현재 얻어지는 전자 . 이 회로는Regenerative circuit 이것 때문에 positive feedback 과 no Phase inversion. BJT를 이용한 Schmitt trigger의 회로는 다음과 같습니다.

처음에는 Q 1 OFF와 Q 2 ON이 있습니다. Q 2 의베이스에 적용되는 전압 은 R C1 및 R 1을 통해 V CC 입니다. 따라서 출력 전압은

$$V_0 = V_{CC} - (I_{C2}R_{c2})$$

Q 2 가 ON이면 R E 에서 전압 강하 가 발생하며 이는 (I C2 + I B2 ) RE 입니다. 이제이 전압은 Q 1 의 이미 터에 적용됩니다 . 입력 전압이 증가하고, Q까지 1 명 도달 컷 - 인을 ON 전압 출력은 LOW가 남아있다. Q로 1 Q로 ON, 출력은 증가한다 (2) 에 있습니다. 입력 전압이 계속 상승함에 따라 C 1 및 B 2 지점의 전압은 계속 떨어지고 E 2 는 계속 상승합니다. 입력 전압의 특정 값에서 Q 2 가 꺼집니다. 이 시점에서 출력 전압은 V CC가 되며 입력 전압이 더 증가하더라도 일정하게 유지됩니다.

입력 전압이 상승하면 입력 전압이 V 1 에 도달 할 때까지 출력이 LOW로 유지됩니다 .

$$V_1 = [V_{CC} - (I_{C2}R_{C2})]$$

입력 전압이 V 1 과 같고 트랜지스터 Q 1 이 포화 상태가되도록하는 값을 호출합니다.UTP(상위 트리거 포인트). 전압이 이미 V 1 보다 큰 경우 입력 전압이 V 2에 도달 할 때까지 남아 있습니다 . 이는 낮은 레벨 전환입니다. 따라서, 값이되는 입력 전압 V 것 2 Q되는 2가 ON 상태에 들어간로 불린다LTP (낮은 트리거 포인트).

출력 파형

출력 파형은 아래와 같이 얻습니다.

슈미트 트리거 회로는 Comparator 따라서 입력 전압을 다음과 같은 두 가지 전압 레벨과 비교합니다. UTP (상위 트리거 포인트) 및 LTP(낮은 트리거 포인트). 입력이이 UTP를 통과하면 HIGH로 간주되고이 LTP 아래로 떨어지면 LOW로 간주됩니다. 출력은 1은 HIGH, 0은 LOW를 나타내는 바이너리 신호입니다. 따라서 아날로그 신호는 디지털 신호로 변환됩니다. 입력이 중간 값 (HIGH와 LOW 사이)에 있으면 이전 값이 출력이됩니다.

이 개념은 다음과 같은 현상에 따라 달라집니다. Hysteresis. 전자 회로의 전달 특성은loop 호출 Hysteresis. 출력 값은 입력의 현재 값과 과거 값에 모두 의존한다는 것을 설명합니다. 이것은 슈미트 트리거 회로에서 원치 않는 주파수 스위칭을 방지합니다.

장점

슈미트 트리거 회로의 장점은 다음과 같습니다.

- 완벽한 로직 레벨이 유지됩니다.

- 메타 안정성을 피하는 데 도움이됩니다.

- 펄스 컨디셔닝을 위해 일반 비교기보다 선호됩니다.

단점

슈미트 트리거의 주요 단점은 다음과 같습니다.

- 입력이 느리면 출력이 느려집니다.

- 입력에 노이즈가 있으면 출력에 노이즈가 더 많이 발생합니다.

슈미트 트리거의 응용

슈미트 트리거 회로는 진폭 비교기 및 Squaring 회로로 사용됩니다. 또한 펄스 컨디셔닝 및 샤프닝 회로에도 사용됩니다.

이들은 트랜지스터를 사용하는 멀티 바이브레이터 회로입니다. 동일한 멀티 바이브레이터는 연산 증폭기와 IC 555 타이머 회로를 사용하여 설계되었으며 이는 추가 자습서에서 설명합니다.

펄스 회로의 기본을 논의한 후 이제 생성하고 처리하는 다양한 회로를 살펴 보겠습니다. Saw tooth waves. 톱니파는 시간이 지남에 따라 선형 적으로 증가하고 갑작스럽게 감소합니다. 이것은 또한Time base signal. 실제로 이것은 시간축 생성기의 이상적인 출력입니다.

시간축 생성기 란 무엇입니까?

생성하는 전자 발전기 high frequency saw tooth waves 로 불릴 수 있습니다 Time Base Generator. 또한 출력 전압 또는 전류 파형을 생성하는 전자 회로로 이해 될 수 있습니다.varies linearly with time. 시간축 생성기의 수평 속도는 일정해야합니다.

오실로스코프에서 시간에 따른 신호의 변화를 표시하려면 시간에 따라 선형 적으로 변화하는 전압을 편향 판에 적용해야합니다. 이렇게하면 화면에서 빔을 수평으로 스위프하는 신호가 생성됩니다. 따라서 전압은Sweep Voltage. 타임베이스 생성기는 다음과 같이 호출됩니다.Sweep Circuits.

타임베이스 신호의 특징

CRO 또는 픽처 튜브에서 타임베이스 파형을 생성하려면 편향 전압이 시간에 따라 선형 적으로 증가합니다. 일반적으로 빔이 화면에서 선형으로 편향되어 시작점으로 돌아가는 시간축 생성기가 사용됩니다. 이것은 과정에서 발생합니다Scanning. 음극선 관과 영상관도 같은 원리로 작동합니다. 빔은 화면에서 한쪽에서 다른쪽으로 (일반적으로 왼쪽에서 오른쪽으로) 편향되고 동일한 지점으로 돌아갑니다.

이 현상은 Trace 과 Retrace. 화면에서 왼쪽에서 오른쪽으로 빔의 편향을 다음과 같이 부릅니다.Trace, 빔의 오른쪽에서 왼쪽으로의 복귀는 Retrace 또는 Fly back. 일반적으로이 귀선은 보이지 않습니다. 이 프로세스는 사용 된 RC 구성 요소의 도움으로 편향 기간을 설정하는 톱니파 생성기의 도움으로 수행됩니다.

톱니파의 부분을 이해하려고 노력합시다.

위의 신호에서 출력이 선형 적으로 증가하는 시간을 다음과 같이 호출합니다. Sweep Time (TS) 신호가 초기 값으로 돌아가는 데 걸리는 시간은 다음과 같이 호출됩니다. Restoration Time 또는 Fly back Time 또는 Retrace Time (Tr). 이 두 기간은 함께 타임베이스 신호의 한 사이클의 기간을 형성합니다.

실제로 우리가 얻는이 스위프 전압 파형은 스위프 회로의 실제 출력 인 반면 이상적인 출력은 위 그림에 표시된 톱니 파형이어야합니다.

시간축 생성기의 유형

타임베이스 생성기에는 두 가지 유형이 있습니다. 그들은-

Voltage Time Base Generators − 시간에 따라 선형 적으로 변화하는 출력 전압 파형을 제공하는 타임베이스 생성기를 전압 타임베이스 생성기라고합니다.

Current Time Base Generator − 시간에 따라 선형 적으로 변화하는 출력 전류 파형을 제공하는 시간 기반 생성기를 현재 시간 기반 생성기라고합니다.

응용

Time Base Generator는 CRO, 텔레비전, RADAR 디스플레이, 정밀 시간 측정 시스템 및 시간 변조에 사용됩니다.

스위프 신호의 오류

스위프 신호를 생성 한 후 전송할 시간입니다. 전송 된 신호는 선형성에서 벗어날 수 있습니다. 발생한 오류를 이해하고 수정하려면 발생하는 일반적인 오류에 대한 지식이 있어야합니다.

선형성 편차는 세 가지 방식으로 표현됩니다. 그들은-

- 슬로프 또는 스위프 속도 오류

- 변위 오류

- 전송 오류

이에 대해 자세히 논의하겠습니다.

슬로프 또는 스위프 속도 오류 (e s )

스위프 전압은 시간에 따라 선형 적으로 증가해야합니다. 시간에 따른 스위프 전압의 변화율은 일정해야합니다. 이 선형성 편차는 다음과 같이 정의됩니다.Slope Speed Error 또는 Sweep Speed Error.

경사 또는 스위프 속도 eror 전자 S =$\frac{difference \: in\: slope\: at \: the\: beginning\: and\: end\: of\: sweep}{initial \: value \:of \: slope}$

$$= \frac{\left (\frac{\mathrm{d} V_0}{\mathrm{d} t} \right )_{t = 0} - \left( \frac{\mathrm{d} V_0}{\mathrm{d} t} \right)_{t = T_s}}{\left( \frac{\mathrm{d} V_0}{\mathrm{d} t}\right )_{t = 0}}$$

변위 오류 (e d )

선형성의 중요한 기준은 실제 스위프 전압과 실제 스위프의 시작점과 끝점을 통과하는 선형 스위프 간의 최대 차이입니다.

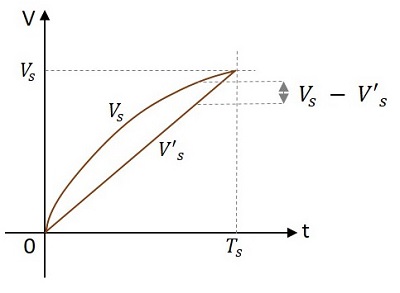

이것은 다음 그림에서 이해할 수 있습니다.

변위 오류 ed 다음과 같이 정의됩니다.

e d =$\frac{(actual\: speed)\thicksim (linear\: sweep \: that\: passes\: beginning \: and \: ending\: of\: actual\: sweep)}{amplitude\: of\: sweep\: at\: the \: end\: of\: sweep\: time}$

$$= \: \frac{(V_s - V′_s)_{max}}{V_s}$$

어디 V s는 실제 스윕과 V ' 의이 선형 스윕이다.

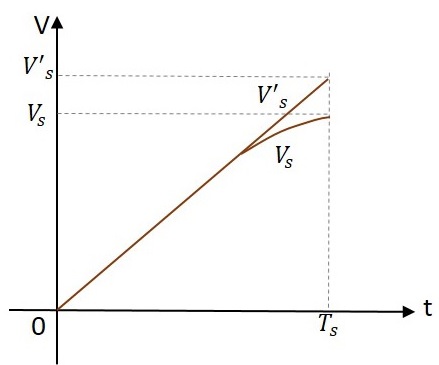

전송 오류 (e t )

스위프 신호가 하이 패스 회로를 통과하면 출력은 아래와 같이 입력에서 벗어납니다.

이 편차는 전송 오류로 표현됩니다.

전송 오류 = $\frac{(input)\: \thicksim \:(output)}{input\: at \: the\: end\: of\: the\: sweep}$

$$e_t = \frac{V′_s − V}{V′_s}$$

여기서 V ' S는 입력이고, V S는 t = T에서 스윕 즉 끝의 출력 들 .

선형성 편차가 매우 작고 스윕 전압이 t의 선형 및 2 차 항의 합으로 근사 될 수있는 경우 위의 세 오류는 다음과 관련됩니다.

$$e_d = \frac{e_s}{8} = \frac{e_t}{4}$$

$$e_s = 2e_t = 8e_d$$

스위프 속도 오류는 변위 오류보다 더 지배적입니다.

두 가지 유형의 타임베이스 생성기가 있다는 생각이 있으므로 해당 타임베이스 생성기 회로의 기본 회로에 대해 알아 보겠습니다.

전압 타임베이스 생성기

시간에 따라 선형 적으로 변하는 출력 전압 파형을 제공하는 타임베이스 생성기를 전압 타임베이스 생성기라고합니다.

기본 전압 타임베이스 생성기를 이해해 보겠습니다.

간단한 전압 타임베이스 생성기

기본 단순 RC 시간축 생성기 또는 램프 생성기 또는 스위프 회로는 직렬 연결된 저항 R 2 를 통해 V CC 를 통해 충전되는 커패시터 C로 구성됩니다 . 베이스가 저항 R 1을 통해 연결된 BJT를 포함합니다 . 커패시터는 저항을 통해 충전되고 트랜지스터를 통해 방전됩니다.

다음 그림은 간단한 RC 스윕 회로를 보여줍니다.

포지티브가는 전압 펄스의인가에 의해, 채도 및 캐패시터에 ON, 트랜지스터 Q의 회전이 급격히 Q 및 R을 통해 배출 1 V 행 CE (포화) . 입력 펄스가 종료되면 Q가 꺼지고 커패시터 C가 충전을 시작하고 다음 입력 펄스까지 계속 충전됩니다. 이 과정은 아래 파형과 같이 반복됩니다.

트랜지스터가 켜지면 커패시터가 빠르게 방전 될 수 있도록 낮은 저항 경로를 제공합니다. 트랜지스터가 OFF 상태에있을 때 커패시터는 방정식에 따라 공급 전압 V CC 까지 지수 적으로 충전됩니다.

$$V_0 = V_{CC}[1 - exp(-t/RC)]$$

어디

- V O = 시간 t에서 커패시터 양단의 순간 전압

- V CC = 공급 전압

- t = 소요 시간

- R = 직렬 저항 값

- C = 커패시터 값

이제 다양한 유형의 시간축 생성기에 대해 알아 보겠습니다.

방금 논의한 회로는 전압의 형태로 출력을 제공하는 전압 타임베이스 생성기 회로입니다.

현재 시간 기반 생성기

시간에 따라 선형 적으로 변하는 출력 전류 파형을 제공하는 시간 기반 생성기를 현재 시간 기반 생성기라고합니다.

기본적인 현재 시간축 생성기를 이해해 보겠습니다.

간단한 현재 시간 기반 생성기

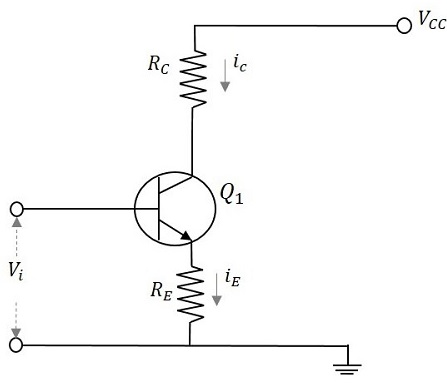

기본 단순 RC 타임베이스 생성기 또는 램프 생성기 또는 스위프 회로는 공통베이스 구성 트랜지스터와 두 개의 저항으로 구성되며 하나는 이미 터에 있고 다른 하나는 콜렉터에 있습니다. V CC 는 트랜지스터의 컬렉터에 제공됩니다. 기본 램프 전류 생성기의 회로도는 아래에 나와 있습니다.

공통베이스 구성으로 연결된 트랜지스터는 콜렉터 전류가 이미 터 전류에 따라 선형 적으로 변합니다. 이미 터 전류가 일정하게 유지되면 콜렉터 기본 전압의 매우 작은 값을 제외하고 콜렉터 전류도 거의 일정한 값이됩니다.

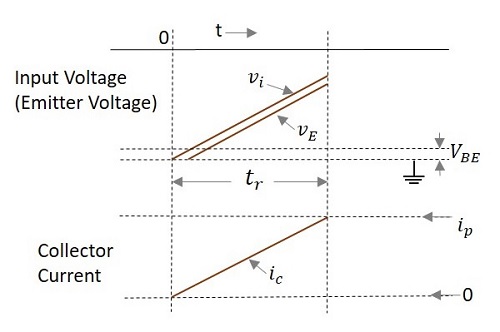

입력 전압 V i 가 트랜지스터의베이스에 적용됨에 따라 에미 터 전류 i E 를 생성하는 에미 터에 나타나며 V i 가 0에서 피크 값 으로 증가함에 따라 선형 적으로 증가합니다. 컬렉터 전류는 이미 터 전류가 증가함에 따라 증가합니다. 왜냐하면 i C 가 i E 와 거의 같기 때문 입니다.

부하 전류의 순간 값은

$$i_L i_C \thickapprox (v_i - V_{BE})/R_E$$

입력 및 출력 파형은 다음과 같습니다.

부트 스트랩 스위프 생성기는 출력이 피드백을 통해 입력으로 피드백되는 시간축 생성기 회로입니다. 이것은 회로의 입력 임피던스를 높이거나 낮출 것입니다. 이 과정bootstrapping 일정한 충전 전류를 얻기 위해 사용됩니다.

부트 스트랩 시간축 생성기의 구성

부트 스트랩 시간 기반 발생기 회로는 두 개의 트랜지스터 Q 구성 1 스위치와 Q 역할 2 이미 터 폴로 워로서 작용한다. 트랜지스터 Q 1 은 베이스 의 입력 커패시터 C B 와 저항 R B ~ V CC를 사용하여 연결됩니다 . 트랜지스터 Q의 콜렉터 (1)는 , 트랜지스터 Q의베이스에 접속되어 2 . Q 2 의 콜렉터는 V CC에 연결되고 이미 터 에는 출력이 사용되는 저항 R E 가 제공됩니다 .

다이오드 D는 양극이 V CC 에 연결되고 음극은 출력에 연결된 커패시터 C 2 에 연결됩니다. 다이오드 D의 캐소드는 커패시터 C에 차례로 연결되는 저항 R에 연결되어 1 . 이 C 1 과 R은 Q 2 의베이스 와 Q 1의 컬렉터를 통해 연결됩니다 . 커패시터 C 1 양단에 나타나는 전압 은 출력 전압 V o를 제공합니다 .

다음 그림은 부트 스트랩 타임베이스 생성기의 구성을 설명합니다.

부트 스트랩 시간축 생성기 작동

t = 0에서 게이팅 파형을 적용하기 전에 트랜지스터가 V CC 에서 R B를 통해 충분한 기본 드라이브를 얻으므로 Q 1 은 ON이고 Q 2 는 OFF입니다. 캐패시터 C 2 개 V까지 충전 CC 이어서 다이오드 D. 단 안정 멀티 바이브레이터 (monostable multivibrator)의 게이팅 파형으로부터 음극 트리거 펄스까지는 Q의베이스에인가 한 Q 온 1 OFF한다. 커패시터 (C) (2)가 지금과 방전 용량 C 1 커패시터 C로 저항 R. 통해 전하 2 커패시턴스의 큰 값을 가지고, 그 전압 레벨 (충전 및 방전)는 느린 속도로 변화한다. 따라서 그것은 천천히 방전되고 Q 2 의 출력에서 램프 생성 동안 거의 일정한 값을 유지합니다 .

램프 시간 동안 다이오드 D는 역 바이어스됩니다. 커패시터 C 2 는 커패시터 C 1 이 충전 할 수 있도록 작은 전류 I C1 을 제공합니다 . 커패시턴스 값이 높기 때문에 전류를 제공하지만 전하에 큰 차이는 없습니다. 램프 시간이 끝날 때 Q 1 이 ON되면 C 1 은 초기 값으로 빠르게 방전됩니다. 이 전압은 V 가로로 표시 O . 따라서, 다이오드 D는 다시 순방향 바이어스 얻고 커패시터 C 2 는 C의 충전 중에 손실 작은 전하 회복 전류의 펄스를 얻을 1 . 이제 회로는 또 다른 램프 출력을 생성 할 준비가되었습니다.

커패시터 C2 커패시터 C1에 피드백 전류를 제공하는 데 도움이됩니다. boot strapping capacitor 정전류를 제공합니다.

출력 파형

출력 파형은 다음 그림과 같이 얻습니다.

입력에 주어진 펄스 와 출력에 기여하는 커패시터 C 1 의 충전 및 방전을 나타내는 전압 V C1 이 위의 그림에 나와 있습니다.

이점

이 부트 스트랩 램프 생성기의 주요 이점은 출력 전압 램프가 매우 선형적이고 램프 진폭이 공급 전압 레벨에 도달한다는 것입니다.

트랜지스터 밀러 타임베이스 생성기 회로가 인기가 있습니다. Miller integrator스위프 파형을 생성하는 회로. 이것은 주로 수평 편향 회로에 사용됩니다.

Miller 시간축 생성기 회로의 구성과 작동을 이해해 보겠습니다.

Miller Sweep Generator의 건설

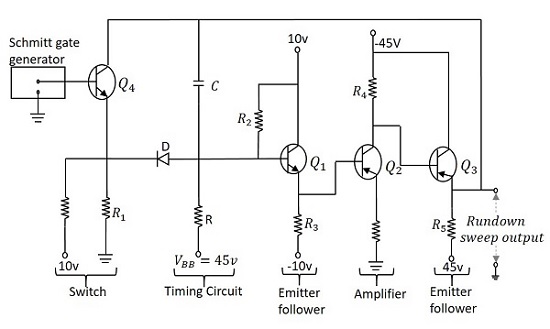

Miller 시간축 생성기 회로는 초기 단계의 스위치와 타이밍 회로로 구성되며, 입력은 Schmitt 게이트 생성기 회로에서 가져옵니다. 앰프 섹션은 3 단계로 구성된 다음 섹션입니다.emitter follower, 두 번째 amplifier 그리고 세 번째는 또한 emitter follower.

이미 터 팔로워 회로는 일반적으로 Buffer amplifier. 그것은low output impedance 그리고 high input impedance. 낮은 출력 임피던스로 인해 회로가 무거운 부하를 구동 할 수 있습니다. 높은 입력 임피던스는 회로가 이전 회로를로드하지 않도록합니다. 마지막 이미 터 팔로워 섹션은 이전 앰프 섹션을로드하지 않습니다. 이 때문에 앰프 게인이 높아집니다.

Q 1 의베이스와 Q 3 의 이미 터 사이에 위치한 커패시터 C 가 타이밍 커패시터입니다. R과 C의 값과 V BB 의 전압 레벨의 변화는 스위프 속도를 변경합니다. 아래 그림은 Miller 시간축 생성기의 회로를 보여줍니다.

Miller Sweep Generator의 작동

슈미트 트리거 발생기의 출력이 음의 펄스는 트랜지스터 Q 인 경우 (4) 를 온 및 이미 터 전류가 흐른다 R 1 . 이미 터는 음의 전위에 있으며 다이오드 D의 음극에도 동일하게 적용되어 순방향 바이어스됩니다. 여기서 커패시터 C는 바이 패스되므로 충전되지 않습니다.

트리거 펄스를 적용하면 슈미트 게이트 출력이 높아지고 트랜지스터 Q 4가 꺼집니다. 이제 10v의 전압이 Q 4 의 이미 터에 적용되어 R 1 을 통해 전류가 흐르게 하여 다이오드 D도 역 바이어스됩니다. 트랜지스터 Q 4 가 차단되면 커패시터 C는 V BB 에서 R을 통해 충전되고 Q 3 에미 터에서 런 다운 스윕 출력을 제공합니다 . 커패시터 C 는 스위프가 끝날 때 D와 트랜지스터 Q 4 를 통해 방전됩니다 .

커패시턴스 C 1 의 효과를 고려하면 기울기 속도 또는 스위프 속도 오류는

$$e_s = \frac{V_s}{V} \left( 1- A + \frac{R}{R_i} + \frac{C}{C_i} \right )$$

응용

밀러 스위프 회로는 많은 장치에서 가장 일반적으로 사용되는 적분기 회로입니다. 널리 사용되는 톱니 발생기입니다.

Unijunction Transistor는 단일 PN 접합이 있지만 여전히 다이오드가 아닌 트랜지스터입니다. Unijunction 트랜지스터 또는 간단히UJT일반 트랜지스터와 달리 이미 터와 두 개의베이스가 있습니다. 이 부품은 특히 네거티브 저항 특성과 이완 발진기로서의 응용으로 유명합니다.

UJT 구축

저항성이 높은 n 형 실리콘 막대가 기본 구조를 형성하는 것으로 간주됩니다. 두 개의 저항 접점이 양쪽 끝에 그려져 있습니다. 이미 터가되는 알루미늄 막대와 같은 구조가 부착되어 있습니다. 이 이미 터는베이스 2에 가깝고베이스 1에 조금 멀습니다. 이 두 가지 모두 결합하여 PN 접합을 형성합니다. 단일 PN 접합이 존재하므로이 구성 요소를Unijunction transistor.

라는 내부 저항 intrinsic resistance저항 값이 막대의 도핑 농도에 따라 달라지는 막대 내부에 존재합니다. UJT의 구성 및 기호는 다음과 같습니다.

기호에서 이미 터는 기울어 진 화살표로 표시되고 나머지 두 끝은베이스를 나타냅니다. UJT는 다이오드와 일부 저항의 조합으로 이해되므로 UJT의 내부 구조는 UJT의 작동을 설명하는 등가 다이어그램으로 표시 할 수 있습니다.

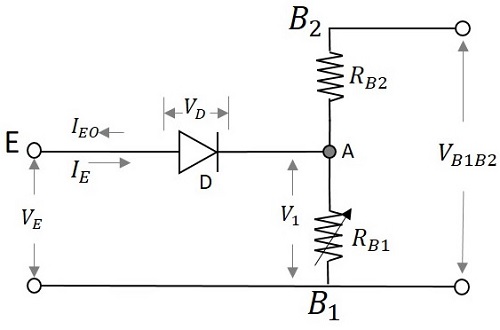

UJT의 일

UJT의 작동은 등가 회로로 이해할 수 있습니다. 이미 터에 적용된 전압은 V E 로 표시되고 내부 저항은 베이스 1과 2에서 각각 R B1 및 R B2 로 표시됩니다 . 내부에 존재하는 두 저항은 함께 다음과 같이 불립니다.intrinsic resistance, R BB 로 표시됩니다 . RB1 양단의 전압은 V 1 로 표시 할 수 있습니다 . 회로가 작동하는 데 적용되는 DC 전압은 V BB 입니다.

UJT 등가 회로는 다음과 같습니다.

처음에는 전압이인가되지 않았을 때

$$V_E = 0$$

그런 다음 전압 V BB 가 R B2를 통해 적용됩니다 . 다이오드 D는 역방향 바이어스가됩니다. 다이오드 양단의 전압은 이미 터 다이오드의 장벽 전압 인 VB가됩니다. V BB 의 적용으로 인해 A 지점에 일부 전압이 나타납니다. 따라서 총 전압은 V A + V B 입니다.

이제 이미 터 전압 V E 가 증가하면 전류 I E 가 다이오드 D를 통해 흐릅니다.이 전류는 다이오드를 순방향 바이어스하게 만듭니다. 캐리어가 유도되고 저항 R B1 이 계속 감소합니다. 따라서 V B1 을 의미하는 R B1 의 전위 도 감소합니다.

$$V_{B1} = \left( \frac{R_{B1}}{R_{B1} + R_{B2}} \right )V_{BB}$$

V BB 가 일정하고 R B1 이 채널의 도핑 농도로 인해 최소값으로 감소함에 따라 V B1 도 감소합니다.

실제로 내부에 존재하는 저항은 다음과 같이 함께 호출됩니다. intrinsic resistance, R BB 로 표시됩니다 . 위에서 언급 한 저항은 다음과 같이 나타낼 수 있습니다.

$$R_{BB} = R_{B1} + R_{B2}$$

$$\left( \frac{R_{B1}}{R_{BB}} \right ) = \eta$$

기호 η는 적용된 총 저항을 나타내는 데 사용됩니다.

따라서 V B1 양단의 전압 은 다음과 같이 표현됩니다.

$$V_{B1} = \eta V_{BB}$$

이미 터 전압은 다음과 같이 제공됩니다.

$$V_E = V_D + V_{B1}$$

$$V_E = 0.7 + V_{B1}$$

여기서 V D 는 다이오드 양단의 전압입니다.

다이오드가 순방향 바이어스되면 전압은 0.7v가됩니다. 따라서 이것은 일정하고 V B1 은 계속 감소합니다. 따라서 V E 는 계속 감소합니다. 이 V로 표시 될 수있는 최소 값으로 감소 V를 이라Valley voltage. UJT가 켜지는 전압은Peak VoltageV P 로 표시됩니다 .

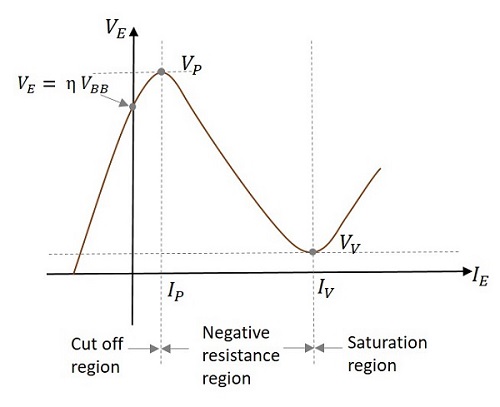

VI UJT의 특성

지금까지 논의 된 개념은 아래의 그래프에서 명확하게 이해됩니다.

V 초기 때 E는 제로까지 IE가 흘러 일부 역방향 전류의 값에 도달에게에서 포인트를 VE

$$V_E = \eta V_{BB}$$

이것은 곡선이 Y 축에 닿는 지점입니다.

V E 가 전압에 도달하면

$$V_E = \eta V_{BB} + V_D$$

이 시점에서 다이오드는 순방향 바이어스됩니다.

이 시점의 전압을 V P (Peak Voltage) 그리고이 시점의 전류는 I P (Peak Current). 지금까지의 그래프 부분은Cut off region UJT가 OFF 상태 였기 때문입니다.

이제 V E 가 더 증가하면 저항 R B1 과 전압 V 1 도 감소하지만 전류는 증가합니다. 이것이Negative resistance property 따라서이 지역은 Negative resistance region.

이제 전압 V E 는 추가 증가가 R B1 양단의 전압 증가로 이어지는 특정 지점에 도달합니다 . 이 시점의 전압을 V V (Valley Voltage) 그리고이 시점의 전류는 I V (Valley Current). 이 후 지역은Saturation region.

UJT의 응용

UJT는 이완 발진기로 가장 두드러지게 사용됩니다. 위상 제어 회로에도 사용됩니다. 또한 UJT는 디지털 회로 용 클록, 다양한 장치의 타이밍 제어, 사이리스터에서 제어 된 발사 및 CRO의 수평 편향 회로 용 동기 펄스를 제공하는 데 널리 사용됩니다.

안 oscillator입력없이 자체적으로 파형을 생성하는 장치입니다. 장치가 작동하기 위해 약간의 DC 전압이 적용되지만 입력으로 파형을 생성하지 않습니다. 이완 발진기는non-sinusoidal waveform그 자체로. 이 파형은 일반적으로 회로에서 커패시터의 충전 및 방전 시간 상수에 따라 달라집니다.

건설 및 작업

UJT의 이미 터는 그림과 같이 저항과 커패시터로 연결됩니다. RC 시정 수는 이완 발진기의 출력 파형 타이밍을 결정합니다. 두베이스는 각각 저항으로 연결됩니다. DC 전압 공급 V BB 가 제공됩니다.

다음 그림은 UJT를 이완 오실레이터로 사용하는 방법을 보여줍니다.

처음에는 커패시터 양단의 전압이 0입니다.

$$V_c = 0$$

UJT가 OFF 상태입니다. 저항기R 커패시터 경로 제공 C 적용된 전압을 통해 충전합니다.

커패시터는 전압에 따라 충전됩니다.

$$V = V_0(1 - e^{-t/RC})$$

커패시터는 일반적으로 충전을 시작하고 최대 전압 V BB 까지 충전을 계속합니다 . 그러나이 회로에서 커패시터 양단의 전압이 UJT가 켜질 수있는 값 (피크 전압)에 도달하면 커패시터가 충전을 중지하고 UJT를 통해 방전을 시작합니다. 이제이 방전은 UJT를 끄는 최소 전압 (밸리 전압)까지 계속됩니다. 이 프로세스가 계속되고 커패시터 양단의 전압이 그래프에 표시되면 다음 파형이 관찰됩니다.

따라서 커패시터의 충전 및 방전은 위와 같이 스위프 파형을 생성합니다. 충전 시간은 스윕을 증가시키고 방전 시간은 스윕을 감소시킵니다. 이 사이클의 반복은 연속 스위프 출력 파형을 형성합니다.

출력이 정현파가 아닌 파형이기 때문에이 회로는 이완 발진기 역할을한다고합니다.

이완 발진기의 응용

이완 발진기는 함수 발생기, 전자 신호음, SMPS, 인버터, 깜빡이 및 전압 제어 발진기에 널리 사용됩니다.

파형 발생기가 서로 다른 모든 시스템에서 모두 동기식으로 작동해야합니다. 동기화는 두 개 이상의 파형 발생기가주기의 일부 기준점에 정확히 동시에 도착하도록 만드는 프로세스입니다.

동기화 유형

동기화는 다음 두 가지 유형이 될 수 있습니다.

일대일 기준

모든 발전기는 동일한 주파수로 작동합니다.

그들 모두는주기의 어떤 기준점에 정확히 동시에 도착합니다.

주파수 분할과 동기화

발전기는 서로 정수배 인 서로 다른 주파수에서 작동합니다.

그들 모두는주기의 어떤 기준점에 정확히 동시에 도착합니다.

이완 장치

완화 회로는 커패시터의 점진적인 충전을 통해 타이밍 간격이 설정되는 회로로, 타이밍 간격은 커패시터의 갑작스런 방전 (완화)에 의해 종료됩니다.

Examples − 멀티 바이브레이터, 스위프 회로, 차단 발진기 등

우리는 UJT 완화 발진기 회로에서 UJT와 같은 음극 저항 장치가 켜지면 커패시터가 충전을 중지하는 것을 관찰했습니다. 그런 다음 커패시터는이를 통해 방전되어 최소값에 도달합니다. 이 두 지점은 모두 스위프 파형의 최대 및 최소 전압 지점을 나타냅니다.

이완 장치의 동기화

스위프 파형의 고전압 또는 피크 전압 또는 항복 전압을 더 낮은 레벨로 낮추어야하는 경우 외부 신호를 적용 할 수 있습니다. 적용되는이 신호는 그 효과가 펄스 기간 동안 피크 또는 항복 전압의 전압을 낮추는 동기화 된 신호입니다. 동기화 펄스는 일반적으로 이미 터 또는 네거티브 저항 장치의베이스에 적용됩니다. 동기화를 달성하기 위해 일정한 간격의 펄스를 갖는 펄스 트레인이 적용됩니다.

동기화 신호가 적용 되더라도 펄스 발생시 스위프 신호의 진폭이 VP 보다 작을뿐 아니라 처음 몇 개의 펄스가 스위프 생성기에 영향을 미치지 않습니다 . 따라서 스윕 생성기는 동기화되지 않은 상태로 실행됩니다. UJT가 켜지는 정확한 순간은 펄스 발생 순간에 의해 결정됩니다. 동기화 신호가 스위프 신호와 동기화되는 지점입니다. 이것은 다음 그림에서 볼 수 있습니다.

어디,

- T P 는 펄스 신호의 기간입니다.

- T O는 스위프 신호의 시간

- V P 는 피크 또는 항복 전압입니다.

- V V 는 밸리 또는 유지 전압

동기화를 달성하기 위해 펄스 타이밍 간격 TP 스윕 생성기의 기간보다 짧아야합니다. TO, 스윕주기를 조기에 종료합니다. 펄스 타이밍 간격이TP스윕 발생기 T O 의 시간보다 길고 또한 펄스의 진폭이 정지 항복과 스윕 전압 사이의 간격을 메우기에 충분히 크지 않은 경우에도 T P 는TO.

스위프 회로의 주파수 분할

이전 항목에서는 다음 조건이 충족 될 때 동기화가 이루어짐을 확인했습니다. 그들은

T P <T O 일 때

펄스의 진폭이 각 사이클을 조기에 종료하기에 충분할 때.

이 두 가지 조건을 충족하면 동기화가 이루어 지지만 동기화 타이밍과 관련하여 스위프에서 특정 흥미로운 패턴을 발견 할 수 있습니다. 다음 그림은이 점을 보여줍니다.

동기화 후 스위프 의 진폭 V ' S 가 동기화되지 않은 진폭 V S 보다 작다는 것을 알 수 있습니다. 또한 스위프의 기간 T O 는 펄스의 기간에 따라 조정되지만 그 사이에 사이클이 남습니다. 즉, 하나의 스위프 사이클이 두 개의 펄스 사이클과 동일하게됩니다. 모든 대체주기에 대해 동기화가 이루어집니다.

$$T_o > 2T_P$$

스위프 타이밍 T O 는 TS 로 제한되고 진폭은 V ' S로 감소합니다 .

매 두 번째 펄스가 스위프주기와 동기화되어 만들어 지므로이 신호는 2 배의 주파수 분할을 나타내는 회로로 이해 될 수 있습니다. 따라서 주파수 분할 회로는 동기화에 의해 얻어집니다.

발진기는 제공하는 회로입니다 alternating voltage 또는 current by its own, 입력이 적용되지 않습니다. 발진기에는amplifier 그리고 또한 feedback출력에서. 제공되는 피드백은 출력 신호의 일부와 함께 입력 신호와 위상이 같은 출력 신호의 구성 요소를 포함하는 재생 피드백이어야합니다. 비 정현파 출력을 생성하기 위해 재생 피드백을 사용하는 발진기는 다음과 같이 호출됩니다.Relaxation Oscillator.

우리는 이미 UJT 이완 발진기를 보았습니다. 이완 발진기의 또 다른 유형은 차단 발진기입니다.

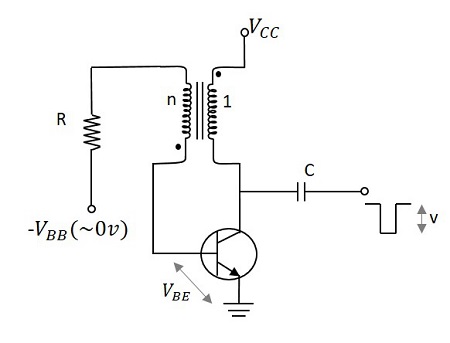

차단 발진기

차단 발진기는 좁은 펄스 또는 트리거 펄스를 생성하는 데 사용되는 파형 발생기입니다. 출력 신호에서 피드백을받는 동안주기가 지정된 특정 시간 동안 피드백을 차단합니다. 이 기능blocking the output 있는 동안 an oscillator, 오실레이터를 차단하는 이름을 가져옵니다.

차단 발진기의 구성에서 트랜지스터는 증폭기로 사용되며 변압기는 피드백에 사용됩니다. 여기에 사용 된 변압기는Pulse transformer. 펄스 변압기의 기호는 다음과 같습니다.

펄스 변압기

펄스 변압기는 전기 에너지의 직사각형 펄스 소스를 부하에 연결하는 변압기입니다. 펄스의 모양과 기타 속성을 그대로 유지합니다. 그들은 광대역 변압기입니다minimum attenuation 및 0 또는 최소 phase change.

변압기의 출력은 연결된 커패시터의 충전 및 방전에 따라 달라집니다.

펄스 트랜스포머를 사용하여 회생 피드백을 쉽게 할 수 있습니다. 출력은 펄스 트랜스포머의 권선 극성을 적절하게 선택하여 동일한 위상의 입력으로 피드백 될 수 있습니다. 차단 발진기는주기적인 펄스를 생성하는 대부분의 듀티 사이클 동안 차단되는 단일 트랜지스터와 함께 커패시터와 펄스 변압기를 사용하여 만든 이러한 자유 실행 발진기입니다.

차단 발진기를 사용하여 Astable 및 Monostable 작동이 가능합니다. 그러나 쌍 안정 작동은 불가능합니다. 그들을 살펴 보자.

단 안정 차단 발진기

차단 발진기에 단일 펄스가 필요한 경우 상태를 변경하기 위해이를 단 안정 차단 발진기 회로라고합니다. 이러한 단 안정 차단 발진기는 두 가지 유형이 있습니다. 그들은

- 기본 타이밍이있는 단 안정 차단 발진기

- 이미 터 타이밍이있는 단 안정 차단 발진기

이들 모두에서, 타이밍 저항 R은 트랜지스터의베이스에 배치 될 때베이스 타이밍 회로가되고 트랜지스터의 에미 터에 배치 될 때 에미 터 타이밍 회로가되는 게이트 폭을 제어한다.

명확한 이해를 위해 기본 타이밍 단 안정 멀티 바이브레이터의 작동에 대해 논의하겠습니다.

기본 타이밍이있는 트랜지스터 트리거 단 안정 차단 발진기

트랜지스터, 피드백을위한 펄스 트랜스포머 및 트랜지스터베이스의 저항은베이스 타이밍을 가진 트랜지스터 트리거 단 안정 차단 발진기의 회로를 구성합니다. 여기에 사용 된 펄스 트랜스포머의 권선비는n: 1 베이스 회로가있는 곳 n컬렉터 회로를 켤 때마다 회전합니다. 저항 R은 펄스 지속 시간을 제어하는 트랜지스터의베이스에 직렬로 연결됩니다.

처음에는 트랜지스터가 OFF 상태입니다. 다음 그림에서 볼 수 있듯이 VBB는 0 또는 너무 낮은 것으로 간주되어 무시할 수 있습니다.

컬렉터의 전압 은 장치가 꺼져 있기 때문에 V CC 입니다. 그러나 콜렉터에 네거티브 트리거가 적용되면 전압이 감소합니다. 변압기의 권선 극성으로 인해 컬렉터 전압은 내려 가고 기본 전압은 상승합니다.

에미 터 전압의베이스가 컷인 전압보다 커지면

$$V_{BE} > V_\gamma$$

그런 다음 작은 기본 전류가 관찰됩니다. 이것은 콜렉터 전압을 감소시키는 콜렉터 전류를 증가시킵니다. 이 동작은 더 누적되어 콜렉터 전류를 증가시키고 콜렉터 전압을 더욱 감소시킵니다. 회생 피드백 동작으로 루프 게인이 증가하면 트랜지스터가 빠르게 포화됩니다. 그러나 이것은 안정적인 상태가 아닙니다.

그런 다음 작은 기본 전류가 관찰됩니다. 이것은 콜렉터 전압을 감소시키는 콜렉터 전류를 증가시킵니다. 이 동작은 더 누적되어 콜렉터 전류를 증가시키고 콜렉터 전압을 더욱 감소시킵니다. 회생 피드백 동작으로 루프 게인이 증가하면 트랜지스터가 빠르게 포화됩니다. 그러나 이것은 안정적인 상태가 아닙니다.

트랜지스터가 포화 상태가되면 콜렉터 전류가 증가하고베이스 전류는 일정합니다. 이제 콜렉터 전류가 천천히 커패시터를 충전하기 시작하고 변압기의 전압이 감소합니다. 변압기 권선 극성으로 인해 기본 전압이 증가합니다. 이것은 차례로 기본 전류를 감소시킵니다. 이 누적 동작은 트랜지스터를 회로의 안정적인 상태 인 차단 상태로 만듭니다.

그만큼 output waveforms 다음과 같습니다-

메인 disadvantage이 회로의 출력 펄스 폭은 안정적으로 유지 될 수 없습니다. 우리는 콜렉터 전류가

$$i_c = h_{FE}i_B$$

h FE 는 온도에 따라 다르며 펄스 폭은 이에 따라 선형 적으로 변하기 때문에 출력 펄스 폭은 안정적 일 수 없습니다. 또한 h FE 는 사용되는 트랜지스터에 따라 다릅니다.

어쨌든 저항이 이미 터에 배치되면이 단점을 제거 할 수 있습니다. 즉, 해결책은 emitter timing circuit. 위의 조건이 발생하면 에미 터 타이밍 회로에서 트랜지스터가 OFF되어 안정된 출력을 얻을 수 있습니다.

불안정한 차단 발진기

차단 발진기가 자동으로 상태를 변경할 수있는 경우이를 불안정 차단 발진기 회로라고합니다. 이 불안정한 차단 발진기는 두 가지 유형이 있습니다. 그들은

- 다이오드 제어 불안정 차단 발진기

- RC 제어 불안정 차단 발진기

다이오드 제어 비정상 차단 발진기에서 컬렉터에 배치 된 다이오드는 차단 발진기의 상태를 변경합니다. RC 제어 불안정 차단 발진기에서 타이밍 저항 R과 커패시터 C는 펄스 타이밍을 제어하기 위해 이미 터 섹션에서 네트워크를 형성합니다.

명확한 이해를 위해 Diode 제어 Astable 차단 발진기의 작동에 대해 논의하겠습니다.

다이오드 제어 불안정 차단 발진기

다이오드 제어 Astable 차단 발진기는 콜렉터 회로에 펄스 변압기를 포함합니다. 2 차 트랜스포머와 트랜지스터베이스 사이에 커패시터가 연결됩니다. 1 차 변압기와 다이오드는 컬렉터에 연결됩니다.

안 initial pulse 프로세스를 시작하기 위해 트랜지스터의 컬렉터에 주어지고 거기에서 no pulses are required회로는 Astable Multivibrator로 작동합니다. 아래 그림은 다이오드 제어 Astable 차단 발진기의 회로를 보여줍니다.

처음에는 트랜지스터가 OFF 상태입니다. 회로를 시작하기 위해 음의 트리거 펄스가 컬렉터에 적용됩니다. 양극이 컬렉터에 연결된 다이오드는 역 바이어스 상태가되며이 네거티브 트리거 펄스를 적용하면 꺼집니다.

이 펄스는 펄스 변압기에 적용되며 권선 극성 (그림 참조)으로 인해 위상 반전없이 동일한 양의 전압이 유도됩니다. 이 전압은 커패시터를 통해베이스쪽으로 흐르며베이스 전류에 기여합니다. 이 기준 전류는 컷 - 인 전압, 트랜지스터 Q 푸시 교차 에미 터 전압, 일부 염기 개발 하나를 ON으로한다. 이제 트랜지스터 Q 1 의 콜렉터 전류가 상승하여 다이오드와 변압기 모두에 적용됩니다. 초기에 OFF였던 다이오드가 이제 ON됩니다. 변압기 1 차 권선으로 유도되는 전압은 커패시터가 충전을 시작하는 변압기 2 차 권선으로 약간의 전압을 유도합니다.

커패시터는 충전되는 동안 전류를 전달하지 않으므로 기본 전류 i B 가 흐르지 않습니다. 그러면 트랜지스터 Q 1이 꺼집니다. 따라서 상태가 변경됩니다.

이제 ON 상태였던 다이오드에는 전압이 약간 있고, 트랜스포머 1 차측에 적용되어 2 차측으로 유도됩니다. 이제 커패시터를 통해 전류가 흐르고 커패시터가 방전됩니다. 따라서베이스 전류 i B 가 흐르면서 트랜지스터가 다시 켜집니다. 출력 파형은 다음과 같습니다.

다이오드가 트랜지스터의 상태를 변경하는 데 도움이되므로이 회로는 다이오드로 제어됩니다. 또한 트리거 펄스는 시작시에만 적용되는 반면 회로는 자체적으로 상태를 계속 변경하기 때문에이 회로는 불안정 발진기입니다. 따라서 다이오드 제어 불안정 차단 발진기라는 이름이 주어집니다.

또 다른 유형의 회로는 트랜지스터의 이미 터 부분에 R 및 C 조합을 사용하며 RC 제어 불안정 차단 발진기 회로라고합니다.

지금까지 우리는 다른 펄스 회로를 보았습니다. 때때로 우리는 그러한 펄스 입력의 적용을 특정 기간으로 제한 할 필요가 있습니다. 이 측면에서 우리를 돕는 회로는Sampling gate circuit. 이것들은 또한linear gates 또는 transmission gates 또는 selection circuits.

이러한 샘플링 게이트는 출력 신호가 입력 신호와 같거나 그렇지 않으면 0 인 특정 시간 간격에서 전송 신호를 선택하는 데 도움이됩니다. 해당 기간은control signal 또는 selection signal.

샘플링 게이트

샘플링 게이트의 경우 출력 신호는 입력과 동일하거나 선택한 시간 간격의 입력 신호에 비례해야하며 그렇지 않으면 0이어야합니다. 선택한 기간을Transmission Period 다른 기간은 Non-transmission Period. 이것은control signalV C로 표시됩니다 . 다음 그림은이 점을 설명합니다.

제어 신호 V C 가 V 1 에있을 때 샘플링 게이트가 닫히고 V C 가 V 2 에있을 때 개방됩니다. T 펄스 폭 g는 게이트 펄스가인가되는 시간을 나타낸다.

샘플링 게이트의 유형

샘플링 게이트의 유형은 다음과 같습니다.

Unidirectional sampling sgates− 이러한 유형의 샘플링 게이트는 양 또는 음의 펄스를 통과시킬 수 있습니다. 그들은 다이오드를 사용하여 구성됩니다.

Bidirectional sampling gate− 이러한 유형의 샘플링 게이트는 포지티브 및 네거티브 진행 펄스를 모두 통과시킬 수 있습니다. 그들은 다이오드 또는 BJT를 사용하여 구성됩니다.

사용되는 스위치 유형

샘플링 게이트는 직렬 또는 분로 스위치를 사용하여 구성 할 수 있습니다. 스위치를 열거 나 닫아야하는 시간은 게이팅 펄스 신호에 의해 결정됩니다. 이 스위치는 다이오드 및 트랜지스터와 같은 능동 소자로 대체됩니다.

다음 그림은 시리즈 및 션트 스위치를 사용하는 샘플링 게이트의 블록 다이어그램을 보여줍니다.

직렬 스위치를 사용한 샘플링 게이트

이 유형의 스위치에서 스위치 S가 닫히면 출력은 입력과 정확히 동일하거나 비례합니다. 그 기간은Transmission Period.

스위치 S가 열려 있으면 출력은 0 또는 접지 신호가됩니다. 그 기간은Non-transmission Period.

션트 스위치를 사용한 샘플링 게이트

이 유형의 스위치에서 스위치 S가 닫히면 출력은 0 또는 접지 신호가됩니다. 그 기간은Non-transmission Period.

스위치 S가 열려 있으면 출력은 입력과 정확히 같거나 비례합니다. 그 기간은Transmission Period.

샘플링 게이트는 디지털 회로의 논리 게이트와 완전히 다릅니다. 또한 펄스 또는 전압 레벨로 표시됩니다. 그러나 그들은 디지털 게이트이며 출력은 입력의 정확한 복제가 아닙니다. 샘플링 게이트 회로는 출력이 입력의 정확한 복제 인 아날로그 게이트입니다.

다음 장에서는 샘플링 게이트의 유형에 대해 설명합니다.

샘플링 게이트의 개념을 살펴본 후 이제 샘플링 게이트의 유형을 이해해 보겠습니다. 단방향 샘플링 게이트는이를 통해 포지티브 또는 네거티브 진행 펄스를 전달할 수 있습니다. 그들은 다이오드를 사용하여 구성됩니다.

단방향 샘플링 게이트 회로는 커패시터 C, 다이오드 D 및 두 개의 저항 R 1 및 RL로 구성 됩니다. 신호 입력은 커패시터에 제공되고 제어 입력은 저항 R 1에 제공 됩니다. 출력은 부하 저항 R L을 통해 이루어 집니다. 회로는 다음과 같습니다.

다이오드의 기능에 따라 다이오드의 양극이 다이오드의 음극보다 양극 일 때만 전도됩니다. 다이오드의 입력에 양의 신호가 있으면 전도합니다. 게이트 신호가 ON되는 시간이 전송주기입니다. 따라서 입력 신호가 전송되는 기간 동안입니다. 그렇지 않으면 전송이 불가능합니다.

다음 그림은 입력 신호와 게이트 신호의 기간을 보여줍니다.

입력 신호는 그림과 같이 게이트가 ON 된 시간 동안 만 전송됩니다.

우리가 가지고있는 회로에서

다이오드의 양극에는 두 신호 (V S 및 V C ) 가 적용됩니다 . 양극의 전압이 V P 로 표시되고 음극의 전압이 V N 으로 표시되면 출력 전압은 다음과 같이 얻어집니다.

$$V_o = V_P = (V_S + V_C) > V_N$$

따라서 다이오드는 순방향 바이어스 상태입니다.

$$V_O = V_S + V_1 > V_N$$

그때

$$V_O = V_S$$

V 1 = 0 일 때 ,

그때

$$V_O = V_S + V_1 \: Which \: means \: V_O = V_S$$

V 1 = 0 의 이상적인 값 .

따라서 V 1 = 0이면 전체 입력 신호가 출력에 나타납니다. V 1 의 값 이 음수이면 일부 입력이 손실되고 V 1 이 양수이면 입력과 함께 추가 신호가 출력에 나타납니다.

이 모든 일은 전송 기간 동안 발생합니다.

미 전송 기간 동안

$$V_O = 0$$

다이오드가 역 바이어스 상태이므로

양극의 전압이 음극의 전압보다 낮을 때,

$$V_S + V_C < 0 \: Volts$$

미 전송 기간 동안

$$V_C = V_2$$

$$V_S + V_2 < 0$$

V 2의 크기는 V s 보다 매우 높아야 합니다.

$$|V_2| ≫ V_S$$

다이오드가 역 바이어스에 있기 때문에 전압 V S 및 V C 의 합은 음수 여야합니다. V C ( 이제 V 2 임)는 V S 가 양수 이지만 두 전압의 합이 음의 결과를 생성하도록 가능한 한 음수 여야합니다.

특수한 상황들

이제 제어 전압이 음의 값인 여러 입력 전압 값에 대한 몇 가지 사례를 살펴 보겠습니다.

사례 1

V S = 10V 및 V C = -10v (V 1 ) ~ -20v (V 2 ) 인 예를 들어 보겠습니다.

이제이 두 신호 (V S 및 V C ) 가 적용될 때 양극의 전압은

$$V_P = V_S + V_C$$

이것은 전송주기에 관한 것이므로 V C 는 V 1 만 고려됩니다 .

$$V_O = (10V) + (-10V) = 0V$$

따라서 약간의 입력 전압이 적용 되더라도 출력은 0이됩니다. 다음 그림은이 점을 설명합니다.

사례 2

V S = 10V 및 V C = -5v (V 1 ) ~ -20v (V 2 ) 인 예를 들어 보겠습니다.

이제이 두 신호 (V S 및 V C ) 가 적용될 때 양극의 전압은

$$V_P = V_S + V_C$$

이것은 전송주기에 관한 것이므로 V C 는 V 1 만 고려됩니다 .

$$V_O = (10V) + (-5V) = 5V$$

따라서 출력은 5V가됩니다. 다음 그림은이 점을 설명합니다.

사례 3

V S = 10V 및 V C = 0v (V 1 ) ~ -20v (V 2 ) 인 예를 들어 보겠습니다.

이제이 두 신호 (V S 및 V C ) 가 적용될 때 양극의 전압은

$$V_P = V_S + V_C$$

이것은 전송주기에 관한 것이므로 V C 는 V 1 만 고려됩니다 .

$$V_O = (10V) + (0V) = 10V$$

따라서 출력은 10V가됩니다. 다음 그림은이 점을 설명합니다.

사례 4

V S = 10V 및 V C = 5v (V 1 ) ~ -20v (V 2 ) 인 예를 들어 보겠습니다.

이제이 두 신호 (V S 및 V C ) 가 적용될 때 양극의 전압은

$$V_P = V_S + V_C$$

이것은 전송주기에 관한 것이므로 V C 는 V 1 만 고려됩니다 .

$$V_O = (10V) + (5V) = 15V$$

따라서 출력은 15V가됩니다.

출력 전압은 적용된 제어 전압의 영향을받습니다. 이 전압은 입력에 추가되어 출력을 생성합니다. 따라서 출력에 영향을 미칩니다.

다음 그림은 두 신호의 중첩을 보여줍니다.

게이트 전압 만 가해지는 동안 출력은 5v가되는 것을 볼 수 있습니다. 두 신호가 모두 적용되면 V P 가 V O 로 나타납니다 . 비 전송 기간 동안 출력은 0v입니다.

위 그림에서 알 수 있듯이 (V S = 0 일 때) 입력 신호가인가되지 않더라도 전송주기와 비 전송주기 동안의 출력 신호의 차이를 다음과 같이 부릅니다.Pedestal. 이 받침대는 양수 또는 음수 일 수 있습니다. 이 예에서는 출력에 포지티브 받침대가 있습니다.

RC가 제어 전압에 미치는 영향

제어 전압이 정상 상태에 도달하기 전에 입력 신호가 적용되면 출력에 약간의 왜곡이 발생합니다.

제어 신호가 0v 일 때 입력 신호가 주어질 때만 올바른 출력을 얻습니다. 이 0v가 안정된 값입니다. 그 전에 입력 신호가 주어지면 왜곡이 발생합니다.

A에서 제어 전압의 느린 상승은 RC 회로가 있기 때문입니다. RC의 결과 인 시간 상수는이 파형의 모양에 영향을줍니다.

단방향 샘플링 게이트의 장단점

단방향 샘플링 게이트의 장단점을 살펴 보겠습니다.

장점

회로는 간단합니다.

입력과 출력 사이의 시간 지연이 너무 낮습니다.

더 많은 입력으로 확장 할 수 있습니다.

비 전송 기간에는 전류가 흐르지 않습니다. 따라서 대기 상태에서는 전력 손실이 없습니다.

단점

제어 신호와 입력 신호 (V C 및 V S ) 간에 상호 작용이 있습니다.

입력 수가 증가하면 제어 입력에 대한 부하가 증가합니다.

출력 제어 입력 전압 V에 민감한 1 (V의 상위 C )

한 순간에 하나의 입력 만 적용되어야합니다.

제어 신호의 느린 상승 시간으로 인해 정상 상태에 도달하기 전에 입력 신호가 적용되면 출력이 왜곡 될 수 있습니다.

지금까지 논의한 단방향 샘플링 게이트 회로에는 단일 입력이 있습니다. 이 장에서는 둘 이상의 입력 신호를 처리 할 수있는 몇 가지 단방향 샘플링 게이트 회로에 대해 설명하겠습니다.

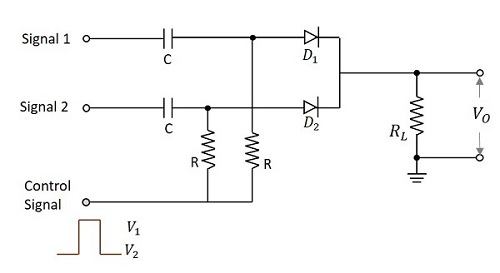

단방향 샘플링 게이트 회로는 동일한 값의 커패시터와 저항으로 구성됩니다. 여기서는 두 개의 입력이있는 두 개의 입력 단방향 다이오드 샘플링 게이트가 고려됩니다. 이 회로에는 동일한 값의 두 개의 커패시터와 두 개의 저항이 있습니다. 그들은 각각 두 개의 다이오드로 연결됩니다.

제어 신호는 저항에 적용됩니다. 출력은 부하 저항을 통해 이루어집니다. 아래 그림은 둘 이상의 입력 신호가있는 단방향 다이오드 샘플링 게이트의 회로도를 보여줍니다.

제어 입력이 주어지면

전송 기간 동안 V C = V 1 에서 다이오드 D 1 및 D 2 모두 순방향 바이어스됩니다. 이제 출력은 세 입력의 합계가됩니다.

$$V_O = V_{S1} + V_{S2} + V_C$$

이상적인 값인 V 1 = 0v의 경우,

$$V_O = V_{S1} + V_{S2}$$

여기에는 전송 기간 중 임의의 순간에 하나의 입력 만 적용되어야한다는 큰 제한이 있습니다. 이것은이 회로의 단점입니다.

비 전송 기간 동안

$$V_C = V_2$$

두 다이오드는 모두 역 바이어스가되어 개방 회로를 의미합니다.

이것은 출력을 만든다

$$V_O = 0V$$

이 회로의 주요 단점은 loading of the circuit입력 수가 증가하면 증가합니다. 이 제한은 제어 입력이 입력 신호 다이오드 다음에 제공되는 다른 회로에 의해 피할 수 있습니다.

받침대 감소

다양한 유형의 샘플링 게이트와 생성되는 출력을 거치면서 출력 파형에서 다음과 같은 추가 전압 레벨을 발견했습니다. Pedestal. 이것은 원치 않으며 약간의 소음을 생성합니다.

게이트 회로의 받침대 감소

입력 신호를인가하지 않았는데도 송신 기간과 비 송신 기간 동안의 출력 신호의 차이를 Pedestal. 포지티브 또는 네거티브 받침대 일 수 있습니다.

따라서 입력 신호가 없어도 게이팅 전압으로 인해 관찰되는 출력입니다. 이것은 원치 않는 것이며 줄여야합니다. 아래 회로는 게이트 회로에서 받침대를 줄이기 위해 설계되었습니다.

제어 신호가인가되면 전송 기간, 즉 V 1 에서 Q 1 이 켜지고 Q 2 가 꺼지고 V CC 가 R C 를 통해 Q 1에 적용됩니다 . V에서 nontransmission 기간 동안 즉, 반면 2 , Q 2 Q ON 및 턴 1 턴 OFF 및 V의 CC R 통해인가 C Q로 2 . 기본 전압 –V BB1 및 –V BB2 와 게이트 신호의 진폭은 두 트랜지스터 전류가 동일하고 결과적으로 대기 출력 전압 레벨이 일정하게 유지되도록 조정됩니다.

게이트 펄스 전압이 트랜지스터 의 V BE 에 비해 크면 , 각 트랜지스터는 전도되지 않을 때 차단 아래 훨씬 아래로 바이어스됩니다. 게이트 전압이 나타날 Q 때, (2) Q 전에 차단으로 구동 될 것이다 1 게이트 끝에 반면 실시하기 시작 Q 1 Q 전에 차단하도록 구동 될 2 실시하기 시작한다.

아래 그림은이를 더 나은 방식으로 설명합니다.

따라서 게이트 신호는 위 그림과 같이 나타납니다. 게이트 된 신호 전압은이 파형에 겹쳐서 나타납니다. 이러한 스파이크는 게이트 파형 상승 시간이 게이트 지속 시간에 비해 작은 경우 무시할 수있는 값입니다.

적다 drawbacks 이 회로의

명확한 상승 및 하강 시간으로 인해 급격한 스파이크 발생

RC를 통한 연속 전류는 많은 열을 방출합니다.

두 개의 바이어스 전압과 두 개의 제어 신호 소스 (서로 보완)는 회로를 복잡하게 만듭니다.

이러한 단점 외에이 회로는 게이트 회로에서 받침대를 줄이는 데 유용합니다.

단방향 게이트와 달리 양방향 게이트는 양극 및 음극의 신호를 모두 전송합니다. 이 게이트는 트랜지스터 또는 다이오드를 사용하여 구성 할 수 있습니다. 다른 유형의 회로에서 트랜지스터로 구성된 회로와 다이오드로 구성된 다른 회로를 살펴 보겠습니다.

트랜지스터를 사용하는 양방향 샘플링 게이트

기본 양방향 샘플링 게이트는 트랜지스터와 3 개의 저항으로 구성됩니다. 입력 신호 전압 V S 및 제어 입력 전압 V C 는 합산 저항을 통해 트랜지스터의베이스에 적용됩니다. 아래의 회로도는 트랜지스터를 사용하는 양방향 샘플링 게이트를 보여줍니다.

여기에 적용된 제어 입력 V C 는 두 레벨 V 1 및 V 2 와 펄스 폭 t p를 갖는 펄스 파형입니다 . 이 펄스 폭은 원하는 전송 간격을 결정합니다. 게이팅 신호는 입력이 전송되도록합니다. 게이팅 신호가 낮은 레벨 V 2 에있을 때 트랜지스터는 활성 영역으로 들어갑니다. 따라서 게이팅 입력이 상위 레벨로 유지 될 때까지 트랜지스터베이스에 나타나는 극성 중 하나의 신호가 샘플링되어 출력에서 증폭 된 것처럼 보입니다.

4 개의 다이오드 양방향 샘플링 게이트

양방향 샘플링 게이트 회로도 다이오드를 사용하여 만들어집니다. 2 다이오드 양방향 샘플링 게이트가이 모델의 기본 게이트입니다. 그러나 다음과 같은 단점이 거의 없습니다.

- 게인이 낮습니다.

- 제어 전압의 불균형에 민감합니다.

- Vn (분) 이 과도 할 수 있음

- 다이오드 정전 용량 누출이 있습니다.

4 개의 다이오드 양방향 샘플링 게이트가 개발되어 이러한 기능이 향상되었습니다. 2 개의 양방향 샘플링 게이트 회로는 그림과 같이 4 개의 다이오드 양방향 샘플링 게이트의 회로를 만들기 위해 2 개의 다이오드와 2 개의 평형 전압 + v 또는 -v를 추가하여 개선되었습니다.

제어 전압 V C 및 -V C 는 다이오드 D 3 및 D 4를 각각 역 바이어스합니다 . 전압 + v 및 –v는 다이오드 D 1 및 D 2를 각각 순방향 바이어스합니다 . 신호 소스는 저항 R 2 와 전도 다이오드 D 1 및 D 2를 통해 부하에 연결됩니다 . 다이오드 D 3 및 D 4 가 역 바이어스 됨에 따라 개방되고 게이트에서 제어 신호를 분리합니다. 따라서 제어 신호의 불균형은 출력에 영향을주지 않습니다.

적용된 제어 전압이 V n 및 –V n 이면 다이오드 D 3 및 D 4가 전도됩니다. 포인트 P 2 및 P 1 은 이러한 전압으로 클램핑되어 다이오드 D 1 및 D 2가 바이어스됩니다. 이제 출력은 0입니다.

전송 중에 다이오드 D 3 및 D 4 는 꺼집니다. 회로의 이득 A는 다음과 같이 주어진다.

$$A = \frac{R_C}{R_C + R_2} \times \frac{R_L}{R_L + (R_s/2)}$$

따라서 제어 전압 적용을 선택하면 전송이 활성화되거나 비활성화됩니다. 양쪽 극성의 신호는 게이팅 입력에 따라 전송됩니다.

샘플링 게이트의 응용

샘플링 게이트 회로에는 많은 응용 분야가 있습니다. 가장 일반적인 것은 다음과 같습니다.

- 샘플링 범위

- Multiplexers

- 샘플 및 홀드 회로

- 디지털-아날로그 변환기

- 잘게 잘린 안정기 증폭기

샘플링 게이트 회로의 응용 분야 중 샘플링 범위 회로가 널리 사용됩니다. 샘플링 범위의 블록 다이어그램에 대한 아이디어를 생각해 보겠습니다.

샘플링 범위

샘플링 스코프에서 디스플레이는 입력 파형의 샘플 시퀀스로 구성됩니다. 각 샘플은 파형의 일부 기준점에 대해 점진적으로 지연된 시간에 수집됩니다. 이것이 아래 블록 다이어그램에 표시된 샘플링 범위의 작동 원리입니다.

그만큼 ramp generator 그리고 stair case generator적용된 트리거 입력에 따라 파형을 생성합니다. 그만큼comparator 이 두 신호를 비교하여 출력을 생성하여 샘플링 게이트 회로에 제어 신호로 제공합니다.

제어 입력이 높을 때 입력은 sampling gate 출력으로 전달되며 제어 입력이 낮을 때마다 입력이 전송되지 않습니다.

샘플을 채취하는 동안 동일한 증분만큼 점진적으로 지연되는 시간 순간에 선택됩니다. 샘플은 지속 시간이 샘플링 게이트 제어의 지속 시간과 같고 진폭이 샘플링 시간에 입력 신호의 크기에 의해 결정되는 펄스로 구성됩니다. 그러면 생성되는 펄스 폭이 낮아집니다.

펄스 변조에서와 마찬가지로 신호를 샘플링하고 유지해야합니다. 그러나 펄스 폭이 낮기 때문에 증폭기 회로에 의해 증폭되어stretch 다이오드-커패시터 조합 회로에 주어 hold다음 샘플의 간격을 채우기 위해 신호. 이 회로에 주어진 출력vertical deflection plates 그리고 스위프 회로의 출력은 horizontal deflection plates 샘플링 스코프의 출력 파형을 표시합니다.