Systemy wbudowane - typy architektury

Mikrokontrolery 8051 pracują z 8-bitową szyną danych. Dzięki temu mogą obsługiwać zewnętrzną pamięć danych do 64 KB i zewnętrzną pamięć programu w najlepszym przypadku 64 KB. Łącznie mikrokontrolery 8051 mogą adresować 128k pamięci zewnętrznej.

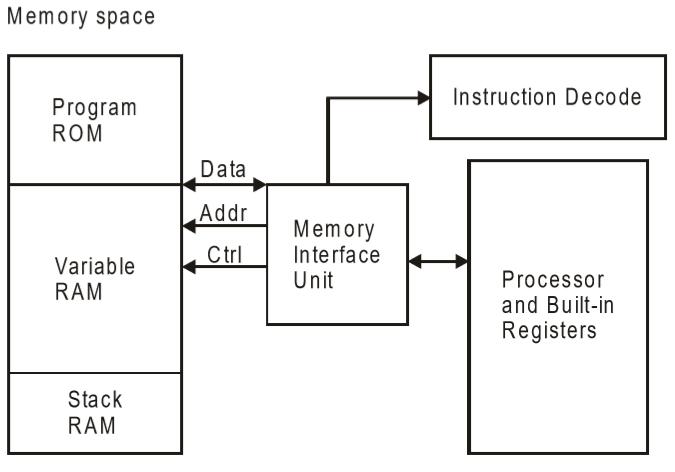

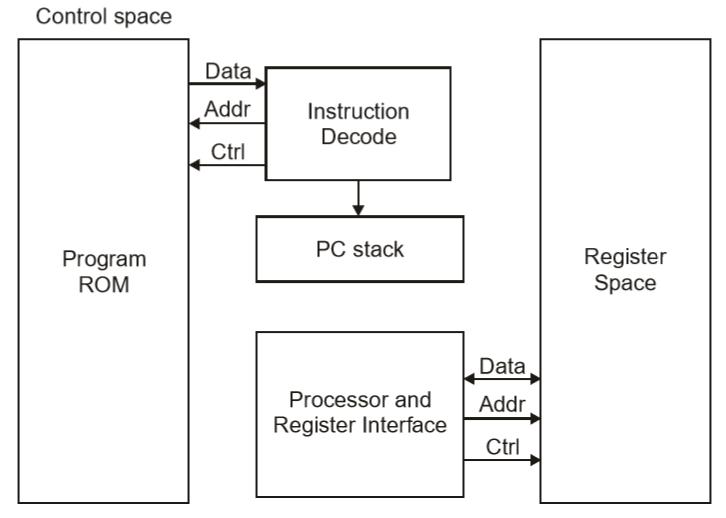

Gdy dane i kod znajdują się w różnych blokach pamięci, wówczas architektura jest określana jako Harvard architecture. W przypadku, gdy dane i kod znajdują się w tym samym bloku pamięci, wówczas architektura jest określana jakoVon Neumann architecture.

Architektura von Neumanna

Architektura von Neumanna została po raz pierwszy zaproponowana przez informatyka Johna von Neumanna. W tej architekturze istnieje jedna ścieżka lub magistrala danych dla instrukcji i danych. W rezultacie procesor wykonuje jedną operację na raz. Pobiera instrukcję z pamięci lub wykonuje operację odczytu / zapisu danych. Zatem pobranie instrukcji i operacja na danych nie mogą wystąpić jednocześnie, współużytkując wspólną magistralę.

Architektura Von-Neumanna obsługuje prosty sprzęt. Pozwala na użycie pojedynczej, sekwencyjnej pamięci. Dzisiejsze prędkości przetwarzania znacznie przewyższają czasy dostępu do pamięci i stosujemy bardzo szybką, ale niewielką ilość pamięci (cache) lokalnej procesora.

Architektura Harvardu

Architektura Harvardu oferuje oddzielne szyny pamięci i sygnałowe dla instrukcji i danych. W tej architekturze dane są przechowywane w całości w CPU i nie ma dostępu do pamięci instrukcji w postaci danych. Komputery mają oddzielne obszary pamięci dla instrukcji programu i danych przy użyciu wewnętrznych szyn danych, umożliwiając jednoczesny dostęp zarówno do instrukcji, jak i danych.

Programy potrzebne do załadowania przez operatora; procesor nie mógł się uruchomić. W architekturze Harvardu nie ma potrzeby, aby te dwie pamięci miały wspólne właściwości.

Architektura Von-Neumanna a architektura Harvardu

Poniższe punkty odróżniają architekturę von Neumanna od architektury harwardzkiej.

| Architektura von Neumanna | Architektura Harvardu |

|---|---|

| Pojedyncza pamięć współdzielona przez kod i dane. | Oddzielne pamięci na kod i dane. |

| Procesor musi pobrać kod w oddzielnym cyklu zegara, a dane w innym cyklu zegara. Więc wymaga dwóch cykli zegara. | Pojedynczy cykl zegara jest wystarczający, ponieważ oddzielne magistrale są używane do dostępu do kodu i danych. |

| Większa prędkość, a tym samym mniej czasochłonne. | Mniejsza prędkość, a więc bardziej czasochłonna. |

| Prosty projekt. | Złożony projekt. |

CISC i RISC

CISC jest komputerem ze złożonym zestawem rozkazów. Jest to komputer, który może adresować dużą liczbę instrukcji.

We wczesnych latach osiemdziesiątych projektanci komputerów zalecali, aby komputery używały mniejszej liczby instrukcji z prostymi konstrukcjami, aby można je było wykonywać znacznie szybciej w procesorze bez konieczności używania pamięci. Takie komputery są klasyfikowane jako komputer ze zredukowanym zestawem instrukcji lub RISC.

CISC vs RISC

Poniższe punkty odróżniają CISC od RISC -

| CISC | RISC |

|---|---|

| Większy zestaw instrukcji. Łatwe do zaprogramowania | Mniejszy zestaw instrukcji. Trudne do zaprogramowania. |

| Prostszy projekt kompilatora, biorąc pod uwagę większy zestaw instrukcji. | Złożony projekt kompilatora. |

| Wiele trybów adresowania powodujących złożone formaty instrukcji. | Kilka trybów adresowania, naprawiono format instrukcji. |

| Długość instrukcji jest zmienna. | Długość instrukcji jest różna. |

| Wyższe cykle zegara na sekundę. | Niski cykl zegara na sekundę. |

| Nacisk kładziony jest na sprzęt. | Nacisk kładziony jest na oprogramowanie. |

| Jednostka sterująca realizuje duży zestaw instrukcji za pomocą jednostki mikroprogramu. | Każda instrukcja ma być wykonana sprzętowo. |

| Wolniejsze wykonanie, ponieważ instrukcje mają być odczytywane z pamięci i dekodowane przez jednostkę dekodera. | Szybsze wykonanie, ponieważ każda instrukcja ma być wykonywana sprzętowo. |

| Rurociągi nie są możliwe. | Potokowanie instrukcji jest możliwe, biorąc pod uwagę pojedynczy cykl zegara. |