Daha Fazla Girdi ile Tek Yönlü

Şimdiye kadar tartıştığımız tek yönlü örnekleme kapısı devrelerinin tek bir girişi vardır. Bu bölümde, birden fazla giriş sinyalini idare edebilen birkaç tek yönlü örnekleme kapısı devresini tartışalım.

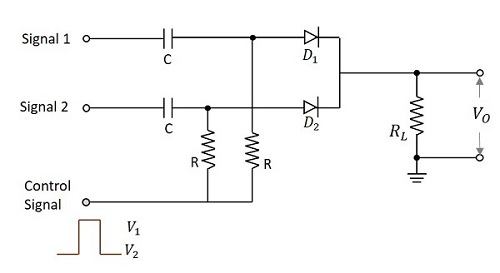

Tek yönlü bir örnekleme kapısı devresi, aynı değere sahip kapasitörler ve dirençlerden oluşur. Burada iki girişli iki girişli tek yönlü diyot örnekleme geçidi dikkate alınır. Bu devrede iki kapasitörümüz ve aynı değerde iki direncimiz var. Her biri iki diyotla bağlanırlar.

Kontrol sinyali dirençlere uygulanır. Çıkış, yük direnci üzerinden alınır. Aşağıdaki şekil, birden fazla giriş sinyaline sahip tek yönlü diyot örnekleme geçidi için devre şemasını göstermektedir.

Kontrol girişi verildiğinde,

İletim periyodu sırasında olan V C = V 1'de , hem D 1 hem de D 2 diyotları ileri doğru eğilimlidir. Şimdi çıktı, üç girdinin toplamı olacaktır.

$$ V_O = V_ {S1} + V_ {S2} + V_C $$

İdeal değer olan V 1 = 0v için,

$$ V_O = V_ {S1} + V_ {S2} $$

Burada, herhangi bir anda, iletim periyodu sırasında yalnızca bir girişin uygulanması gerektiğine dair büyük bir sınırlamamız var. Bu, bu devrenin bir dezavantajıdır.

İletim dışı dönemde,

$$ V_C = V_2 $$

Her iki diyot da açık devre anlamına gelen ters yönde olacaktır.

Bu çıktıyı yapar

$$ V_O = 0V $$

Bu devrenin ana dezavantajı, loading of the circuitgirdi sayısı arttıkça artar. Bu sınırlama, kontrol girişinin giriş sinyali diyotlarından sonra verildiği başka bir devre ile önlenebilir.

Kaide Azaltma

Farklı tipte örnekleme kapıları ve ürettikleri çıktılardan geçerken, çıkış dalga formlarında ekstra bir voltaj seviyesi ile karşılaştık. Pedestal. Bu istenmeyen bir durumdur ve biraz gürültü yaratır.

Bir Kapı devresinde Kaide'nin Azaltılması

Giriş sinyalleri uygulanmadığı halde iletim periyodu ve iletim dışı periyotta çıkış sinyallerindeki farka, Pedestal. Pozitif veya negatif bir kaide olabilir.

Dolayısıyla, giriş sinyali olmamasına rağmen geçit voltajı nedeniyle gözlemlenen çıktıdır. Bu istenmeyen bir durumdur ve azaltılması gerekir. Aşağıdaki devre, bir kapı devresindeki kaidenin indirgenmesi için tasarlanmıştır.

Kontrol sinyali uygulandığında, iletim periyodu sırasında, yani V 1'de , Q 1 AÇIK konuma gelir ve Q 2 KAPALI konuma geçer ve V CC , R C'den Q 1'e uygulanır . İletimsiz dönemde, yani V 2'de , Q 2 AÇIK konuma gelir ve Q 1 KAPALI hale gelir ve V CC , R C ile Q 2 arasında uygulanır . Temel gerilimler –V BB1 ve –V BB2 ve kapı sinyallerinin genliği, iki transistör akımı özdeş olacak şekilde ayarlanır ve sonuç olarak hareketsiz çıkış voltajı seviyesi sabit kalır.

Geçit darbe voltajı, transistörlerin V BE'sine kıyasla büyükse , o zaman her transistör, iletken olmadığında kesmenin çok altında önyargılıdır. Bu nedenle, kapı voltajı göründüğünde, Q 2 , Q 1 çalışmaya başlamadan önce kesilirken , kapının sonunda Q 1 , Q 2 çalışmaya başlamadan önce kesilmek üzere sürülür .

Aşağıdaki şekil bunu daha iyi bir şekilde açıklamaktadır.

Dolayısıyla kapı sinyalleri yukarıdaki şekildeki gibi görünür. Geçitli sinyal voltajı bu dalga formunun üzerine yerleştirilmiş olarak görünecektir. Geçit dalga biçimi yükselme süresi geçit süresine kıyasla küçükse, bu sivri uçlar ihmal edilebilir değerde olacaktır.

az var drawbacks gibi bu devrenin

Kesin yükselme ve düşme süreleri, keskin artışlarla sonuçlanır

RC aracılığıyla sürekli akım, çok fazla ısıyı dağıtır

İki öngerilim gerilimi ve iki kontrol sinyal kaynağı (birbirini tamamlayan) devreyi karmaşık hale getirir.

Bu dezavantajların dışında, bu devre bir kapı devresindeki kaidenin azaltılmasında kullanışlıdır.