555 Hẹn giờ

Các 555 TimerIC lấy tên của nó từ ba điện trở $ 5K \ Omega $ được sử dụng trong mạng phân áp của nó. IC này rất hữu ích để tạo ra độ trễ và dao động thời gian chính xác. Chương này giải thích chi tiết về Bộ hẹn giờ 555.

Sơ đồ chân và Sơ đồ chức năng

Trong phần này, trước tiên chúng ta hãy thảo luận về sơ đồ chân của IC Timer 555 và sau đó là sơ đồ chức năng của nó.

Sơ đồ chân

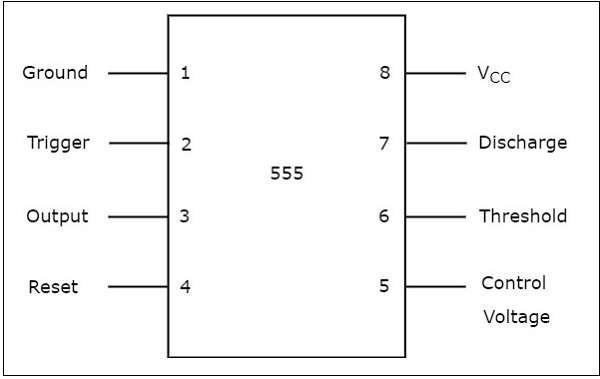

IC hẹn giờ 555 là một Gói nội tuyến kép (DIP) nhỏ 8 chân. Cácpin diagram của IC hẹn giờ 555 được hiển thị trong hình sau:

Ý nghĩa của mỗi chân có thể tự giải thích từ sơ đồ trên. IC Hẹn giờ 555 này có thể hoạt động với nguồn DC từ + 5V đến + 18V. Nó chủ yếu hữu ích để tạonon-sinusoidal các dạng sóng như hình vuông, đoạn đường nối, xung và v.v.

Sơ đồ chức năng

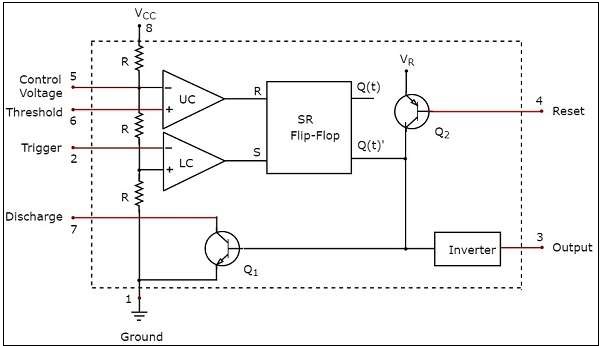

Biểu diễn bằng hình ảnh hiển thị các chi tiết bên trong của Bộ hẹn giờ 555 được gọi là sơ đồ chức năng.

Các functional diagram của IC hẹn giờ 555 được hiển thị trong hình sau:

Quan sát sơ đồ chức năng của Bộ định thời 555 có chứa một mạng phân áp, hai bộ so sánh, một tấm lật SR, hai bóng bán dẫn và một biến tần. Phần này thảo luận chi tiết về mục đích của từng khối hoặc thành phần -

Mạng phân chia điện áp

Mạng phân áp bao gồm ba điện trở $ 5K \ Omega $ được mắc nối tiếp giữa điện áp cung cấp $ V_ {cc} $ và đất.

Mạng này cung cấp điện áp $ \ frac {V_ {cc}} {3} $ giữa một điểm và mặt đất, nếu chỉ tồn tại một điện trở $ 5K \ Omega $. Tương tự, nó cung cấp điện áp $ \ frac {2V_ {cc}} {3} $ giữa một điểm và mặt đất, nếu chỉ tồn tại hai điện trở $ 5K \ Omega $.

Máy so sánh

Sơ đồ chức năng của IC hẹn giờ 555 bao gồm hai bộ so sánh: Bộ so sánh trên (UC) và Bộ so sánh dưới (LC).

Nhớ lại rằng a comparator so sánh hai đầu vào được áp dụng cho nó và tạo ra một đầu ra.

Nếu điện áp hiện tại tại đầu cuối không đảo của op-amp lớn hơn điện áp hiện tại tại đầu cuối đảo của nó, thì đầu ra của bộ so sánh sẽ là $ + V_ {sat} $. Đây có thể coi làLogic High ('1') trong biểu diễn kỹ thuật số.

Nếu điện áp hiện tại tại cực không nghịch đảo của op-amp nhỏ hơn hoặc bằng điện áp tại cực nghịch của nó, thì đầu ra của bộ so sánh sẽ là $ -V_ {sat} $. Đây có thể coi làLogic Low ('0') trong biểu diễn kỹ thuật số.

SR Flip-Flop

Nhớ lại rằng a SR flip-flophoạt động với chuyển đổi đồng hồ tích cực hoặc chuyển đổi đồng hồ âm. Nó có hai đầu vào: S và R, và hai đầu ra: Q (t) và Q (t) '. Các kết quả đầu ra, Q (t) & Q (t) 'bổ sung cho nhau.

Bảng sau đây cho thấy state table của một chiếc lật úp SR

| S | R | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - |

Ở đây, Q (t) & Q (t + 1) lần lượt là trạng thái hiện tại và trạng thái tiếp theo. Vì vậy, SR flip-flop có thể được sử dụng cho một trong ba chức năng này như Hold, Reset & Set dựa trên các điều kiện đầu vào, khi quá trình chuyển đổi tích cực (âm) của tín hiệu đồng hồ được áp dụng.

Các đầu ra của Bộ so sánh dưới (LC) và Bộ so sánh trên (UC) được áp dụng như inputs of SR flip-flop như trong sơ đồ chức năng của IC Timer 555.

Bóng bán dẫn và Biến tần

Sơ đồ chức năng của IC hẹn giờ 555 bao gồm một bóng bán dẫn npn $ Q_ {1} $ và một bóng bán dẫn pnp $ Q_ {2} $. Bóng bán dẫn npn $ Q_ {1} $ sẽ được BẬT nếu điện áp cơ bản đến bộ phát của nó là dương và lớn hơn điện áp cắt. Nếu không, nó sẽ bị TẮT.

Bóng bán dẫn pnp $ Q_ {2} $ được sử dụng làm buffer để cách ly đầu vào đặt lại khỏi bảng lật SR và bóng bán dẫn npn $ Q_ {1} $.

Các inverter được sử dụng trong sơ đồ chức năng của IC hẹn giờ 555 không chỉ thực hiện hành động đảo ngược mà còn khuếch đại mức công suất.

IC Hẹn giờ 555 có thể được sử dụng trong hoạt động ổn định đơn để tạo ra một xung ở đầu ra. Tương tự, nó có thể được sử dụng trong hoạt động ổn định để tạo ra một sóng vuông ở đầu ra.