ADC loại trực tiếp

Bộ chuyển đổi Analog sang kỹ thuật số (ADC)chuyển đổi tín hiệu tương tự thành tín hiệu kỹ thuật số. Tín hiệu kỹ thuật số được biểu diễn bằng mã nhị phân, là sự kết hợp của bit 0 và bit 1.

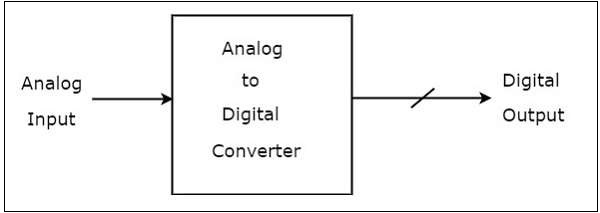

Các block diagram của một ADC được thể hiện trong hình sau:

Quan sát rằng trong hình bên trên, Bộ chuyển đổi Analog sang Digital (ADC)bao gồm một đầu vào tương tự duy nhất và nhiều đầu ra nhị phân. Nói chung, số lượng đầu ra nhị phân của ADC sẽ là lũy thừa của hai.

Có two typescủa ADC: ADC loại trực tiếp và ADC loại gián tiếp. Chương này thảo luận chi tiết về các ADC kiểu Trực tiếp.

Nếu ADC thực hiện chuyển đổi tương tự sang kỹ thuật số trực tiếp bằng cách sử dụng mã số (nhị phân) tương đương được tạo bên trong để so sánh với đầu vào tương tự, thì nó được gọi là Direct type ADC.

Sau đây là examples của ADC loại Trực tiếp -

- Loại bộ đếm ADC

- ADC xấp xỉ kế tiếp

- Flash loại ADC

Phần này thảo luận chi tiết về các ADC loại Trực tiếp này.

Loại bộ đếm ADC

A counter type ADC tạo ra đầu ra kỹ thuật số, gần bằng đầu vào tương tự bằng cách sử dụng hoạt động của bộ đếm bên trong.

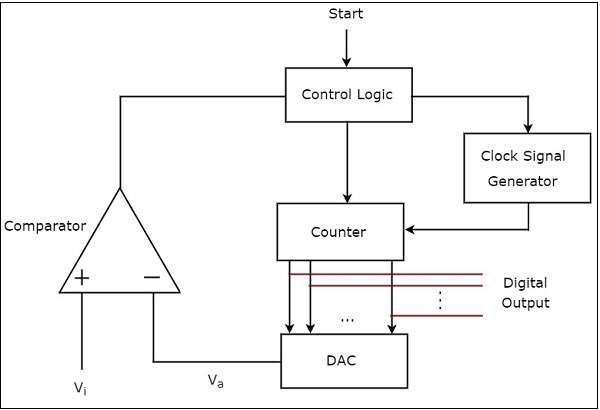

Các block diagram của loại bộ đếm ADC được hiển thị trong hình sau:

Bộ đếm kiểu ADC chủ yếu gồm 5 khối: Bộ tạo tín hiệu đồng hồ, Bộ đếm, DAC, Bộ so sánh và Điều khiển logic.

Các working của loại bộ đếm ADC như sau:

Các control logic đặt lại bộ đếm và bật bộ tạo tín hiệu đồng hồ để gửi xung đồng hồ đến bộ đếm, khi nó nhận được tín hiệu lệnh bắt đầu.

Các counterđược tăng lên một cho mỗi xung đồng hồ và giá trị của nó sẽ ở định dạng nhị phân (kỹ thuật số). Đầu ra này của bộ đếm được áp dụng như một đầu vào của DAC.

DACchuyển đổi đầu vào nhị phân (kỹ thuật số) nhận được, là đầu ra của bộ đếm, thành đầu ra tương tự. Bộ so sánh so sánh giá trị tương tự này, $ V_ {a} $ với giá trị đầu vào tương tự bên ngoài $ V_ {i} $.

Các output of comparator sẽ là ‘1’miễn là lớn hơn. Các hoạt động được đề cập trong hai bước trên sẽ được tiếp tục miễn là logic điều khiển nhận được '1' từ đầu ra của bộ so sánh.

Các output of comparator sẽ là ‘0’khi $ V_ {i} $ nhỏ hơn hoặc bằng $ V_ {a} $. Vì vậy, logic điều khiển nhận '0' từ đầu ra của bộ so sánh. Sau đó, logic điều khiển sẽ vô hiệu hóa bộ tạo tín hiệu đồng hồ để nó không gửi bất kỳ xung đồng hồ nào đến bộ đếm.

Tại thời điểm này, đầu ra của bộ đếm sẽ được hiển thị dưới dạng digital output. Nó gần như tương đương với giá trị đầu vào tương tự bên ngoài tương ứng $ V_ {i} $.

ADC xấp xỉ kế tiếp

A successive approximation type ADC tạo ra đầu ra kỹ thuật số, gần bằng với đầu vào tương tự bằng cách sử dụng kỹ thuật xấp xỉ liên tiếp bên trong.

Các block diagram của một ADC gần đúng liên tiếp được thể hiện trong hình sau

Bộ ADC xấp xỉ kế tiếp chủ yếu bao gồm 5 khối - Bộ tạo tín hiệu đồng hồ, Thanh ghi xấp xỉ kế tiếp (SAR), DAC, bộ so sánh và logic điều khiển.

Các working của một ADC gần đúng liên tiếp như sau:

Các control logic đặt lại tất cả các bit của SAR và cho phép bộ tạo tín hiệu đồng hồ để gửi các xung đồng hồ đến SAR, khi nó nhận được tín hiệu lệnh bắt đầu.

Dữ liệu nhị phân (kỹ thuật số) có trong SARsẽ được cập nhật cho mọi xung đồng hồ dựa trên đầu ra của bộ so sánh. Đầu ra của SAR được áp dụng như một đầu vào của DAC.

DAC chuyển đổi đầu vào kỹ thuật số nhận được, là đầu ra của SAR, thành đầu ra tương tự. Bộ so sánh so sánh giá trị tương tự này $ V_ {a} $ với giá trị đầu vào tương tự bên ngoài $ V_ {i} $.

Các output of a comparatorsẽ là '1' miễn là $ V_ {i} $ lớn hơn $ V_ {a} $. Tương tự, đầu ra của bộ so sánh sẽ là '0', khi $ V_ {i} $ nhỏ hơn hoặc bằng $ V_ {a} $.

Các hoạt động được đề cập trong các bước trên sẽ được tiếp tục cho đến khi đầu ra kỹ thuật số là hợp lệ.

Đầu ra kỹ thuật số sẽ là đầu ra hợp lệ, khi nó gần như tương đương với giá trị đầu vào tương tự bên ngoài tương ứng $ V_ {i} $.

Flash loại ADC

A flash type ADCtạo ra đầu ra kỹ thuật số tương đương cho đầu vào tương tự tương ứng trong thời gian nhanh chóng. Do đó, ADC loại flash là ADC nhanh nhất.

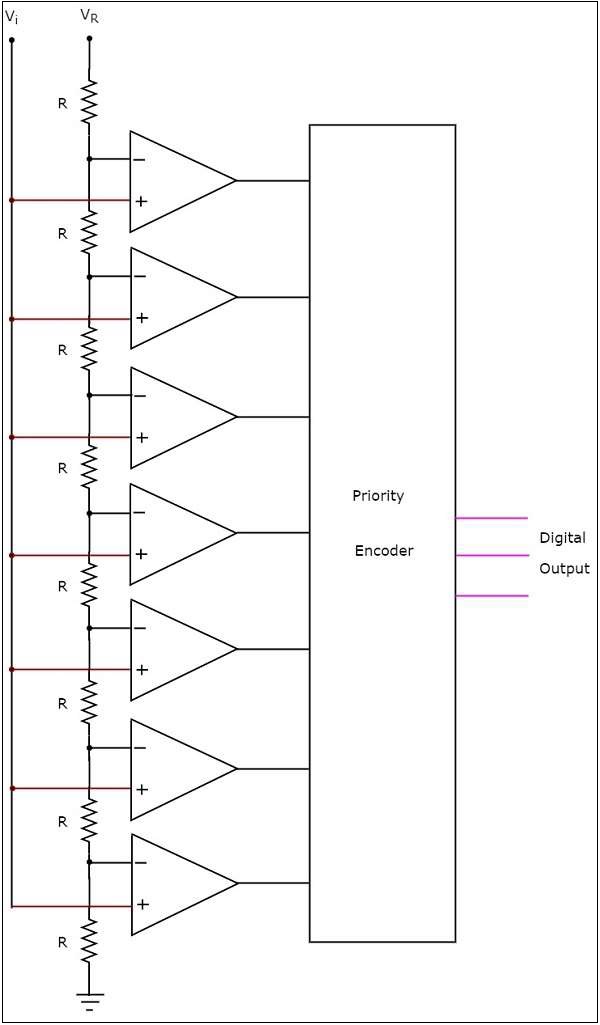

Các circuit diagram của ADC loại flash 3 bit được thể hiện trong hình sau:

ADC loại flash 3 bit bao gồm mạng phân áp, 7 bộ so sánh và bộ mã hóa ưu tiên.

Các working của ADC loại flash 3 bit như sau.

Các voltage divider networkchứa 8 điện trở bằng nhau. Điện áp tham chiếu $ V_ {R} $ được áp dụng trên toàn bộ mạng đó so với mặt đất. Điện áp rơi trên mỗi điện trở từ dưới lên trên so với mặt đất sẽ là bội số nguyên (từ 1 đến 8) của $ \ frac {V_ {R}} {8} $.

Ngoại thương input voltage$ V_ {i} $ được áp dụng cho đầu cuối không đảo ngược của tất cả các trình so sánh. Điện áp rơi trên mỗi điện trở từ dưới lên trên so với mặt đất được áp dụng cho đầu nối nghịch lưu của bộ so sánh từ dưới lên trên.

Tại một thời điểm, tất cả các bộ so sánh sẽ so sánh điện áp đầu vào bên ngoài với điện áp giảm ở đầu cuối đầu vào tương ứng khác. Điều đó có nghĩa là, các hoạt động so sánh diễn ra bởi mỗi bộ so sánhparallelly.

Các output of the comparatorsẽ là '1' với điều kiện là $ V_ {i} $ lớn hơn điện áp rơi ở đầu vào khác tương ứng. Tương tự, đầu ra của bộ so sánh sẽ là '0', khi $ V_ {i} $ nhỏ hơn hoặc bằng mức sụt điện áp hiện tại ở đầu vào khác tương ứng.

Tất cả các đầu ra của bộ so sánh được kết nối như đầu vào của priority encoderBộ mã hóa ưu tiên này tạo ra mã nhị phân (đầu ra kỹ thuật số), tương ứng với đầu vào ưu tiên cao có '1'.

Do đó, đầu ra của bộ mã hóa ưu tiên không là gì ngoài mã nhị phân tương đương (digital output) điện áp đầu vào tương tự bên ngoài, $ V_ {i} $.

ADC loại flash được sử dụng trong các ứng dụng có tốc độ chuyển đổi đầu vào tương tự thành dữ liệu kỹ thuật số rất cao.