Bộ chuyển đổi Digital sang Analog

A Digital to Analog Converter (DAC)chuyển đổi tín hiệu đầu vào kỹ thuật số thành tín hiệu đầu ra tương tự. Tín hiệu kỹ thuật số được biểu diễn bằng mã nhị phân, là sự kết hợp của bit 0 và 1. Chương này đề cập chi tiết đến Bộ chuyển đổi kỹ thuật số sang tương tự.

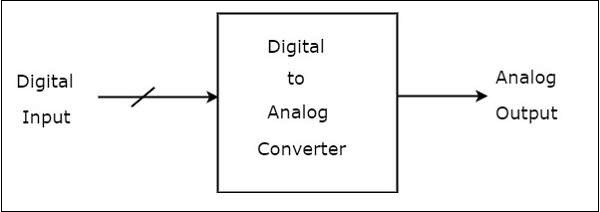

Các block diagram của DAC được thể hiện trong hình sau:

Bộ chuyển đổi Digital sang Analog (DAC) bao gồm một số đầu vào nhị phân và một đầu ra duy nhất. Nói chung,number of binary inputs của DAC sẽ là lũy thừa của hai.

Các loại DAC

Có two types của DAC

- DAC điện trở trọng số

- DAC thang R-2R

Phần này thảo luận chi tiết về hai loại DAC này -

DAC điện trở trọng số

Một điện trở có trọng số DAC tạo ra đầu ra tương tự, gần bằng với đầu vào kỹ thuật số (nhị phân) bằng cách sử dụng binary weighted resistorstrong mạch cộng đảo. Tóm lại, DAC điện trở có trọng số nhị phân được gọi là DAC điện trở có trọng số.

Các circuit diagram của một điện trở có trọng số nhị phân 3 bit DAC được thể hiện trong hình sau:

Nhớ lại rằng các bit của một số nhị phân chỉ có thể có một trong hai giá trị. tức là 0 hoặc 1. Hãy3-bit binary inputlà $ b_ {2} b_ {1} b_ {0} $. Ở đây, các bit $ b_ {2} $ và $ b_ {0} $ biểu thịMost Significant Bit (MSB) and Least Significant Bit (LSB) tương ứng.

Các digital switcheshiển thị trong hình trên sẽ được kết nối với đất, khi các bit đầu vào tương ứng bằng '0'. Tương tự, các công tắc kỹ thuật số hiển thị trong hình trên sẽ được kết nối với điện áp tham chiếu âm, $ -V_ {R} $ khi các bit đầu vào tương ứng bằng '1'.

Trong mạch trên, cực đầu vào không đảo ngược của op-amp được nối với đất. Điều đó có nghĩa là 0 vôn được áp dụng tại đầu cuối đầu vào không đảo ngược của op-amp.

Theo virtual short concept, điện áp tại cực đầu vào đảo ngược của opamp giống như điện áp hiện tại ở cực đầu vào không đảo của nó. Vì vậy, điện áp tại nút của thiết bị đầu cuối đầu vào đảo ngược sẽ là 0 vôn.

Các nodal equation tại nút của thiết bị đầu cuối đầu vào đảo ngược là:

$$ \ frac {0 + V_ {R} b_ {2}} {2 ^ {0} R} + \ frac {0 + V_ {R} b_ {1}} {2 ^ {1} R} + \ frac {0 + V_ {R} b_ {0}} {2 ^ {2} R} + \ frac {0-V_ {0}} {R_ {f}} = 0 $$

$$ => \ frac {V_ {0}} {R_ {f}} = \ frac {V_ {R} b_ {2}} {2 ^ {0} R} + \ frac {V_ {R} b_ {1 }} {2 ^ {1} R} + \ frac {V_ {R} b_ {0}} {2 ^ {2} R} $$

$$ => V_ {0} = \ frac {V_ {R} R_ {f}} {R} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac {b_ {1 }} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \} $$

Thay thế, $ R = 2R_ {f} $ trong phương trình trên.

$$ => V_ {0} = \ frac {V_ {R} R_ {f}} {2R_ {f}} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac { b_ {1}} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \} $$

$$ => V_ {0} = \ frac {V_ {R}} {2} \ left \ {\ frac {b_ {2}} {2 ^ {0}} + \ frac {b_ {1}} {2 ^ {1}} + \ frac {b_ {0}} {2 ^ {2}} \ right \} $$

Phương trình trên đại diện cho output voltage equationcủa một DAC điện trở có trọng số nhị phân 3 bit. Vì số bit là ba trong đầu vào nhị phân (kỹ thuật số), chúng ta sẽ nhận được bảy giá trị có thể có của điện áp đầu ra bằng cách thay đổi đầu vào nhị phân từ 000 đến 111 cho điện áp tham chiếu cố định, $ V_ {R} $.

Chúng tôi có thể viết generalized output voltage equation của DAC điện trở có trọng số nhị phân N-bit như hình dưới đây dựa trên phương trình điện áp đầu ra của DAC điện trở có trọng số nhị phân 3 bit.

$$ => V_ {0} = \ frac {V_ {R}} {2} \ left \ {\ frac {b_ {N-1}} {2 ^ {0}} + \ frac {b_ {N-2 }} {2 ^ {1}} + .... + \ frac {b_ {0}} {2 ^ {N-1}} \ right \} $$

Các disadvantages của một điện trở có trọng số nhị phân DAC như sau:

Sự khác biệt giữa các giá trị điện trở tương ứng với LSB & MSB sẽ tăng lên khi số lượng bit hiện diện trong đầu vào kỹ thuật số tăng lên.

Rất khó để thiết kế điện trở chính xác hơn khi số lượng bit hiện diện trong đầu vào kỹ thuật số tăng lên.

DAC thang R-2R

DAC R-2R Ladder khắc phục được nhược điểm của DAC điện trở trọng số nhị phân. Như tên cho thấy, R-2R Ladder DAC tạo ra đầu ra tương tự, gần như bằng với đầu vào kỹ thuật số (nhị phân) bằng cách sử dụngR-2R ladder network trong mạch cộng đảo.

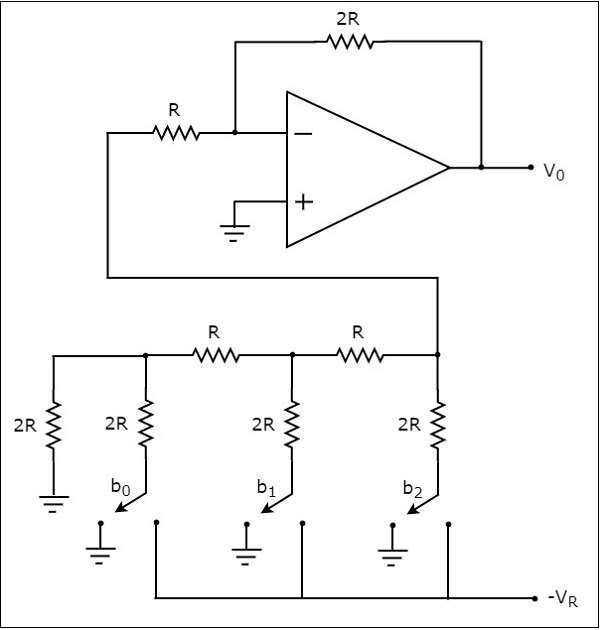

Cáccircuit diagramcủa DAC 3-bit R-2R Ladder được thể hiện trong hình sau:

Nhớ lại rằng các bit của một số nhị phân chỉ có thể có một trong hai giá trị. tức là 0 hoặc 1. Hãy3-bit binary inputlà $ b_ {2} b_ {1} b_ {0} $. Ở đây, các bit $ b_ {2} $ và $ b_ {0} $ lần lượt biểu thị Bit quan trọng nhất (MSB) và Bit ít quan trọng nhất (LSB).

Các công tắc kỹ thuật số hiển thị trong hình trên sẽ được kết nối với đất, khi các bit đầu vào tương ứng bằng '0'. Tương tự, các công tắc kỹ thuật số hiển thị trong hình trên sẽ được kết nối với điện áp tham chiếu âm, $ -V_ {R} $ khi các bit đầu vào tương ứng bằng '1'.

Rất khó để có được phương trình điện áp đầu ra tổng quát của DAC R-2R Ladder. Tuy nhiên, chúng ta có thể tìm thấy các giá trị điện áp đầu ra tương tự của R-2R Ladder DAC cho các kết hợp đầu vào nhị phân riêng lẻ một cách dễ dàng.

Các advantages của DAC R-2R Ladder như sau:

R-2R Ladder DAC chỉ chứa hai giá trị của điện trở: R và 2R. Vì vậy, có thể dễ dàng lựa chọn và thiết kế điện trở chính xác hơn.

Nếu có nhiều bit hơn trong đầu vào kỹ thuật số, thì chúng ta phải bao gồm thêm số phần R-2R cần thiết.

Do những ưu điểm trên, DAC R-2R Ladder được ưa chuộng hơn DAC điện trở trọng số nhị phân.