Bộ vi xử lý - Cấu hình chân 8086

8086 là bộ vi xử lý 16 bit đầu tiên có sẵn trong chip DIP 40 chân (Gói nội tuyến kép). Bây giờ chúng ta hãy thảo luận chi tiết về cấu hình chân của Bộ vi xử lý 8086.

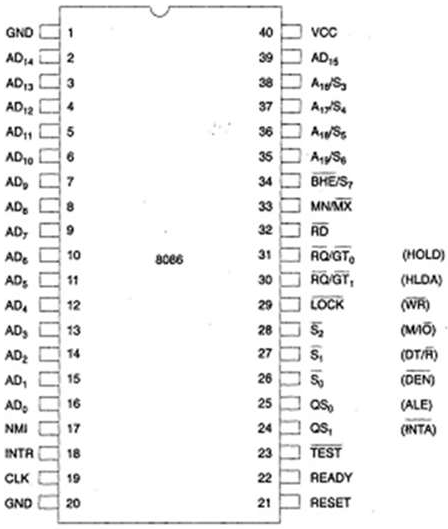

Sơ đồ chân 8086

Đây là sơ đồ chân của bộ vi xử lý 8086 -

Bây giờ chúng ta hãy thảo luận chi tiết về các tín hiệu -

Power supply and frequency signals

Nó sử dụng nguồn điện 5V DC ở chân V CC 40 và sử dụng nối đất ở chân V SS 1 và 20 cho hoạt động của nó.

Clock signal

Tín hiệu đồng hồ được cung cấp thông qua Pin-19. Nó cung cấp thời gian để bộ xử lý hoạt động. Tần số của nó là khác nhau đối với các phiên bản khác nhau, tức là 5MHz, 8MHz và 10MHz.

Address/data bus

AD0-AD15. Đây là 16 bus địa chỉ / dữ liệu. AD0-AD7 mang dữ liệu byte bậc thấp và AD8AD15 mang dữ liệu byte bậc cao. Trong chu kỳ xung nhịp đầu tiên, nó mang địa chỉ 16 bit và sau đó nó mang dữ liệu 16 bit.

Address/status bus

A16-A19 / S3-S6. Đây là 4 địa chỉ / trạng thái xe buýt. Trong chu kỳ xung nhịp đầu tiên, nó mang địa chỉ 4 bit và sau đó nó mang tín hiệu trạng thái.

S7/BHE

BHE là viết tắt của Bus High Enable. Nó có sẵn ở chân 34 và được sử dụng để chỉ ra việc truyền dữ liệu bằng bus dữ liệu D8-D15. Tín hiệu này ở mức thấp trong chu kỳ đồng hồ đầu tiên, sau đó nó hoạt động.

Read($\overline{RD}$)

Nó có sẵn ở chân 32 và được sử dụng để đọc tín hiệu cho hoạt động Đọc.

Ready

Nó có sẵn ở chân 22. Đây là tín hiệu báo nhận từ các thiết bị I / O mà dữ liệu được truyền. Đó là một tín hiệu cao đang hoạt động. Khi nó ở mức cao, nó chỉ ra rằng thiết bị đã sẵn sàng để truyền dữ liệu. Khi nó ở mức thấp, nó cho biết trạng thái chờ.

RESET

Nó có sẵn ở chân 21 và được sử dụng để khởi động lại quá trình thực thi. Nó khiến bộ xử lý chấm dứt ngay hoạt động hiện tại của nó. Tín hiệu này hoạt động ở mức cao trong 4 chu kỳ xung nhịp đầu tiên để ĐẶT LẠI bộ vi xử lý.

INTR

Nó có sẵn ở chân 18. Đây là một tín hiệu yêu cầu ngắt, được lấy mẫu trong chu kỳ xung nhịp cuối cùng của mỗi lệnh để xác định xem bộ xử lý có coi đây là một ngắt hay không.

NMI

Nó là viết tắt của ngắt không che được và có sẵn ở chân 17. Nó là một đầu vào được kích hoạt cạnh, gây ra một yêu cầu ngắt tới bộ vi xử lý.

$ \ overline {TEST} $

Tín hiệu này giống như trạng thái chờ và có sẵn ở chân 23. Khi tín hiệu này ở mức cao, thì bộ xử lý phải đợi trạng thái IDLE, nếu không thì quá trình thực thi tiếp tục.

MN/$\overline{MX}$

Nó là viết tắt của Minimum / Maximum và có sẵn ở chân 33. Nó cho biết bộ vi xử lý đang hoạt động ở chế độ nào; khi ở mức cao, nó hoạt động ở chế độ tối thiểu và đảo chiều.

INTA

Nó là một tín hiệu báo nhận ngắt và id có sẵn ở chân 24. Khi bộ vi xử lý nhận được tín hiệu này, nó sẽ báo nhận ngắt.

ALE

Nó là viết tắt của chốt kích hoạt địa chỉ và có sẵn ở chân 25. Một xung tích cực được tạo ra mỗi khi bộ xử lý bắt đầu bất kỳ hoạt động nào. Tín hiệu này cho biết sự sẵn có của một địa chỉ hợp lệ trên các đường địa chỉ / dữ liệu.

DEN

Nó là viết tắt của Data Enable và có sẵn ở chân 26. Nó được sử dụng để kích hoạt Bộ thu phát 8286. Bộ thu phát là một thiết bị dùng để tách dữ liệu ra khỏi bus địa chỉ / dữ liệu.

DT/R

Nó là viết tắt của tín hiệu Truyền / Nhận dữ liệu và có sẵn ở chân 27. Nó quyết định hướng của luồng dữ liệu qua bộ thu phát. Khi nó ở mức cao, dữ liệu được truyền ra ngoài và ngược lại.

M/IO

Tín hiệu này được sử dụng để phân biệt giữa bộ nhớ và các hoạt động I / O. Khi ở mức cao, nó cho biết hoạt động I / O và khi ở mức thấp cho biết hoạt động của bộ nhớ. Nó có sẵn tại pin 28.

WR

Nó là viết tắt của tín hiệu ghi và có sẵn ở chân 29. Nó được sử dụng để ghi dữ liệu vào bộ nhớ hoặc thiết bị đầu ra tùy thuộc vào trạng thái của tín hiệu M / IO.

HLDA

Nó là viết tắt của tín hiệu Hold Acknowledgement và có sẵn ở chân 30. Tín hiệu này ghi nhận tín hiệu HOLD.

HOLD

Tín hiệu này cho bộ xử lý biết rằng các thiết bị bên ngoài đang yêu cầu truy cập các bus địa chỉ / dữ liệu. Nó có sẵn tại pin 31.

QS1 and QS0

Đây là các tín hiệu trạng thái hàng đợi và có sẵn ở chân 24 và 25. Các tín hiệu này cung cấp trạng thái của hàng đợi lệnh. Điều kiện của chúng được thể hiện trong bảng sau:

| QS 0 | QS 1 | Trạng thái |

|---|---|---|

| 0 | 0 | Không hoạt động |

| 0 | 1 | Byte đầu tiên của mã opcode từ hàng đợi |

| 1 | 0 | Dọn sạch hàng đợi |

| 1 | 1 | Byte tiếp theo từ hàng đợi |

S0, S1, S2

Đây là các tín hiệu trạng thái cung cấp trạng thái hoạt động, được sử dụng bởi Bộ điều khiển Bus 8288 để tạo ra các tín hiệu điều khiển bộ nhớ & I / O. Chúng có sẵn tại pin 26, 27 và 28. Sau đây là bảng hiển thị trạng thái của chúng -

| S 2 | S 1 | S 0 | Trạng thái |

|---|---|---|---|

| 0 | 0 | 0 | Xác nhận ngắt |

| 0 | 0 | 1 | I / O Đọc |

| 0 | 1 | 0 | I / O Viết |

| 0 | 1 | 1 | Tạm dừng lại |

| 1 | 0 | 0 | Tìm nạp opcode |

| 1 | 0 | 1 | Đọc bộ nhớ |

| 1 | 1 | 0 | Ghi nhớ |

| 1 | 1 | 1 | Bị động |

LOCK

Khi tín hiệu này hoạt động, nó chỉ ra cho các bộ xử lý khác không yêu cầu CPU rời khỏi bus hệ thống. Nó được kích hoạt bằng cách sử dụng tiền tố LOCK trên bất kỳ hướng dẫn nào và có sẵn tại pin 29.

RQ/GT1 and RQ/GT0

Đây là các tín hiệu Request / Grant được các bộ xử lý khác sử dụng để yêu cầu CPU giải phóng bus hệ thống. Khi tín hiệu được nhận bởi CPU, sau đó nó sẽ gửi xác nhận. RQ / GT 0 có mức độ ưu tiên cao hơn RQ / GT 1 .