Bộ vi xử lý - Hướng dẫn nhanh

Bộ vi xử lý là một bộ phận điều khiển của một máy vi tính, được chế tạo trên một con chip nhỏ có khả năng thực hiện các hoạt động ALU (Đơn vị logic số học) và giao tiếp với các thiết bị khác được kết nối với nó.

Bộ vi xử lý bao gồm ALU, mảng thanh ghi và đơn vị điều khiển. ALU thực hiện các phép toán số học và logic trên dữ liệu nhận được từ bộ nhớ hoặc thiết bị đầu vào. Mảng thanh ghi bao gồm các thanh ghi được xác định bằng các chữ cái như B, C, D, E, H, L và bộ tích lũy. Khối điều khiển kiểm soát luồng dữ liệu và hướng dẫn trong máy tính.

Sơ đồ khối của một máy vi tính cơ bản

Bộ vi xử lý hoạt động như thế nào?

Bộ vi xử lý tuân theo một trình tự: Tìm nạp, Giải mã, rồi Thực thi.

Ban đầu, các lệnh được lưu trong bộ nhớ theo một thứ tự tuần tự. Bộ vi xử lý tìm nạp các lệnh đó từ bộ nhớ, sau đó giải mã nó và thực hiện các lệnh đó cho đến khi đạt được lệnh STOP. Sau đó, nó gửi kết quả ở dạng nhị phân đến cổng đầu ra. Giữa các quá trình này, thanh ghi lưu trữ dữ liệu tạm thời và ALU thực hiện các chức năng tính toán.

Danh sách các thuật ngữ được sử dụng trong bộ vi xử lý

Dưới đây là danh sách một số thuật ngữ thường dùng trong bộ vi xử lý -

Instruction Set - Nó là tập hợp các lệnh mà bộ vi xử lý có thể hiểu được.

Bandwidth - Là số bit được xử lý trong một lệnh duy nhất.

Clock Speed- Nó xác định số lượng hoạt động mỗi giây mà bộ xử lý có thể thực hiện. Nó được biểu thị bằng megahertz (MHz) hoặc gigahertz (GHz). Nó còn được gọi là Tốc độ đồng hồ.

Word Length- Nó phụ thuộc vào độ rộng của bus dữ liệu bên trong, thanh ghi, ALU, v.v. Một bộ vi xử lý 8 bit có thể xử lý dữ liệu 8 bit tại một thời điểm. Độ dài từ nằm trong khoảng từ 4 bit đến 64 bit tùy thuộc vào loại máy vi tính.

Data Types - Bộ vi xử lý có nhiều định dạng kiểu dữ liệu như nhị phân, BCD, ASCII, số có dấu và không dấu.

Các tính năng của một bộ vi xử lý

Dưới đây là danh sách một số tính năng nổi bật nhất của bất kỳ bộ vi xử lý nào -

Cost-effective - Các chip vi xử lý có sẵn với giá thấp và dẫn đến chi phí thấp.

Size - Bộ vi xử lý là chip kích thước nhỏ, do đó có thể di động.

Low Power Consumption - Bộ vi xử lý được sản xuất bằng công nghệ bán dẫn metaloxit nên tiêu thụ điện năng thấp.

Versatility - Các bộ vi xử lý rất linh hoạt vì chúng ta có thể sử dụng cùng một chip trong một số ứng dụng bằng cách cấu hình chương trình phần mềm.

Reliability - Tỷ lệ hỏng hóc của một vi mạch trong vi xử lý là rất thấp, do đó nó đáng tin cậy.

Một bộ vi xử lý có thể được phân thành ba loại:

Bộ xử lý RISC

RISC là viết tắt của Reduced Instruction Set Computer. Nó được thiết kế để giảm thời gian thực hiện bằng cách đơn giản hóa tập lệnh của máy tính. Sử dụng bộ xử lý RISC, mỗi lệnh chỉ yêu cầu một chu kỳ đồng hồ để thực thi kết quả trong thời gian thực thi thống nhất. Điều này làm giảm hiệu quả vì có nhiều dòng mã hơn, do đó cần nhiều RAM hơn để lưu các lệnh. Trình biên dịch cũng phải làm việc nhiều hơn để chuyển đổi các lệnh ngôn ngữ cấp cao thành mã máy.

Một số bộ xử lý RISC là -

- Nguồn PC: 601, 604, 615, 620

- DEC Alpha: 210642, 211066, 21068, 21164

- Bộ xử lý RISC MIPS: TS (R10000)

- PA-RISC: HP 7100LC

Kiến trúc của RISC

Kiến trúc bộ vi xử lý RISC sử dụng bộ hướng dẫn được tối ưu hóa cao. Nó được sử dụng trong các thiết bị di động như Apple iPod do hiệu quả sử dụng năng lượng.

Đặc điểm của RISC

Các đặc điểm chính của bộ xử lý RISC như sau:

Nó bao gồm các hướng dẫn đơn giản.

Nó hỗ trợ các định dạng kiểu dữ liệu khác nhau.

Nó sử dụng các chế độ địa chỉ đơn giản và hướng dẫn độ dài cố định cho đường ống.

Nó hỗ trợ đăng ký để sử dụng trong mọi ngữ cảnh.

Thời gian thực hiện một chu kỳ.

Hướng dẫn “TẢI” và “CỬA HÀNG” được sử dụng để truy cập vị trí bộ nhớ.

Nó bao gồm số lượng thanh ghi lớn hơn.

Nó bao gồm số lượng bóng bán dẫn ít hơn.

Bộ xử lý CISC

CISC là viết tắt của Complex Instruction Set Computer. Nó được thiết kế để giảm thiểu số lượng lệnh trên mỗi chương trình, bỏ qua số chu kỳ trên mỗi lệnh. Trọng tâm là xây dựng các hướng dẫn phức tạp trực tiếp vào phần cứng.

Trình biên dịch phải thực hiện rất ít công việc để dịch một ngôn ngữ cấp cao sang ngôn ngữ cấp hợp ngữ / mã máy vì độ dài của mã tương đối ngắn, do đó cần rất ít RAM để lưu các lệnh.

Một số Bộ xử lý CISC là -

- IBM 370/168

- VAX 11/780

- Intel 80486

Kiến trúc của CISC

Kiến trúc của nó được thiết kế để giảm chi phí bộ nhớ vì cần nhiều bộ nhớ hơn trong các chương trình lớn hơn, dẫn đến chi phí bộ nhớ cao hơn. Để giải quyết vấn đề này, có thể giảm số lượng lệnh trên mỗi chương trình bằng cách nhúng số lượng thao tác vào một lệnh đơn.

Đặc điểm của CISC

- Nhiều chế độ địa chỉ.

- Số lượng hướng dẫn lớn hơn.

- Độ dài thay đổi của các định dạng lệnh.

- Có thể cần một số chu kỳ để thực hiện một lệnh.

- Logic giải mã lệnh rất phức tạp.

- Cần có một hướng dẫn để hỗ trợ nhiều chế độ định địa chỉ.

Bộ xử lý đặc biệt

Đây là những bộ xử lý được thiết kế cho một số mục đích đặc biệt. Một số bộ vi xử lý đặc biệt được thảo luận ngắn gọn -

Bộ đồng xử lý

Bộ đồng xử lý là một bộ vi xử lý được thiết kế đặc biệt, có thể xử lý chức năng cụ thể của nó nhanh hơn nhiều lần so với bộ vi xử lý thông thường.

For example - Bộ đồng xử lý toán học.

Một số bộ đồng xử lý toán học của Intel là -

- 8087-được sử dụng với 8086

- 80287-used with 80286

- 80387-được sử dụng với 80386

Bộ xử lý đầu vào / đầu ra

Nó là một bộ vi xử lý được thiết kế đặc biệt có bộ nhớ cục bộ của riêng nó, được sử dụng để điều khiển các thiết bị I / O với sự tham gia tối thiểu của CPU.

For example -

- Bộ điều khiển DMA (Truy cập bộ nhớ trực tiếp)

- Bộ điều khiển bàn phím / chuột

- Bộ điều khiển hiển thị đồ họa

- Bộ điều khiển cổng SCSI

Máy vận chuyển (Máy tính bán dẫn)

Bộ chuyển tiếp là một bộ vi xử lý được thiết kế đặc biệt với bộ nhớ cục bộ của riêng nó và có các liên kết để kết nối bộ phát này với bộ phát khác để liên lạc giữa các bộ xử lý. Nó được thiết kế lần đầu tiên vào năm 1980 bởi Inmos và được nhắm mục tiêu sử dụng công nghệ VLSI.

Một máy phát có thể được sử dụng như một hệ thống xử lý đơn lẻ hoặc có thể được kết nối với các liên kết bên ngoài, giúp giảm chi phí xây dựng và tăng hiệu suất.

For example - Bộ vi xử lý 16-bit T212, 32-bit T425, dấu phẩy động (T800, T805 & T9000).

DSP (Bộ xử lý tín hiệu kỹ thuật số)

Bộ xử lý này được thiết kế đặc biệt để xử lý các tín hiệu tương tự thành dạng kỹ thuật số. Điều này được thực hiện bằng cách lấy mẫu mức điện áp trong các khoảng thời gian đều đặn và chuyển điện áp tại thời điểm đó thành dạng kỹ thuật số. Quá trình này được thực hiện bởi một mạch được gọi là bộ chuyển đổi tương tự sang kỹ thuật số, bộ chuyển đổi A sang D hoặc ADC.

DSP chứa các thành phần sau:

Program Memory - Nó lưu trữ các chương trình mà DSP sẽ sử dụng để xử lý dữ liệu.

Data Memory - Nó lưu trữ thông tin cần xử lý.

Compute Engine - Nó thực hiện xử lý toán học, truy cập chương trình từ bộ nhớ chương trình và dữ liệu từ bộ nhớ dữ liệu.

Input/Output - Nó kết nối với thế giới bên ngoài.

Các ứng dụng của nó là -

- Tổng hợp âm thanh và âm nhạc

- Nén âm thanh và video

- Xử lý tín hiệu video

- Tăng tốc đồ họa 2D và 3d.

For example - Dòng TMS 320 của Texas Instrument, ví dụ: TMS 320C40, TMS320C50.

8085 được phát âm là bộ vi xử lý "tám mươi lăm". Nó là bộ vi xử lý 8-bit được Intel thiết kế vào năm 1977 sử dụng công nghệ NMOS.

Nó có cấu hình sau:

- Xe buýt dữ liệu 8 bit

- Xe buýt địa chỉ 16 bit, có thể giải quyết tối đa 64KB

- Bộ đếm chương trình 16 bit

- Một con trỏ ngăn xếp 16 bit

- Sáu thanh ghi 8 bit được sắp xếp theo cặp: BC, DE, HL

- Yêu cầu nguồn cung cấp + 5V để hoạt động ở xung nhịp một pha 3.2 MHZ

Nó được sử dụng trong máy giặt, lò vi sóng, điện thoại di động, v.v.

Bộ vi xử lý 8085 - Đơn vị chức năng

8085 bao gồm các đơn vị chức năng sau:

Tích lũy

Nó là một thanh ghi 8 bit được sử dụng để thực hiện các phép toán số học, logic, I / O & LOAD / STORE. Nó được kết nối với bus dữ liệu nội bộ & ALU.

Toán học và đơn vị logic

Như tên cho thấy, nó thực hiện các phép toán số học và logic như Phép cộng, Phép trừ, AND, OR, v.v. trên dữ liệu 8 bit.

Đăng ký mục đích chung

Có 6 thanh ghi mục đích chung trong bộ xử lý 8085, tức là B, C, D, E, H & L. Mỗi thanh ghi có thể chứa dữ liệu 8-bit.

Các thanh ghi này có thể hoạt động theo cặp để chứa dữ liệu 16-bit và sự kết hợp ghép nối của chúng giống như BC, DE & HL.

Bộ đếm chương trình

Nó là một thanh ghi 16 bit được sử dụng để lưu vị trí địa chỉ bộ nhớ của lệnh tiếp theo sẽ được thực thi. Bộ vi xử lý gia tăng chương trình bất cứ khi nào một lệnh đang được thực thi, để bộ đếm chương trình trỏ đến địa chỉ bộ nhớ của lệnh tiếp theo sẽ được thực thi.

Con trỏ ngăn xếp

Nó cũng là một thanh ghi 16-bit hoạt động giống như ngăn xếp, luôn tăng / giảm 2 trong các hoạt động đẩy & bật.

Đăng ký tạm thời

Nó là một thanh ghi 8-bit, lưu trữ dữ liệu tạm thời của các phép toán số học và logic.

Cờ đăng ký

Nó là một thanh ghi 8 bit có năm flip-flop 1 bit, giữ 0 hoặc 1 tùy thuộc vào kết quả được lưu trữ trong bộ tích lũy.

Đây là bộ 5 dép xỏ ngón -

- Dấu hiệu)

- Zero (Z)

- Hộp đựng phụ (AC)

- Chẵn lẻ (P)

- Mang (C)

Vị trí bit của nó được hiển thị trong bảng sau:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| S | Z | AC | P | C Y |

Thanh ghi lệnh và bộ giải mã

Nó là một thanh ghi 8-bit. Khi một lệnh được tìm nạp từ bộ nhớ thì nó sẽ được lưu trữ trong thanh ghi lệnh. Bộ giải mã lệnh giải mã thông tin có trong thanh ghi lệnh.

Bộ định thời và điều khiển

Nó cung cấp thời gian và tín hiệu điều khiển để bộ vi xử lý thực hiện các hoạt động. Sau đây là các tín hiệu thời gian và điều khiển, điều khiển các mạch bên ngoài và bên trong -

- Tín hiệu điều khiển: READY, RD ', WR', ALE

- Tín hiệu trạng thái: S0, S1, IO / M '

- Tín hiệu DMA: HOLD, HLDA

- Tín hiệu ĐẶT LẠI: ĐẶT LẠI VÀO, ĐẶT LẠI

Kiểm soát ngắt

Như tên cho thấy nó kiểm soát các ngắt trong một quá trình. Khi một bộ vi xử lý đang thực hiện một chương trình chính và bất cứ khi nào xảy ra ngắt, bộ vi xử lý sẽ chuyển điều khiển từ chương trình chính sang xử lý yêu cầu đến. Sau khi hoàn thành yêu cầu, điều khiển quay trở lại chương trình chính.

Có 5 tín hiệu ngắt trong vi xử lý 8085: INTR, RST 7.5, RST 6.5, RST 5.5, TRAP.

Điều khiển đầu vào / đầu ra nối tiếp

Nó kiểm soát giao tiếp dữ liệu nối tiếp bằng cách sử dụng hai lệnh sau: SID (Dữ liệu đầu vào nối tiếp) và SOD (Dữ liệu đầu ra nối tiếp).

Bộ đệm địa chỉ và bộ đệm dữ liệu địa chỉ

Nội dung được lưu trữ trong con trỏ ngăn xếp và bộ đếm chương trình được tải vào bộ đệm địa chỉ và bộ đệm dữ liệu địa chỉ để giao tiếp với CPU. Bộ nhớ và chip I / O được kết nối với các bus này; CPU có thể trao đổi dữ liệu mong muốn với bộ nhớ và chip I / O.

Xe buýt địa chỉ và xe buýt dữ liệu

Bus dữ liệu mang dữ liệu cần lưu trữ. Nó là hai chiều, trong khi bus địa chỉ mang vị trí đến nơi nó cần được lưu trữ và nó là một chiều. Nó được sử dụng để chuyển dữ liệu và địa chỉ I / O thiết bị.

8085 kiến trúc

Chúng tôi đã cố gắng mô tả kiến trúc của năm 8085 với hình ảnh sau:

Hình ảnh sau đây mô tả sơ đồ chân của Bộ vi xử lý 8085 -

Các chân của bộ vi xử lý 8085 có thể được phân thành bảy nhóm -

Địa chỉ xe buýt

A15-A8, nó mang 8 bit bộ nhớ / địa chỉ IO quan trọng nhất.

Xe buýt dữ liệu

AD7-AD0, nó mang địa chỉ 8 bit và bus dữ liệu ít quan trọng nhất.

Các tín hiệu điều khiển và trạng thái

Những tín hiệu này được sử dụng để xác định bản chất của hoạt động. Có 3 tín hiệu điều khiển và 3 tín hiệu trạng thái.

Ba tín hiệu điều khiển là RD, WR & ALE.

RD - Tín hiệu này cho biết IO hoặc thiết bị nhớ đã chọn sẽ được đọc và sẵn sàng chấp nhận dữ liệu có sẵn trên bus dữ liệu.

WR - Tín hiệu này cho biết dữ liệu trên bus dữ liệu sẽ được ghi vào bộ nhớ hoặc vị trí IO đã chọn.

ALE- Là một xung chuyển động tích cực được tạo ra khi một hoạt động mới được bắt đầu bởi bộ vi xử lý. Khi xung tăng cao, nó chỉ ra địa chỉ. Khi xung đi xuống, nó chỉ ra dữ liệu.

Ba tín hiệu trạng thái là IO / M, S0 & S1.

IO / M

Tín hiệu này được sử dụng để phân biệt giữa hoạt động IO và bộ nhớ, tức là khi nó ở mức cao cho biết hoạt động của IO và khi nó ở mức thấp thì nó cho biết hoạt động của bộ nhớ.

S1 & S0

Các tín hiệu này được sử dụng để xác định loại hoạt động hiện tại.

Nguồn cấp

Có 2 tín hiệu cấp nguồn - VCC & VSS. VCC cho biết nguồn điện + 5v và VSS chỉ ra tín hiệu nối đất.

Tín hiệu đồng hồ

Có 3 tín hiệu xung nhịp, tức là X1, X2, CLK OUT.

X1, X2- Một tinh thể (RC, LC N / W) được kết nối tại hai chân này và được sử dụng để đặt tần số của bộ tạo xung nhịp bên trong. Tần số này được chia cho 2.

CLK OUT - Tín hiệu này được sử dụng làm đồng hồ hệ thống cho các thiết bị kết nối với bộ vi xử lý.

Ngắt & tín hiệu bắt đầu từ bên ngoài

Ngắt là các tín hiệu do thiết bị bên ngoài tạo ra để yêu cầu bộ vi xử lý thực hiện một tác vụ. Có 5 tín hiệu ngắt, tức là TRAP, RST 7.5, RST 6.5, RST 5.5 và INTR. Chúng ta sẽ thảo luận chi tiết về ngắt trong phần ngắt.

INTA - Là tín hiệu báo nhận ngắt.

RESET IN - Tín hiệu này được sử dụng để thiết lập lại bộ vi xử lý bằng cách đặt bộ đếm chương trình về không.

RESET OUT - Tín hiệu này được sử dụng để đặt lại tất cả các thiết bị được kết nối khi bộ vi xử lý được đặt lại.

READY- Tín hiệu này cho biết thiết bị đã sẵn sàng để gửi hoặc nhận dữ liệu. Nếu READY ở mức thấp, thì CPU phải đợi READY lên cao.

HOLD - Tín hiệu này chỉ ra rằng một chủ khác đang yêu cầu sử dụng các bus địa chỉ và dữ liệu.

HLDA (HOLD Acknowledge)- Nó chỉ ra rằng CPU đã nhận được yêu cầu HOLD và nó sẽ từ bỏ bus trong chu kỳ xung nhịp tiếp theo. HLDA được đặt thành thấp sau khi tín hiệu HOLD bị loại bỏ.

Tín hiệu I / O nối tiếp

Có 2 tín hiệu nối tiếp, tức là SID và SOD và các tín hiệu này được sử dụng để giao tiếp nối tiếp.

SOD (Đường dữ liệu đầu ra nối tiếp) - SOD đầu ra được đặt / đặt lại theo chỉ định của lệnh SIM.

SID (Dòng dữ liệu đầu vào nối tiếp) - Dữ liệu trên dòng này được tải vào bộ tích lũy bất cứ khi nào một lệnh RIM được thực thi.

Bây giờ chúng ta hãy thảo luận về các chế độ định địa chỉ trong Bộ vi xử lý 8085.

Chế độ địa chỉ trong 8085

Đây là các lệnh được sử dụng để chuyển dữ liệu từ thanh ghi này sang thanh ghi khác, từ bộ nhớ sang thanh ghi, và từ thanh ghi sang bộ nhớ mà không có bất kỳ sự thay đổi nào về nội dung. Các chế độ địa chỉ trong 8085 được phân thành 5 nhóm -

Chế độ giải quyết ngay lập tức

Trong chế độ này, dữ liệu 8/16 bit được chỉ định trong chính lệnh như một trong các toán hạng của nó. For example: MVI K, 20F: nghĩa là 20F được sao chép vào thanh ghi K.

Đăng ký chế độ địa chỉ

Trong chế độ này, dữ liệu được sao chép từ thanh ghi này sang thanh ghi khác. For example: MOV K, B: có nghĩa là dữ liệu trong thanh ghi B được sao chép sang thanh ghi K.

Chế độ địa chỉ trực tiếp

Trong chế độ này, dữ liệu được sao chép trực tiếp từ địa chỉ đã cho vào thanh ghi. For example: LDB 5000K: có nghĩa là dữ liệu ở địa chỉ 5000K được sao chép vào thanh ghi B.

Chế độ địa chỉ gián tiếp

Trong chế độ này, dữ liệu được chuyển từ thanh ghi này sang thanh ghi khác bằng cách sử dụng địa chỉ được chỉ bởi thanh ghi. For example: MOV K, B: có nghĩa là dữ liệu được chuyển từ địa chỉ bộ nhớ được trỏ tới thanh ghi K.

Chế độ địa chỉ ngụ ý

Chế độ này không yêu cầu bất kỳ toán hạng nào; dữ liệu được chỉ định bởi chính opcode.For example: CMP.

Ngắt trong 8085

Ngắt là các tín hiệu do thiết bị bên ngoài tạo ra để yêu cầu bộ vi xử lý thực hiện một tác vụ. Có 5 tín hiệu ngắt, tức là TRAP, RST 7.5, RST 6.5, RST 5.5 và INTR.

Ngắt được phân loại thành các nhóm sau dựa trên tham số của chúng:

Vector interrupt - Trong kiểu ngắt này, bộ xử lý đã biết địa chỉ ngắt. For example: RST7.5, RST6.5, RST5.5, TRAP.

Non-Vector interrupt - Trong kiểu ngắt này, bộ xử lý không biết địa chỉ ngắt do đó địa chỉ ngắt cần được thiết bị gửi ra bên ngoài để thực hiện ngắt. For example: INTR.

Maskable interrupt - Trong kiểu ngắt này, ta có thể vô hiệu hóa ngắt bằng cách ghi một số lệnh vào chương trình. For example: RST7.5, RST6.5, RST5.5.

Non-Maskable interrupt - Trong kiểu ngắt này, chúng ta không thể vô hiệu hóa ngắt bằng cách ghi một số lệnh vào chương trình. For example: BẨY.

Software interrupt- Trong kiểu ngắt này, người lập trình phải thêm các lệnh vào chương trình để thực hiện ngắt. Có 8 phần mềm ngắt trong 8085, tức là RST0, RST1, RST2, RST3, RST4, RST5, RST6 và RST7.

Hardware interrupt - Có 5 chân ngắt trong 8085 được sử dụng làm ngắt phần cứng, tức là TRAP, RST7.5, RST6.5, RST5.5, INTA.

Note- NTA không phải là ngắt, nó được sử dụng bởi bộ vi xử lý để gửi báo nhận. TRAP có mức độ ưu tiên cao nhất, sau đó đến RST7.5, v.v.

Quy trình dịch vụ ngắt (ISR)

Một chương trình nhỏ hoặc một quy trình mà khi thực thi, dịch vụ nguồn ngắt tương ứng được gọi là ISR.

BẨY

Nó là một ngắt không che được, có mức ưu tiên cao nhất trong số tất cả các ngắt. Mặc định, nó được kích hoạt cho đến khi được xác nhận. Trong trường hợp không thành công, nó thực thi dưới dạng ISR và gửi dữ liệu đến bộ nhớ sao lưu. Ngắt này chuyển điều khiển đến vị trí 0024H.

RST7,5

Nó là một ngắt có thể che dấu, có mức ưu tiên cao thứ hai trong số tất cả các ngắt. Khi ngắt này được thực thi, bộ xử lý lưu nội dung của thanh ghi PC vào ngăn xếp và các nhánh tới địa chỉ 003CH.

RST 6,5

Nó là một ngắt có thể che dấu, có mức ưu tiên cao thứ ba trong số tất cả các ngắt. Khi ngắt này được thực thi, bộ xử lý lưu nội dung của thanh ghi PC vào ngăn xếp và các nhánh tới địa chỉ 0034H.

RST 5.5

Nó là một ngắt có thể che giấu. Khi ngắt này được thực thi, bộ xử lý lưu nội dung của thanh ghi PC vào ngăn xếp và các nhánh tới địa chỉ 002CH.

INTR

Nó là một ngắt có thể che dấu, có mức ưu tiên thấp nhất trong số tất cả các ngắt. Nó có thể bị vô hiệu hóa bằng cách đặt lại bộ vi xử lý.

Khi nào INTR signal goes high, các sự kiện sau có thể xảy ra:

Bộ vi xử lý kiểm tra trạng thái của tín hiệu INTR trong quá trình thực hiện từng lệnh.

Khi tín hiệu INTR cao, bộ vi xử lý hoàn thành lệnh hiện tại của nó và gửi tín hiệu xác nhận ngắt hoạt động ở mức thấp.

Khi nhận được lệnh, bộ vi xử lý sẽ lưu địa chỉ của lệnh tiếp theo trên ngăn xếp và thực hiện lệnh đã nhận.

Chúng ta hãy cùng xem lập trình của Bộ vi xử lý 8085.

Bộ lệnh là mã lệnh để thực hiện một số tác vụ. Nó được phân thành năm loại.

| Không. | Hướng dẫn & Mô tả |

|---|---|

| 1 | Hướng dẫn kiểm soát Sau đây là bảng hiển thị danh sách các lệnh Control với ý nghĩa của chúng. |

| 2 | Hướng dẫn logic Sau đây là bảng hiển thị danh sách các hướng dẫn logic với ý nghĩa của chúng. |

| 3 | Hướng dẫn phân nhánh Sau đây là bảng hiển thị danh sách các hướng dẫn Phân nhánh với ý nghĩa của chúng. |

| 4 | Hướng dẫn số học Sau đây là bảng hiển thị danh sách các hướng dẫn Số học với ý nghĩa của chúng. |

| 5 | Hướng dẫn chuyển dữ liệu Sau đây là bảng hiển thị danh sách các hướng dẫn Truyền dữ liệu với ý nghĩa của chúng. |

8085 - Chương trình demo

Bây giờ, chúng ta hãy xem một số bản trình diễn chương trình bằng cách sử dụng các hướng dẫn ở trên -

Thêm hai số 8 bit

Viết chương trình thêm dữ liệu vào vị trí bộ nhớ 3005H & 3006H và lưu kết quả ở vị trí bộ nhớ 3007H.

Problem demo -

(3005H) = 14H

(3006H) = 89HResult -

14H + 89H = 9DH

Mã chương trình có thể được viết như thế này -

LXI H 3005H : "HL points 3005H"

MOV A, M : "Getting first operand"

INX H : "HL points 3006H"

ADD M : "Add second operand"

INX H : "HL points 3007H"

MOV M, A : "Store result at 3007H"

HLT : "Exit program"Trao đổi vị trí bộ nhớ

Viết chương trình trao đổi dữ liệu ở vị trí bộ nhớ 5000M & 6000M.

LDA 5000M : "Getting the contents at5000M location into accumulator"

MOV B, A : "Save the contents into B register"

LDA 6000M : "Getting the contents at 6000M location into accumulator"

STA 5000M : "Store the contents of accumulator at address 5000M"

MOV A, B : "Get the saved contents back into A register"

STA 6000M : "Store the contents of accumulator at address 6000M"Sắp xếp các số theo thứ tự tăng dần

Viết chương trình sắp xếp 10 số đầu tiên từ ô nhớ địa chỉ 3000H theo thứ tự tăng dần.

MVI B, 09 :"Initialize counter"

START :"LXI H, 3000H: Initialize memory pointer"

MVI C, 09H :"Initialize counter 2"

BACK: MOV A, M :"Get the number"

INX H :"Increment memory pointer"

CMP M :"Compare number with next number"

JC SKIP :"If less, don’t interchange"

JZ SKIP :"If equal, don’t interchange"

MOV D, M

MOV M, A

DCX H

MOV M, D

INX H :"Interchange two numbers"

SKIP:DCR C :"Decrement counter 2"

JNZ BACK :"If not zero, repeat"

DCR B :"Decrement counter 1"

JNZ START

HLT :"Terminate program execution"Bộ vi xử lý 8086 là phiên bản nâng cao của bộ vi xử lý 8085Microprocessor được Intel thiết kế vào năm 1976. Đây là bộ vi xử lý 16 bit có 20 đường địa chỉ và 16 đường dữ liệu cung cấp dung lượng lưu trữ lên đến 1MB. Nó bao gồm tập lệnh mạnh mẽ, cung cấp các phép toán như nhân và chia một cách dễ dàng.

Nó hỗ trợ hai chế độ hoạt động, tức là chế độ Tối đa và chế độ Tối thiểu. Chế độ tối đa phù hợp với hệ thống có nhiều bộ xử lý và chế độ Tối thiểu phù hợp với hệ thống có một bộ xử lý duy nhất.

Các tính năng của 8086

Các tính năng nổi bật nhất của bộ vi xử lý 8086 như sau:

Nó có một hàng đợi lệnh, có khả năng lưu trữ sáu byte lệnh từ bộ nhớ, giúp xử lý nhanh hơn.

Đây là bộ xử lý 16 bit đầu tiên có ALU 16 bit, thanh ghi 16 bit, bus dữ liệu bên trong và bus dữ liệu ngoài 16 bit giúp xử lý nhanh hơn.

Nó có sẵn trong 3 phiên bản dựa trên tần suất hoạt động -

8086 → 5MHz

8086-2 → 8MHz

(c) 8086-1 → 10 MHz

Nó sử dụng hai giai đoạn pipelining, tức là Giai đoạn Tìm nạp và Giai đoạn Thực thi, giúp cải thiện hiệu suất.

Giai đoạn tìm nạp có thể tìm nạp trước tối đa 6 byte hướng dẫn và lưu trữ chúng trong hàng đợi.

Giai đoạn thực thi thực hiện các hướng dẫn này.

Nó có 256 ngắt vectơ.

Nó bao gồm 29.000 bóng bán dẫn.

So sánh giữa Bộ vi xử lý 8085 & 8086

Size - 8085 là bộ vi xử lý 8 bit, trong khi 8086 là bộ vi xử lý 16 bit.

Address Bus - 8085 có bus địa chỉ 16 bit trong khi 8086 có bus địa chỉ 20 bit.

Memory - 8085 có thể truy cập lên đến 64Kb, trong khi 8086 có thể truy cập tới 1 Mb bộ nhớ.

Instruction - 8085 không có hàng đợi lệnh, trong khi 8086 có hàng đợi lệnh.

Pipelining - 8085 không hỗ trợ kiến trúc pipelined trong khi 8086 hỗ trợ kiến trúc pipelined.

I/O - 8085 có thể giải quyết 2 ^ 8 = 256 I / O, trong khi 8086 có thể truy cập 2 ^ 16 = 65.536 I / O's.

Cost - Chi phí của 8085 thấp trong khi 8086 cao.

Kiến trúc của 8086

Sơ đồ sau mô tả kiến trúc của Bộ vi xử lý 8086 -

Bộ vi xử lý 8086 được chia thành hai đơn vị chức năng, tức là EU (Đơn vị thực hiện) và BIU (Đơn vị Giao diện Bus).

EU (Đơn vị thực thi)

Đơn vị thực thi cung cấp hướng dẫn cho BIU nêu rõ nơi lấy dữ liệu và sau đó giải mã và thực hiện các hướng dẫn đó. Chức năng của nó là điều khiển các hoạt động trên dữ liệu bằng cách sử dụng bộ giải mã lệnh & ALU. EU không có kết nối trực tiếp với các bus hệ thống như trong hình trên, nó thực hiện các hoạt động qua dữ liệu thông qua BIU.

Bây giờ chúng ta hãy thảo luận về các bộ phận chức năng của bộ vi xử lý 8086.

ALU

Nó xử lý tất cả các phép toán số học và logic, như các phép toán +, -, ×, /, OR, AND, NOT.

Cờ Đăng ký

Nó là một thanh ghi 16-bit hoạt động giống như một flip-flop, tức là nó thay đổi trạng thái của nó theo kết quả được lưu trữ trong bộ tích lũy. Nó có 9 lá cờ và chúng được chia thành 2 nhóm - Cờ điều kiện và Cờ điều khiển.

Cờ có điều kiện

Nó đại diện cho kết quả của lệnh số học hoặc logic cuối cùng được thực hiện. Sau đây là danh sách các cờ điều kiện:

Carry flag - Cờ này chỉ ra điều kiện tràn đối với các phép toán số học.

Auxiliary flag- Khi một thao tác được thực hiện tại ALU, nó dẫn đến chuyển hướng từ ngòi xuống dưới (tức là D0 - D3) đến ngòi trên (tức là D4 - D7), thì cờ này được đặt, tức là chuyển do bit D3 cho D4 là Cờ AF. Bộ xử lý sử dụng cờ này để thực hiện chuyển đổi nhị phân sang BCD.

Parity flag- Cờ này được sử dụng để chỉ ra tính chẵn lẻ của kết quả, tức là khi 8 bit bậc dưới của kết quả chứa số chẵn là 1 thì Cờ chẵn lẻ được đặt. Đối với số lẻ của 1, Cờ chẵn lẻ được đặt lại.

Zero flag - Cờ này được đặt thành 1 khi kết quả của phép toán số học hoặc logic bằng 0, nếu không nó được đặt thành 0.

Sign flag - Cờ này giữ dấu hiệu của kết quả, tức là khi kết quả của phép toán là âm, thì cờ dấu được đặt thành 1 khác được đặt thành 0.

Overflow flag - Cờ này thể hiện kết quả khi vượt quá dung lượng hệ thống.

Cờ kiểm soát

Cờ điều khiển kiểm soát các hoạt động của đơn vị thực thi. Sau đây là danh sách các cờ điều khiển:

Trap flag- Nó được sử dụng để điều khiển từng bước và cho phép người dùng thực hiện một lệnh tại một thời điểm để gỡ lỗi. Nếu nó được đặt, thì chương trình có thể chạy ở chế độ một bước.

Interrupt flag- Là cờ cho phép / vô hiệu hóa ngắt, tức là dùng để cho phép / cấm ngắt chương trình. Nó được đặt thành 1 cho điều kiện kích hoạt ngắt và đặt thành 0 cho điều kiện ngắt ngắt.

Direction flag- Nó được sử dụng trong hoạt động chuỗi. Như tên cho thấy khi nó được đặt thì các byte chuỗi được truy cập từ địa chỉ bộ nhớ cao hơn đến địa chỉ bộ nhớ thấp hơn và ngược lại.

Đăng ký mục đích chung

Có 8 thanh ghi mục đích chung, tức là, AH, AL, BH, BL, CH, CL, DH và DL. Các thanh ghi này có thể được sử dụng riêng lẻ để lưu trữ dữ liệu 8 bit và có thể được sử dụng theo cặp để lưu trữ dữ liệu 16 bit. Các cặp thanh ghi hợp lệ là AH và AL, BH và BL, CH và CL, DH và DL. Nó được gọi lần lượt là AX, BX, CX và DX.

AX register- Nó còn được gọi là thanh ghi tích lũy. Nó được sử dụng để lưu trữ các toán hạng cho các phép toán số học.

BX register- Nó được sử dụng như một thanh ghi cơ sở. Nó được sử dụng để lưu trữ địa chỉ cơ sở bắt đầu của vùng bộ nhớ trong phân đoạn dữ liệu.

CX register- Nó được gọi là bộ đếm. Nó được sử dụng trong lệnh lặp để lưu trữ bộ đếm vòng lặp.

DX register - Thanh ghi này được sử dụng để giữ địa chỉ cổng I / O cho lệnh I / O.

Thanh ghi con trỏ ngăn xếp

Nó là một thanh ghi 16 bit, giữ địa chỉ từ đầu đoạn đến vị trí bộ nhớ, nơi một từ được lưu trữ gần đây nhất trên ngăn xếp.

BIU (Đơn vị giao diện xe buýt)

BIU đảm nhận tất cả dữ liệu và chuyển địa chỉ trên các xe buýt cho EU như gửi địa chỉ, tìm nạp các lệnh từ bộ nhớ, đọc dữ liệu từ các cổng và bộ nhớ cũng như ghi dữ liệu vào các cổng và bộ nhớ. EU không có kết nối hướng với Xe buýt Hệ thống nên điều này có thể xảy ra với BIU. EU và BIU được kết nối với Bus nội bộ.

Nó có các phần chức năng sau:

Instruction queue- BIU chứa hàng đợi lệnh. BIU nhận tối đa 6 byte lệnh tiếp theo và lưu trữ chúng trong hàng đợi lệnh. Khi EU thực hiện các lệnh và sẵn sàng cho lệnh tiếp theo của nó, thì nó chỉ cần đọc lệnh từ hàng đợi lệnh này, dẫn đến tốc độ thực thi tăng lên.

Tìm nạp lệnh tiếp theo trong khi lệnh hiện tại thực thi được gọi pipelining.

Segment register- BIU có 4 bus phân đoạn, tức là CS, DS, SS & ES. Nó giữ các địa chỉ của lệnh và dữ liệu trong bộ nhớ, được bộ xử lý sử dụng để truy cập các vị trí bộ nhớ. Nó cũng chứa 1 IP thanh ghi con trỏ, giữ địa chỉ của lệnh tiếp theo được EU thực thi.

CS- Nó là viết tắt của Code Segment. Nó được sử dụng để định địa chỉ một vị trí bộ nhớ trong đoạn mã của bộ nhớ, nơi chương trình thực thi được lưu trữ.

DS- Nó là viết tắt của Data Segment. Nó bao gồm dữ liệu được chương trình sử dụng và được truy cập trong phân đoạn dữ liệu bằng một địa chỉ offset hoặc nội dung của thanh ghi khác có địa chỉ offset.

SS- Nó là viết tắt của Stack Segment. Nó xử lý bộ nhớ để lưu trữ dữ liệu và địa chỉ trong quá trình thực thi.

ES- Nó là viết tắt của Extra Segment. ES là phân đoạn dữ liệu bổ sung, được sử dụng bởi chuỗi để chứa dữ liệu đích bổ sung.

Instruction pointer - Là một thanh ghi 16 bit dùng để giữ địa chỉ của lệnh tiếp theo sẽ được thực hiện.

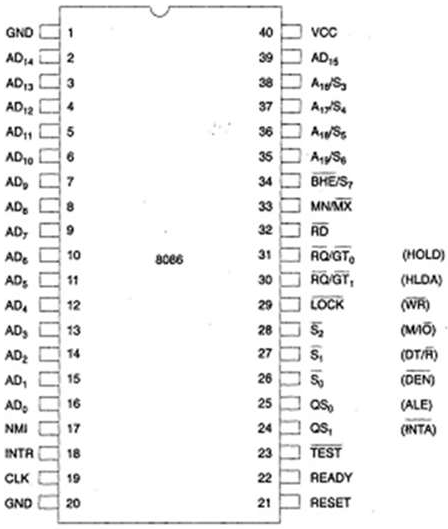

8086 là bộ vi xử lý 16 bit đầu tiên có sẵn trong chip DIP 40 chân (Gói nội tuyến kép). Bây giờ chúng ta hãy thảo luận chi tiết về cấu hình chân của Bộ vi xử lý 8086.

Sơ đồ chân 8086

Đây là sơ đồ chân của bộ vi xử lý 8086 -

Bây giờ chúng ta hãy thảo luận chi tiết về các tín hiệu -

Power supply and frequency signals

Nó sử dụng nguồn điện 5V DC ở chân V CC 40 và sử dụng đất ở chân V SS 1 và 20 cho hoạt động của nó.

Clock signal

Tín hiệu đồng hồ được cung cấp thông qua Pin-19. Nó cung cấp thời gian để bộ xử lý hoạt động. Tần số của nó là khác nhau đối với các phiên bản khác nhau, tức là 5MHz, 8MHz và 10MHz.

Address/data bus

AD0-AD15. Đây là 16 bus địa chỉ / dữ liệu. AD0-AD7 mang dữ liệu byte bậc thấp và AD8AD15 mang dữ liệu byte bậc cao. Trong chu kỳ xung nhịp đầu tiên, nó mang địa chỉ 16 bit và sau đó nó mang dữ liệu 16 bit.

Address/status bus

A16-A19 / S3-S6. Đây là 4 xe buýt địa chỉ / trạng thái. Trong chu kỳ xung nhịp đầu tiên, nó mang địa chỉ 4 bit và sau đó nó mang các tín hiệu trạng thái.

S7/BHE

BHE là viết tắt của Bus High Enable. Nó có sẵn ở chân 34 và được sử dụng để chỉ ra việc truyền dữ liệu bằng bus dữ liệu D8-D15. Tín hiệu này ở mức thấp trong chu kỳ đồng hồ đầu tiên, sau đó nó hoạt động.

Read($\overline{RD}$)

Nó có sẵn ở chân 32 và được sử dụng để đọc tín hiệu cho hoạt động Đọc.

Ready

Nó có sẵn ở chân 22. Đây là tín hiệu báo nhận từ các thiết bị I / O mà dữ liệu được truyền. Đó là một tín hiệu cao đang hoạt động. Khi nó ở mức cao, nó chỉ ra rằng thiết bị đã sẵn sàng để truyền dữ liệu. Khi nó ở mức thấp, nó cho biết trạng thái chờ.

RESET

Nó có sẵn ở chân 21 và được sử dụng để khởi động lại quá trình thực thi. Nó khiến bộ xử lý chấm dứt ngay hoạt động hiện tại của nó. Tín hiệu này hoạt động ở mức cao trong 4 chu kỳ xung nhịp đầu tiên để ĐẶT LẠI bộ vi xử lý.

INTR

Nó có sẵn ở chân 18. Đây là một tín hiệu yêu cầu ngắt, được lấy mẫu trong chu kỳ xung nhịp cuối cùng của mỗi lệnh để xác định xem bộ xử lý có coi đây là một ngắt hay không.

NMI

Nó là viết tắt của ngắt không che được và có sẵn ở chân 17. Nó là một đầu vào được kích hoạt cạnh, gây ra một yêu cầu ngắt tới bộ vi xử lý.

$\overline{TEST}$

Tín hiệu này giống như trạng thái chờ và có sẵn ở chân 23. Khi tín hiệu này ở mức cao, thì bộ xử lý phải đợi trạng thái IDLE, nếu không thì quá trình thực thi tiếp tục.

MN/$\overline{MX}$

Nó là viết tắt của Minimum / Maximum và có sẵn ở chân 33. Nó chỉ ra chế độ hoạt động của bộ xử lý; khi ở mức cao, nó hoạt động ở chế độ tối thiểu và đảo chiều.

INTA

Nó là một tín hiệu báo nhận ngắt và id có sẵn tại chân 24. Khi bộ vi xử lý nhận được tín hiệu này, nó sẽ báo nhận ngắt.

ALE

Nó là viết tắt của chốt kích hoạt địa chỉ và có sẵn ở chân 25. Một xung tích cực được tạo ra mỗi khi bộ xử lý bắt đầu bất kỳ hoạt động nào. Tín hiệu này cho biết sự sẵn có của một địa chỉ hợp lệ trên các đường địa chỉ / dữ liệu.

DEN

Nó là viết tắt của Data Enable và có sẵn ở chân 26. Nó được sử dụng để kích hoạt Bộ thu phát 8286. Bộ thu phát là một thiết bị dùng để tách dữ liệu khỏi bus địa chỉ / dữ liệu.

DT/R

Nó là viết tắt của tín hiệu Truyền / Nhận dữ liệu và có sẵn ở chân 27. Nó quyết định hướng của luồng dữ liệu qua bộ thu phát. Khi mức cao, dữ liệu được truyền ra ngoài và ngược lại.

M/IO

Tín hiệu này được sử dụng để phân biệt giữa bộ nhớ và các hoạt động I / O. Khi ở mức cao, nó cho biết hoạt động I / O và khi ở mức thấp cho biết hoạt động của bộ nhớ. Nó có sẵn tại pin 28.

WR

Nó là viết tắt của tín hiệu ghi và có sẵn ở chân 29. Nó được sử dụng để ghi dữ liệu vào bộ nhớ hoặc thiết bị xuất tùy thuộc vào trạng thái của tín hiệu M / IO.

HLDA

Nó là viết tắt của tín hiệu Hold Acknowledgement và có sẵn ở chân 30. Tín hiệu này ghi nhận tín hiệu HOLD.

HOLD

Tín hiệu này cho bộ xử lý biết rằng các thiết bị bên ngoài đang yêu cầu truy cập các bus địa chỉ / dữ liệu. Nó có sẵn tại pin 31.

QS1 and QS0

Đây là các tín hiệu trạng thái hàng đợi và có sẵn ở chân 24 và 25. Các tín hiệu này cung cấp trạng thái của hàng đợi lệnh. Điều kiện của chúng được thể hiện trong bảng sau:

| QS 0 | QS 1 | Trạng thái |

|---|---|---|

| 0 | 0 | Không hoạt động |

| 0 | 1 | Byte opcode đầu tiên từ hàng đợi |

| 1 | 0 | Dọn sạch hàng đợi |

| 1 | 1 | Byte tiếp theo từ hàng đợi |

S0, S1, S2

Đây là các tín hiệu trạng thái cung cấp trạng thái hoạt động, được sử dụng bởi Bộ điều khiển Bus 8288 để tạo ra các tín hiệu điều khiển bộ nhớ & I / O. Chúng có sẵn tại pin 26, 27 và 28. Sau đây là bảng hiển thị trạng thái của chúng -

| S 2 | S 1 | S 0 | Trạng thái |

|---|---|---|---|

| 0 | 0 | 0 | Xác nhận ngắt |

| 0 | 0 | 1 | I / O Đọc |

| 0 | 1 | 0 | I / O Viết |

| 0 | 1 | 1 | Tạm dừng lại |

| 1 | 0 | 0 | Tìm nạp opcode |

| 1 | 0 | 1 | Đọc bộ nhớ |

| 1 | 1 | 0 | Ghi nhớ |

| 1 | 1 | 1 | Bị động |

LOCK

Khi tín hiệu này hoạt động, nó chỉ ra cho các bộ xử lý khác không yêu cầu CPU rời khỏi bus hệ thống. Nó được kích hoạt bằng cách sử dụng tiền tố LOCK trên bất kỳ hướng dẫn nào và có sẵn tại pin 29.

RQ/GT1 and RQ/GT0

Đây là các tín hiệu Request / Grant được các bộ xử lý khác sử dụng yêu cầu CPU giải phóng bus hệ thống. Khi tín hiệu được nhận bởi CPU, sau đó nó sẽ gửi xác nhận. RQ / GT 0 có mức độ ưu tiên cao hơn RQ / GT 1 .

Bộ vi xử lý 8086 hỗ trợ 8 loại lệnh -

- Hướng dẫn chuyển dữ liệu

- Hướng dẫn số học

- Hướng dẫn thao tác bit

- Hướng dẫn chuỗi

- Hướng dẫn chuyển thực thi chương trình (Hướng dẫn nhánh & vòng lặp)

- Hướng dẫn kiểm soát bộ xử lý

- Hướng dẫn kiểm soát lặp lại

- Hướng dẫn ngắt

Bây giờ chúng ta hãy thảo luận chi tiết về các bộ hướng dẫn này.

Hướng dẫn chuyển dữ liệu

Các hướng dẫn này được sử dụng để chuyển dữ liệu từ toán hạng nguồn sang toán hạng đích. Sau đây là danh sách các hướng dẫn trong nhóm này:

Hướng dẫn chuyển một từ

MOV - Được sử dụng để sao chép byte hoặc từ từ nguồn được cung cấp đến đích được cung cấp.

PPUSH - Được sử dụng để đặt một từ ở trên cùng của ngăn xếp.

POP - Được sử dụng để lấy một từ từ trên cùng của ngăn xếp đến vị trí được cung cấp.

PUSHA - Dùng để đưa tất cả các thanh ghi vào ngăn xếp.

POPA - Dùng để lấy từ từ ngăn xếp đến tất cả các thanh ghi.

XCHG - Được sử dụng để trao đổi dữ liệu từ hai vị trí.

XLAT - Dùng để dịch một byte trong AL bằng bảng trong bộ nhớ.

Hướng dẫn chuyển cổng đầu vào và đầu ra

IN - Được sử dụng để đọc một byte hoặc từ từ cổng được cung cấp đến bộ tích lũy.

OUT - Được sử dụng để gửi một byte hoặc một từ từ bộ tích lũy đến cổng được cung cấp.

Hướng dẫn chuyển địa chỉ

LEA - Dùng để nạp địa chỉ của toán hạng vào thanh ghi được cung cấp.

LDS - Được sử dụng để tải thanh ghi DS và thanh ghi được cung cấp khác từ bộ nhớ

LES - Dùng để nạp thanh ghi ES và thanh ghi được cung cấp khác từ bộ nhớ.

Hướng dẫn chuyển thanh ghi cờ

LAHF - Dùng để nạp AH với byte thấp của thanh ghi cờ.

SAHF - Dùng để lưu thanh ghi AH vào byte thấp của thanh ghi cờ.

PUSHF - Dùng để sao chép thanh ghi cờ ở đầu ngăn xếp.

POPF - Được sử dụng để sao chép một từ ở trên cùng của ngăn xếp vào thanh ghi cờ.

Hướng dẫn số học

Các hướng dẫn này được sử dụng để thực hiện các phép toán số học như cộng, trừ, nhân, chia, v.v.

Sau đây là danh sách các hướng dẫn trong nhóm này:

Hướng dẫn thực hiện phép cộng

ADD - Được sử dụng để thêm byte đã cung cấp thành byte / từ thành từng từ.

ADC - Dùng để thêm vào mang theo.

INC - Được sử dụng để tăng byte / từ được cung cấp lên 1.

AAA - Dùng để điều chỉnh ASCII sau khi thêm vào.

DAA - Dùng để điều chỉnh số thập phân sau phép tính cộng / trừ.

Hướng dẫn thực hiện phép trừ

SUB - Dùng để trừ byte khỏi byte / từ khỏi word.

SBB - Dùng để thực hiện phép trừ có mượn.

DEC - Được sử dụng để giảm 1 byte / từ đã cung cấp.

NPG - Được sử dụng để phủ định từng bit của byte / từ được cung cấp và thêm 1/2 phần bổ sung.

CMP - Dùng để so sánh 2 byte / từ được cung cấp.

AAS - Dùng để điều chỉnh mã ASCII sau khi trừ.

DAS - Dùng để điều chỉnh số thập phân sau phép trừ.

Hướng dẫn thực hiện phép nhân

MUL - Dùng để nhân byte không dấu với byte / từng từ.

IMUL - Dùng để nhân byte có dấu với byte / từng từ.

AAM - Dùng để điều chỉnh mã ASCII sau khi nhân.

Hướng dẫn thực hiện phép chia

DIV - Dùng để chia từ không dấu theo từng byte hoặc từ kép không dấu theo từng từ.

IDIV - Dùng để chia từ có dấu theo từng byte hoặc từng từ có dấu.

AAD - Dùng để điều chỉnh các mã ASCII sau khi phân chia.

CBW - Được sử dụng để điền vào byte trên của từ với các bản sao của bit dấu của byte dưới.

CWD - Dùng để điền từ trên của từ kép với bit dấu của từ dưới.

Hướng dẫn thao tác bit

Các lệnh này được sử dụng để thực hiện các hoạt động có liên quan đến các bit dữ liệu, tức là các hoạt động như logic, shift, v.v.

Sau đây là danh sách các hướng dẫn trong nhóm này:

Hướng dẫn thực hiện thao tác logic

NOT - Dùng để đảo từng bit của byte hoặc từ.

AND - Được sử dụng để thêm từng bit trong một byte / từ với bit tương ứng trong byte / từ khác.

OR - Dùng để nhân từng bit trong một byte / từ với bit tương ứng trong byte / từ khác.

XOR - Được sử dụng để thực hiện phép toán Exclusive-OR trên mỗi bit trong byte / từ với bit tương ứng trong byte / từ khác.

TEST - Dùng để thêm toán hạng để cập nhật cờ, không ảnh hưởng đến toán hạng.

Hướng dẫn thực hiện các thao tác trong ca

SHL/SAL - Được sử dụng để dịch chuyển các bit của một byte / từ sang trái và đặt số không (S) trong LSB.

SHR - Được sử dụng để dịch chuyển các bit của một byte / từ về phía bên phải và đặt số không (S) trong MSB.

SAR - Được sử dụng để chuyển các bit của một byte / từ về phía bên phải và sao chép MSB cũ vào MSB mới.

Hướng dẫn thực hiện các thao tác xoay

ROL - Được sử dụng để xoay các bit của byte / từ về phía bên trái, tức là MSB sang LSB và để Carry Flag [CF].

ROR - Được sử dụng để xoay các bit của byte / từ về phía bên phải, tức là LSB sang MSB và để Carry Flag [CF].

RCR - Được sử dụng để xoay các bit byte / từ về phía bên phải, tức là LSB sang CF và CF sang MSB.

RCL - Dùng để xoay các bit byte / word về phía trái, tức là MSB sang CF và CF sang LSB.

Hướng dẫn chuỗi

Chuỗi là một nhóm các byte / từ và bộ nhớ của chúng luôn được cấp phát theo thứ tự tuần tự.

Sau đây là danh sách các hướng dẫn trong nhóm này:

REP - Được sử dụng để lặp lại lệnh đã cho cho đến khi CX ≠ 0.

REPE/REPZ - Được sử dụng để lặp lại lệnh đã cho cho đến khi CX = 0 hoặc cờ không ZF = 1.

REPNE/REPNZ - Được sử dụng để lặp lại lệnh đã cho cho đến khi CX = 0 hoặc cờ không ZF = 1.

MOVS/MOVSB/MOVSW - Dùng để di chuyển byte / từ từ chuỗi này sang chuỗi khác.

COMS/COMPSB/COMPSW - Dùng để so sánh hai chuỗi byte / từ.

INS/INSB/INSW - Được sử dụng như một chuỗi / byte / từ đầu vào từ cổng I / O đến vị trí bộ nhớ được cung cấp.

OUTS/OUTSB/OUTSW - Được sử dụng như một chuỗi / byte / từ đầu ra từ vị trí bộ nhớ được cung cấp đến cổng I / O.

SCAS/SCASB/SCASW - Được sử dụng để quét một chuỗi và so sánh byte của nó với một byte trong AL hoặc từ chuỗi với một từ trong AX.

LODS/LODSB/LODSW - Dùng để lưu chuỗi byte thành AL hoặc chuỗi từ thành AX.

Hướng dẫn chuyển giao thực thi chương trình (Hướng dẫn nhánh và vòng lặp)

Các lệnh này được sử dụng để chuyển / rẽ nhánh các lệnh trong quá trình thực thi. Nó bao gồm các hướng dẫn sau:

Hướng dẫn chuyển lệnh trong khi thực hiện mà không có bất kỳ điều kiện nào -

CALL - Được sử dụng để gọi một thủ tục và lưu địa chỉ trả về của chúng vào ngăn xếp.

RET - Dùng để quay lại từ thủ tục về chương trình chính.

JMP - Được sử dụng để chuyển đến địa chỉ được cung cấp để chuyển sang hướng dẫn tiếp theo.

Hướng dẫn chuyển lệnh trong khi thực hiện với một số điều kiện -

JA/JNBE - Dùng để nhảy nếu trên / không dưới / lệnh bằng thỏa mãn.

JAE/JNB - Dùng để nhảy nếu lệnh trên / không dưới thỏa mãn.

JBE/JNA - Dùng để nhảy nếu lệnh dưới / bằng / không trên thỏa mãn.

JC - Dùng để nhảy nếu mang cờ CF = 1

JE/JZ - Dùng để nhảy nếu cờ bằng / không ZF = 1

JG/JNLE - Được sử dụng để nhảy nếu lệnh lớn hơn / không nhỏ hơn / bằng thỏa mãn.

JGE/JNL - Được sử dụng để nhảy nếu lớn hơn / bằng / không nhỏ hơn lệnh thỏa mãn.

JL/JNGE - Được sử dụng để nhảy nếu lệnh nhỏ hơn / không lớn hơn / bằng thỏa mãn.

JLE/JNG - Dùng để nhảy nếu nhỏ hơn / bằng / nếu không lớn hơn lệnh thỏa mãn.

JNC - Dùng để nhảy nếu không có cờ mang (CF = 0)

JNE/JNZ - Dùng để nhảy nếu không cờ bằng / không ZF = 0

JNO - Dùng để nhảy nếu không có cờ tràn OF = 0

JNP/JPO - Dùng để nhảy nếu không chẵn lẻ / chẵn lẻ PF = 0

JNS - Dùng để nhảy nếu không ký SF = 0

JO - Dùng để nhảy nếu cờ tràn OF = 1

JP/JPE - Dùng để nhảy nếu parity / parity chẵn PF = 1

JS - Dùng để nhảy nếu cờ ký SF = 1

Hướng dẫn kiểm soát bộ xử lý

Các hướng dẫn này được sử dụng để điều khiển hành động của bộ xử lý bằng cách cài đặt / đặt lại các giá trị cờ.

Sau đây là các hướng dẫn trong nhóm này -

STC - Được sử dụng để đặt CF mang cờ thành 1

CLC - Dùng để xóa / đặt lại cờ mang CF về 0

CMC - Dùng để đặt bổ sung ở trạng thái mang cờ CF.

STD - Dùng để đặt cờ hướng DF thành 1

CLD - Dùng để xóa / đặt lại cờ hướng DF về 0

STI - Dùng để đặt cờ cho phép ngắt thành 1, tức là cho phép đầu vào INTR.

CLI - Dùng để xóa cờ cho phép ngắt về 0, tức là tắt đầu vào INTR.

Hướng dẫn kiểm soát lặp lại

Các lệnh này được sử dụng để thực hiện các lệnh đã cho với số lần. Sau đây là danh sách các hướng dẫn trong nhóm này:

LOOP - Dùng để lặp một nhóm lệnh cho đến khi thỏa mãn điều kiện, tức là CX = 0

LOOPE/LOOPZ - Dùng để lặp một nhóm lệnh cho đến khi nó thỏa mãn ZF = 1 & CX = 0

LOOPNE/LOOPNZ - Được sử dụng để lặp một nhóm lệnh cho đến khi nó thỏa mãn ZF = 0 & CX = 0

JCXZ - Được sử dụng để chuyển đến địa chỉ đã cung cấp nếu CX = 0

Hướng dẫn ngắt

Các lệnh này được sử dụng để gọi ngắt trong quá trình thực thi chương trình.

INT - Dùng để ngắt chương trình trong quá trình thực thi và gọi dịch vụ được chỉ định.

INTO - Dùng để ngắt chương trình trong quá trình thực thi nếu OF = 1

IRET - Được sử dụng để trở lại từ dịch vụ ngắt về chương trình chính

Interruptlà phương pháp tạo điểm dừng tạm thời trong quá trình thực hiện chương trình và cho phép các thiết bị ngoại vi truy cập vào bộ vi xử lý. Bộ vi xử lý phản hồi lại ngắt đó bằngISR (Quy trình dịch vụ ngắt), là một chương trình ngắn để hướng dẫn bộ vi xử lý cách xử lý ngắt.

Hình ảnh sau đây cho thấy các loại ngắt mà chúng ta có trong bộ vi xử lý 8086 -

Ngắt phần cứng

Ngắt phần cứng là do bất kỳ thiết bị ngoại vi nào gây ra bằng cách gửi tín hiệu qua một chân được chỉ định tới bộ vi xử lý.

8086 có hai chân ngắt phần cứng, tức là NMI và INTR. NMI là ngắt không che được và INTR là ngắt có thể che có mức ưu tiên thấp hơn. Một chân ngắt khác được liên kết với INTA được gọi là xác nhận ngắt.

NMI

Nó là một chân ngắt không che được (NMI) có mức ưu tiên cao hơn chân yêu cầu ngắt có thể che được (INTR) và nó thuộc loại ngắt 2.

Khi ngắt này được kích hoạt, các hành động này sẽ diễn ra -

Hoàn thành hướng dẫn hiện tại đang được thực hiện.

Đẩy các giá trị của thanh ghi Cờ vào ngăn xếp.

Đẩy giá trị CS (đoạn mã) và giá trị IP (con trỏ lệnh) của địa chỉ trả về vào ngăn xếp.

IP được tải từ nội dung của vị trí từ 00008H.

CS được tải từ nội dung của vị trí từ tiếp theo 0000AH.

Cờ ngắt và cờ bẫy được đặt lại về 0.

INTR

INTR là ngắt có thể che dấu vì bộ vi xử lý sẽ bị ngắt chỉ khi ngắt được kích hoạt bằng cách sử dụng lệnh cờ ngắt đã đặt. Nó không nên được kích hoạt bằng cách sử dụng hướng dẫn Cờ ngắt rõ ràng.

Ngắt INTR được kích hoạt bởi một cổng I / O. Nếu ngắt được bật và NMI bị vô hiệu hóa, thì trước tiên bộ vi xử lý sẽ hoàn thành việc thực thi hiện tại và gửi '0' trên chân INTA hai lần. Số '0' đầu tiên có nghĩa là INTA thông báo cho thiết bị bên ngoài chuẩn bị sẵn sàng và trong '0' thứ hai, bộ vi xử lý nhận 8 bit, chẳng hạn như X, từ bộ điều khiển ngắt có thể lập trình.

Các hành động này được thực hiện bởi bộ vi xử lý -

Đầu tiên hoàn thành hướng dẫn hiện tại.

Kích hoạt đầu ra INTA và nhận kiểu ngắt, giả sử X.

Giá trị thanh ghi cờ, giá trị CS của địa chỉ trả về và giá trị IP của địa chỉ trả về được đẩy vào ngăn xếp.

Giá trị IP được tải từ nội dung của vị trí từ X × 4

CS được tải từ nội dung của vị trí từ tiếp theo.

Cờ ngắt và cờ bẫy được đặt lại thành 0

Ngắt phần mềm

Một số hướng dẫn được chèn ở vị trí mong muốn vào chương trình để tạo ngắt. Các lệnh ngắt này có thể được sử dụng để kiểm tra hoạt động của các bộ xử lý ngắt khác nhau. Nó bao gồm -

INT- Lệnh ngắt với số kiểu

Đây là lệnh 2 byte. Byte đầu tiên cung cấp mã op và byte thứ hai cung cấp số kiểu ngắt. Có 256 kiểu ngắt trong nhóm này.

Quá trình thực hiện của nó bao gồm các bước sau:

Giá trị thanh ghi cờ được đẩy vào ngăn xếp.

Giá trị CS của địa chỉ trả về và giá trị IP của địa chỉ trả về được đẩy vào ngăn xếp.

IP được tải từ nội dung của vị trí từ 'số loại' × 4

CS được tải từ nội dung của vị trí từ tiếp theo.

Cờ ngắt và Cờ bẫy được đặt lại thành 0

Địa chỉ bắt đầu cho ngắt kiểu0 là 000000H, cho ngắt kiểu1 là 00004H tương tự cho kiểu2 là 00008H và …… vv. Năm con trỏ đầu tiên là con trỏ ngắt chuyên dụng. tức là -

TYPE 0 ngắt biểu thị tình huống chia cho số không.

TYPE 1 ngắt đại diện cho việc thực hiện một bước trong quá trình gỡ lỗi của một chương trình.

TYPE 2 ngắt biểu diễn ngắt NMI không che được.

TYPE 3 ngắt biểu diễn ngắt điểm ngắt.

TYPE 4 ngắt biểu diễn ngắt tràn.

Các ngắt từ Kiểu 5 đến Kiểu 31 được dành riêng cho các bộ vi xử lý tiên tiến khác và ngắt từ 32 đến Kiểu 255 dành cho ngắt phần cứng và phần mềm.

Hướng dẫn ngắt INT 3 điểm ngắt

Nó là một lệnh 1 byte có mã op là CCH. Các lệnh này được chèn vào chương trình để khi bộ xử lý đến đó, nó sẽ dừng quá trình thực thi bình thường của chương trình và tuân theo thủ tục điểm ngắt.

Quá trình thực hiện của nó bao gồm các bước sau:

Giá trị thanh ghi cờ được đẩy vào ngăn xếp.

Giá trị CS của địa chỉ trả về và giá trị IP của địa chỉ trả về được đẩy vào ngăn xếp.

IP được tải từ nội dung của vị trí từ 3 × 4 = 0000CH

CS được tải từ nội dung của vị trí từ tiếp theo.

Cờ ngắt và Cờ bẫy được đặt lại thành 0

INTO - Ngắt trên lệnh tràn

Nó là một hướng dẫn 1 byte và ghi nhớ của họ INTO. Mã op cho hướng dẫn này là CEH. Như tên cho thấy nó là một lệnh ngắt có điều kiện, tức là nó chỉ hoạt động khi cờ tràn được đặt thành 1 và rẽ nhánh tới trình xử lý ngắt có số kiểu ngắt là 4. Nếu cờ tràn được đặt lại thì việc thực thi tiếp tục với hướng dẫn tiếp theo.

Quá trình thực hiện của nó bao gồm các bước sau:

Giá trị thanh ghi cờ được đẩy vào ngăn xếp.

Giá trị CS của địa chỉ trả về và giá trị IP của địa chỉ trả về được đẩy vào ngăn xếp.

IP được tải từ nội dung của vị trí từ 4 × 4 = 00010H

CS được tải từ nội dung của vị trí từ tiếp theo.

Cờ ngắt và cờ bẫy được đặt lại thành 0

Các cách khác nhau trong đó toán hạng nguồn được biểu thị trong một lệnh được gọi là addressing modes. Có 8 chế độ địa chỉ khác nhau trong lập trình 8086 -

Chế độ giải quyết ngay lập tức

Chế độ định địa chỉ trong đó toán hạng dữ liệu là một phần của bản thân lệnh được gọi là chế độ định địa chỉ tức thì.

Thí dụ

MOV CX, 4929 H, ADD AX, 2387 H, MOV AL, FFHĐăng ký chế độ địa chỉ

Nó có nghĩa là thanh ghi là nguồn của một toán hạng cho một lệnh.

Thí dụ

MOV CX, AX ; copies the contents of the 16-bit AX register into

; the 16-bit CX register),

ADD BX, AXChế độ địa chỉ trực tiếp

Chế độ định địa chỉ trong đó địa chỉ hiệu quả của vị trí bộ nhớ được ghi trực tiếp trong lệnh.

Thí dụ

MOV AX, [1592H], MOV AL, [0300H]Đăng ký chế độ địa chỉ gián tiếp

Chế độ định địa chỉ này cho phép dữ liệu được định địa chỉ tại bất kỳ vị trí bộ nhớ nào thông qua một địa chỉ bù được giữ trong bất kỳ thanh ghi nào sau đây: BP, BX, DI & SI.

Thí dụ

MOV AX, [BX] ; Suppose the register BX contains 4895H, then the contents

; 4895H are moved to AX

ADD CX, {BX}Chế độ địa chỉ dựa trên

Trong chế độ định địa chỉ này, địa chỉ offset của toán hạng được cho bởi tổng nội dung của các thanh ghi BX / BP và độ dịch chuyển 8 bit / 16 bit.

Thí dụ

MOV DX, [BX+04], ADD CL, [BX+08]Chế độ đánh chỉ mục

Trong chế độ định địa chỉ này, địa chỉ bù của toán hạng được tìm thấy bằng cách thêm nội dung của thanh ghi SI hoặc DI và các chuyển vị 8 bit / 16 bit.

Thí dụ

MOV BX, [SI+16], ADD AL, [DI+16]Chế độ địa chỉ dựa trên chỉ mục

Trong chế độ định địa chỉ này, địa chỉ bù đắp của toán hạng được tính bằng cách tính tổng thanh ghi cơ sở với nội dung của thanh ghi chỉ mục.

Thí dụ

ADD CX, [AX+SI], MOV AX, [AX+DI]Dựa trên được lập chỉ mục với chế độ dịch chuyển

Trong chế độ định địa chỉ này, phần bù toán hạng được tính bằng cách thêm nội dung thanh ghi cơ sở. Một chỉ mục đăng ký nội dung và độ dịch chuyển 8 hoặc 16-bit.

Thí dụ

MOV AX, [BX+DI+08], ADD CX, [BX+SI+16]Đa bộ xử lý có nghĩa là một tập hợp nhiều bộ xử lý thực hiện các lệnh đồng thời. Có ba cấu hình đa xử lý cơ bản.

- Cấu hình bộ đồng xử lý

- Cấu hình kết hợp chặt chẽ

- Cấu hình kết hợp lỏng lẻo

Cấu hình bộ đồng xử lý

Bộ đồng xử lý là một mạch được thiết kế đặc biệt trên chip vi xử lý có thể thực hiện cùng một tác vụ rất nhanh chóng mà bộ vi xử lý thực hiện. Nó làm giảm tải công việc của bộ xử lý chính. Bộ đồng xử lý chia sẻ cùng một bộ nhớ, hệ thống IO, bus, logic điều khiển và bộ tạo xung nhịp. Bộ đồng xử lý xử lý các tác vụ chuyên biệt như tính toán toán học, hiển thị đồ họa trên màn hình, v.v.

8086 và 8088 có thể thực hiện hầu hết các phép toán nhưng tập lệnh của chúng không thể thực hiện các phép toán phức tạp, vì vậy trong những trường hợp này, bộ vi xử lý yêu cầu bộ đồng xử lý toán học như bộ đồng xử lý toán học Intel 8087, có thể dễ dàng thực hiện các phép toán này rất nhanh chóng.

Sơ đồ khối của cấu hình bộ đồng xử lý

Bộ đồng xử lý và bộ xử lý được kết nối như thế nào?

Bộ đồng xử lý và bộ xử lý được kết nối qua tín hiệu TEST, RQ- / GT- và QS 0 & QS 1 .

Tín hiệu TEST được kết nối với chân BUSY của bộ đồng xử lý và 3 chân còn lại được kết nối với 3 chân cùng tên của bộ đồng xử lý.

Tín hiệu TEST quan tâm đến hoạt động của bộ đồng xử lý, tức là bộ đồng xử lý đang bận hoặc không hoạt động.

RT- / GT-được sử dụng để phân xử xe buýt.

Bộ đồng xử lý sử dụng QS 0 & QS 1 để theo dõi trạng thái của hàng đợi của bộ xử lý chủ.

Cấu hình được ghép nối chặt chẽ

Cấu hình kết hợp chặt chẽ tương tự như cấu hình bộ đồng xử lý, tức là cả hai chia sẻ cùng một bộ nhớ, bus hệ thống I / O, logic điều khiển và bộ tạo điều khiển với bộ xử lý chủ. Tuy nhiên, bộ xử lý đồng bộ xử lý và bộ xử lý máy chủ lưu trữ tìm nạp và thực hiện các lệnh riêng của chúng. Bus hệ thống được điều khiển bởi bộ đồng xử lý và bộ xử lý chủ một cách độc lập.

Sơ đồ khối của cấu hình được ghép nối chặt chẽ

Bộ xử lý và bộ xử lý độc lập được kết nối như thế nào?

Giao tiếp giữa máy chủ và bộ xử lý độc lập được thực hiện thông qua không gian bộ nhớ.

Không có hướng dẫn nào được sử dụng để giao tiếp, như WAIT, ESC, v.v.

Bộ xử lý chủ quản lý bộ nhớ và đánh thức bộ xử lý độc lập bằng cách gửi lệnh đến một trong các cổng của nó.

Sau đó, bộ xử lý độc lập truy cập bộ nhớ để thực thi tác vụ.

Sau khi hoàn thành nhiệm vụ, nó sẽ gửi một xác nhận đến bộ xử lý chủ bằng cách sử dụng tín hiệu trạng thái hoặc một yêu cầu ngắt.

Cấu hình được ghép nối lỏng lẻo

Cấu hình kết hợp lỏng bao gồm số lượng mô-đun của hệ thống dựa trên bộ vi xử lý, được kết nối thông qua một bus hệ thống chung. Mỗi mô-đun bao gồm bộ tạo xung nhịp, bộ nhớ, thiết bị I / O của riêng chúng và được kết nối thông qua một bus cục bộ.

Sơ đồ khối của cấu hình được ghép nối lỏng lẻo

Ưu điểm

Có nhiều bộ xử lý sẽ làm tăng hiệu quả.

Mỗi bộ xử lý đều có bus cục bộ riêng để truy cập bộ nhớ cục bộ / thiết bị I / O. Điều này giúp bạn dễ dàng đạt được quá trình xử lý song song.

Cấu trúc hệ thống linh hoạt, tức là sự cố của một mô-đun không ảnh hưởng đến sự cố toàn hệ thống; mô-đun bị lỗi có thể được thay thế sau đó.

Bộ xử lý dữ liệu số 8087 còn được gọi là Math co-processor, Numeric processor extension và Floating point unit. Đây là bộ đồng xử lý toán học đầu tiên được Intel thiết kế để ghép nối với 8086/8088 giúp tính toán dễ dàng hơn và nhanh hơn.

Khi các lệnh được bộ xử lý 8086/8088 xác định, thì nó sẽ được phân bổ cho bộ đồng xử lý 8087 để thực thi thêm.

Các kiểu dữ liệu được hỗ trợ bởi 8087 là -

- Số nguyên nhị phân

- Số thập phân đóng gói

- Số thực

- Định dạng thực tạm thời

Các tính năng nổi bật nhất của bộ xử lý dữ liệu số 8087 như sau:

Nó hỗ trợ dữ liệu kiểu số nguyên, kiểu float và kiểu thực khác nhau, từ 2-10 byte.

Tốc độ xử lý cao đến mức nó có thể tính phép nhân hai số thực 64 bit trong ~ 27 µs và cũng có thể tính căn bậc hai trong ~ 35 µs.

Nó tuân theo tiêu chuẩn dấu chấm động IEEE.

8087 kiến trúc

Kiến trúc 8087 được chia thành hai nhóm, tức là, Control Unit (CU) và Numeric Extension Unit (NEU).

Các control unit xử lý tất cả các giao tiếp giữa bộ xử lý và bộ nhớ chẳng hạn như nó nhận và giải mã các lệnh, đọc và ghi các toán hạng bộ nhớ, duy trì hàng đợi song song, v.v. Tất cả các lệnh của bộ đồng xử lý là lệnh ESC, tức là chúng bắt đầu bằng 'F', chỉ bộ đồng xử lý thực hiện các lệnh ESC trong khi các lệnh khác được thực thi bởi bộ vi xử lý.

Các numeric extension unitxử lý tất cả các lệnh của bộ xử lý số như lệnh số học, logic, siêu việt và truyền dữ liệu. Nó có 8 ngăn xếp thanh ghi, chứa các toán hạng cho các lệnh và kết quả của chúng.

Kiến trúc của bộ đồng xử lý 8087 như sau:

Mô tả mã pin 8087

Đầu tiên chúng ta hãy xem sơ đồ chân của 8087 -

Danh sách sau đây cung cấp Mô tả Pin của 8087 -

AD0 – AD15 - Đây là các đường địa chỉ / dữ liệu được ghép kênh theo thời gian, mang địa chỉ trong chu kỳ đồng hồ đầu tiên và dữ liệu từ chu kỳ đồng hồ thứ hai trở đi.

A19 / S6 – A16/S- Các dòng này là các dòng địa chỉ / trạng thái được ghép kênh theo thời gian. Nó hoạt động theo cách tương tự với các chân tương ứng của 8086. S 6 , S 4 và S3 có mức cao vĩnh viễn, trong khi S 5 ở mức thấp vĩnh viễn.

$\overline{BHE}$/S7 - Trong chu kỳ đồng hồ đầu tiên, $\overline{BHE}$/ S 7 được sử dụng để kích hoạt dữ liệu lên byte cao hơn của bus dữ liệu 8086 và sau đó hoạt động như dòng trạng thái S 7 .

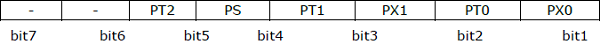

QS1, QS0 - Đây là các tín hiệu đầu vào trạng thái hàng đợi cung cấp trạng thái của hàng đợi lệnh, điều kiện của chúng như được hiển thị trong bảng sau -

| QS 0 | QS 1 | Trạng thái |

|---|---|---|

| 0 | 0 | Không hoạt động |

| 0 | 1 | Byte opcode đầu tiên từ hàng đợi |

| 1 | 0 | Dọn sạch hàng đợi |

| 1 | 1 | Byte tiếp theo từ hàng đợi |

INT - Là tín hiệu ngắt, tín hiệu này thay đổi thành mức cao khi nhận được một ngoại lệ chưa được che giấu trong quá trình thực thi.

BUSY - Là tín hiệu đầu ra, khi ở mức cao nó báo trạng thái bận cho CPU.

READY - Là tín hiệu đầu vào dùng để thông báo cho bộ đồng xử lý biết bus đã sẵn sàng nhận dữ liệu hay chưa.

RESET - Là tín hiệu đầu vào được sử dụng để từ chối các hoạt động bên trong của bộ đồng xử lý và chuẩn bị cho việc thực thi tiếp bất cứ khi nào CPU yêu cầu.

CLK - Đầu vào CLK cung cấp thời gian cơ bản cho hoạt động của bộ xử lý.

VCC - Là tín hiệu cấp nguồn, cần nguồn + 5V cung cấp cho hoạt động của mạch.

S0, S1, S2- Đây là các tín hiệu trạng thái cung cấp trạng thái hoạt động được Bộ điều khiển Bus 8087 sử dụng để tạo ra các tín hiệu điều khiển bộ nhớ và I / O. Các tín hiệu này hoạt động trong chu kỳ đồng hồ thứ tư.

| S 2 | S 1 | S 0 | Trạng thái hàng đợi |

|---|---|---|---|

| 0 | X | X | Không sử dụng |

| 1 | 0 | 0 | Không sử dụng |

| 1 | 0 | 1 | Đọc bộ nhớ |

| 1 | 1 | 0 | Ghi nhớ |

| 1 | 1 | 1 | Bị động |

RQ/GT1 & RQ/GT0 - Đây là những Request/Grant tín hiệu được sử dụng bởi bộ xử lý 8087 để giành quyền kiểm soát bus từ bộ xử lý chủ 8086/8088 để chuyển toán hạng.

Trong chương này, chúng ta sẽ thảo luận về Giao diện bộ nhớ và Giao diện IO với 8085.

Interfacelà con đường giao tiếp giữa hai thành phần. Giao diện có hai loại, giao tiếp bộ nhớ và giao tiếp I / O.

Giao diện bộ nhớ

Khi chúng ta thực hiện bất kỳ lệnh nào, chúng ta cần bộ vi xử lý truy cập bộ nhớ để đọc mã lệnh và dữ liệu được lưu trữ trong bộ nhớ. Đối với điều này, cả bộ nhớ và bộ vi xử lý đều yêu cầu một số tín hiệu để đọc và ghi vào thanh ghi.

Quá trình giao tiếp bao gồm một số yếu tố chính để phù hợp với yêu cầu bộ nhớ và tín hiệu của bộ vi xử lý. Do đó, mạch giao tiếp phải được thiết kế sao cho phù hợp với các yêu cầu tín hiệu bộ nhớ với các tín hiệu của bộ vi xử lý.

IO Interfacing

Có nhiều thiết bị giao tiếp khác nhau như bàn phím, chuột, máy in, v.v. Vì vậy, chúng ta cần giao diện bàn phím và các thiết bị khác với bộ vi xử lý bằng cách sử dụng chốt và bộ đệm. Loại giao tiếp này được gọi là giao tiếp I / O.

Sơ đồ khối của bộ nhớ và giao diện I / O

8085 chân giao diện

Sau đây là danh sách 8085 chân được sử dụng để giao tiếp với các thiết bị khác -

- A 15 - A 8 (Bus địa chỉ cao hơn)

- AD 7 - AD 0 (Địa chỉ thấp hơn / Bus dữ liệu)

- ALE

- RD

- WR

- READY

Cách thức giao tiếp - Bộ vi xử lý với thế giới bên ngoài?

Có hai cách giao tiếp mà bộ vi xử lý có thể kết nối với thế giới bên ngoài.

- Giao diện truyền thông nối tiếp

- Giao diện giao tiếp song song

Serial Communication Interface - Trong kiểu giao tiếp này, giao diện nhận một byte dữ liệu từ bộ vi xử lý và gửi từng bit một tới hệ thống khác theo thứ tự và ngược lại.

Parallel Communication Interface - Trong kiểu giao tiếp này, giao diện nhận một byte dữ liệu từ bộ vi xử lý và gửi nó từng bit đến các hệ thống khác theo kiểu song song (hoặc) và ngược lại.

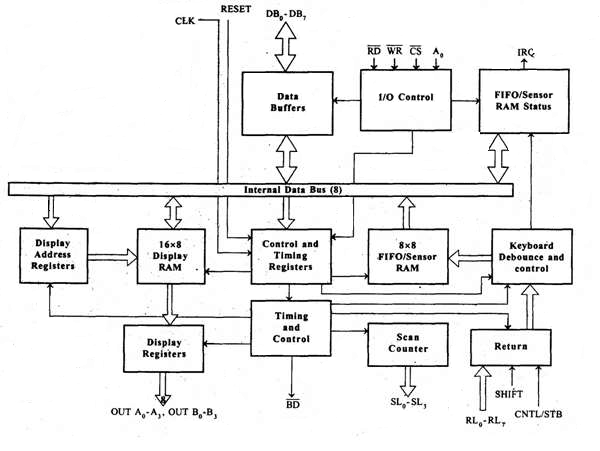

Bộ điều khiển màn hình / bàn phím lập trình 8279 được Intel thiết kế để giao tiếp bàn phím với CPU. Đầu tiên bàn phím sẽ quét bàn phím và xác định xem có phím nào đã được nhấn hay không. Sau đó, nó sẽ gửi phản hồi tương đối của phím được nhấn tới CPU và ngược lại.

Có bao nhiêu cách bàn phím được giao tiếp với CPU?

Bàn phím có thể được giao diện ở chế độ ngắt hoặc được thăm dò. bên trongInterrupt mode, bộ xử lý chỉ được yêu cầu bảo dưỡng nếu bất kỳ phím nào được nhấn, nếu không CPU sẽ tiếp tục với nhiệm vụ chính của nó.

bên trong Polled mode, CPU định kỳ đọc cờ bên trong 8279 để kiểm tra xem có phím nào được nhấn hay không bằng lực nhấn phím.

Bàn phím 8279 hoạt động như thế nào?

Bàn phím bao gồm tối đa 64 phím, được giao tiếp với CPU bằng cách sử dụng mã phím. Các mã khóa này được loại bỏ và được lưu trữ trong một FIFORAM 8 byte, CPU có thể được truy cập. Nếu nhiều hơn 8 ký tự được nhập vào FIFO, thì điều đó có nghĩa là hơn tám phím được nhấn cùng một lúc. Đây là khi trạng thái chạy quá mức được thiết lập.

Nếu một FIFO chứa một mục nhập khóa hợp lệ, thì CPU bị ngắt ở chế độ ngắt khác CPU sẽ kiểm tra trạng thái trong thăm dò để đọc mục nhập. Khi CPU đọc một mục nhập khóa, thì FIFO được cập nhật và mục nhập khóa được đẩy ra khỏi FIFO để tạo không gian cho các mục nhập mới.

Kiến trúc và mô tả

Kiểm soát I / O và Bộ đệm dữ liệu

Bộ phận này kiểm soát luồng dữ liệu thông qua bộ vi xử lý. Nó chỉ được bật khi D ở mức thấp. Bộ đệm dữ liệu của nó giao tiếp giữa bus bên ngoài của hệ thống với bus bên trong của bộ vi xử lý. Các chân A0, RD và WR được sử dụng cho các hoạt động lệnh, trạng thái hoặc đọc / ghi dữ liệu.

Đăng ký kiểm soát và thời gian và kiểm soát thời gian

Thiết bị này chứa các thanh ghi để lưu trữ bàn phím, các chế độ hiển thị và các hoạt động khác như được lập trình bởi CPU. Bộ điều khiển và định thời xử lý thời gian cho hoạt động của mạch.

Quét bộ đếm

Nó có hai chế độ tức là Encoded modevà chế độ Giải mã. Trong chế độ mã hóa, bộ đếm cung cấp số đếm nhị phân sẽ được giải mã bên ngoài để cung cấp các dòng quét cho bàn phím và màn hình.

bên trong decoded scan mode, bộ đếm giải mã nội bộ 2 bit ít quan trọng nhất và cung cấp 1 trong 4 lần quét được giải mã trên SL 0 -SL 3 .

Trả lại bộ đệm, lỗi bàn phím và điều khiển

Đầu tiên, đơn vị này sẽ quét hàng đóng phím, nếu tìm thấy thì đơn vị gỡ lỗi bàn phím sẽ xóa mục nhập phím. Trong trường hợp, cùng một khóa được phát hiện, thì mã của khóa đó được chuyển trực tiếp đến RAM cảm biến cùng với trạng thái phím SHIFT & CONTROL.

FIFO / RAM cảm biến và Logic trạng thái

Đơn vị này hoạt động như RAM 8 byte nhập trước xuất trước (FIFO) nơi mã khóa của mọi phím được nhấn được nhập vào RAM theo trình tự của chúng. Logic trạng thái tạo ra một yêu cầu ngắt sau mỗi thao tác đọc FIFO cho đến khi FIFO trống.

Trong chế độ ma trận cảm biến được quét, đơn vị này hoạt động như RAM cảm biến, nơi mỗi hàng của nó được tải trạng thái của hàng cảm biến tương ứng vào ma trận. Khi cảm biến thay đổi trạng thái, dòng IRQ sẽ chuyển sang mức cao và ngắt CPU.

Hiển thị thanh ghi địa chỉ và hiển thị RAM

This unit consists of display address registers which holds the addresses of the word currently read/written by the CPU to/from the display RAM.

8279 − Pin Description

The following figure shows the pin diagram of 8279 −

Data Bus Lines, DB0 - DB7

These are 8 bidirectional data bus lines used to transfer the data to/from the CPU.

CLK

The clock input is used to generate internal timings required by the microprocessor.

RESET

As the name suggests this pin is used to reset the microprocessor.

CS Chip Select

When this pin is set to low, it allows read/write operations, else this pin should be set to high.

A0

This pin indicates the transfer of command/status information. When it is low, it indicates the transfer of data.

RD, WR

This Read/Write pin enables the data buffer to send/receive data over the data bus.

IRQ

This interrupt output line goes high when there is data in the FIFO sensor RAM. The interrupt line goes low with each FIFO RAM read operation. However, if the FIFO RAM further contains any key-code entry to be read by the CPU, this pin again goes high to generate an interrupt to the CPU.

Vss, Vcc

These are the ground and power supply lines of the microprocessor.

SL0 − SL3

These are the scan lines used to scan the keyboard matrix and display the digits. These lines can be programmed as encoded or decoded, using the mode control register.

RL0 − RL7

These are the Return Lines which are connected to one terminal of keys, while the other terminal of the keys is connected to the decoded scan lines. These lines are set to 0 when any key is pressed.

SHIFT

The Shift input line status is stored along with every key code in FIFO in the scanned keyboard mode. Till it is pulled low with a key closure, it is pulled up internally to keep it high

CNTL/STB - CONTROL/STROBED I/P Mode

In the keyboard mode, this line is used as a control input and stored in FIFO on a key closure. The line is a strobe line that enters the data into FIFO RAM, in the strobed input mode. It has an internal pull up. The line is pulled down with a key closure.

BD

It stands for blank display. It is used to blank the display during digit switching.

OUTA0 – OUTA3 and OUTB0 – OUTB3

These are the output ports for two 16x4 or one 16x8 internal display refresh registers. The data from these lines is synchronized with the scan lines to scan the display and the keyboard.

Operational Modes of 8279

There are two modes of operation on 8279 − Input Mode and Output Mode.

Input Mode

This mode deals with the input given by the keyboard and this mode is further classified into 3 modes.

Scanned Keyboard Mode − In this mode, the key matrix can be interfaced using either encoded or decoded scans. In the encoded scan, an 8×8 keyboard or in the decoded scan, a 4×8 keyboard can be interfaced. The code of key pressed with SHIFT and CONTROL status is stored into the FIFO RAM.

Scanned Sensor Matrix − In this mode, a sensor array can be interfaced with the processor using either encoder or decoder scans. In the encoder scan, 8×8 sensor matrix or with decoder scan 4×8 sensor matrix can be interfaced.

Strobed Input − In this mode, when the control line is set to 0, the data on the return lines is stored in the FIFO byte by byte.

Output Mode

This mode deals with display-related operations. This mode is further classified into two output modes.

Display Scan − This mode allows 8/16 character multiplexed displays to be organized as dual 4-bit/single 8-bit display units.

Display Entry − This mode allows the data to be entered for display either from the right side/left side.

DMA stands for Direct Memory Access. It is designed by Intel to transfer data at the fastest rate. It allows the device to transfer the data directly to/from memory without any interference of the CPU.

Using a DMA controller, the device requests the CPU to hold its data, address and control bus, so the device is free to transfer data directly to/from the memory. The DMA data transfer is initiated only after receiving HLDA signal from the CPU.

How DMA Operations are Performed?

Following is the sequence of operations performed by a DMA −

Initially, when any device has to send data between the device and the memory, the device has to send DMA request (DRQ) to DMA controller.

The DMA controller sends Hold request (HRQ) to the CPU and waits for the CPU to assert the HLDA.

Then the microprocessor tri-states all the data bus, address bus, and control bus. The CPU leaves the control over bus and acknowledges the HOLD request through HLDA signal.

Now the CPU is in HOLD state and the DMA controller has to manage the operations over buses between the CPU, memory, and I/O devices.

Features of 8257

Here is a list of some of the prominent features of 8257 −

It has four channels which can be used over four I/O devices.

Each channel has 16-bit address and 14-bit counter.

Each channel can transfer data up to 64kb.

Each channel can be programmed independently.

Each channel can perform read transfer, write transfer and verify transfer operations.

It generates MARK signal to the peripheral device that 128 bytes have been transferred.

It requires a single phase clock.

Its frequency ranges from 250Hz to 3MHz.

It operates in 2 modes, i.e., Master mode and Slave mode.

8257 Architecture

The following image shows the architecture of 8257 −

8257 Pin Description

The following image shows the pin diagram of a 8257 DMA controller −

DRQ0−DRQ3

These are the four individual channel DMA request inputs, which are used by the peripheral devices for using DMA services. When the fixed priority mode is selected, then DRQ0 has the highest priority and DRQ3 has the lowest priority among them.

DACKo − DACK3

These are the active-low DMA acknowledge lines, which updates the requesting peripheral about the status of their request by the CPU. These lines can also act as strobe lines for the requesting devices.

Do − D7

These are bidirectional, data lines which are used to interface the system bus with the internal data bus of DMA controller. In the Slave mode, it carries command words to 8257 and status word from 8257. In the master mode, these lines are used to send higher byte of the generated address to the latch. This address is further latched using ADSTB signal.

IOR

It is an active-low bidirectional tri-state input line, which is used by the CPU to read internal registers of 8257 in the Slave mode. In the master mode, it is used to read data from the peripheral devices during a memory write cycle.

IOW

It is an active low bi-direction tri-state line, which is used to load the contents of the data bus to the 8-bit mode register or upper/lower byte of a 16-bit DMA address register or terminal count register. In the master mode, it is used to load the data to the peripheral devices during DMA memory read cycle.

CLK

It is a clock frequency signal which is required for the internal operation of 8257.

RESET

This signal is used to RESET the DMA controller by disabling all the DMA channels.

Ao - A3

These are the four least significant address lines. In the slave mode, they act as an input, which selects one of the registers to be read or written. In the master mode, they are the four least significant memory address output lines generated by 8257.

CS

It is an active-low chip select line. In the Slave mode, it enables the read/write operations to/from 8257. In the master mode, it disables the read/write operations to/from 8257.

A4 - A7

These are the higher nibble of the lower byte address generated by DMA in the master mode.

READY

It is an active-high asynchronous input signal, which makes DMA ready by inserting wait states.

HRQ

This signal is used to receive the hold request signal from the output device. In the slave mode, it is connected with a DRQ input line 8257. In Master mode, it is connected with HOLD input of the CPU.

HLDA

It is the hold acknowledgement signal which indicates the DMA controller that the bus has been granted to the requesting peripheral by the CPU when it is set to 1.

MEMR

It is the low memory read signal, which is used to read the data from the addressed memory locations during DMA read cycles.

MEMW

It is the active-low three state signal which is used to write the data to the addressed memory location during DMA write operation.

ADST

This signal is used to convert the higher byte of the memory address generated by the DMA controller into the latches.

AEN

This signal is used to disable the address bus/data bus.

TC

It stands for ‘Terminal Count’, which indicates the present DMA cycle to the present peripheral devices.

MARK

The mark will be activated after each 128 cycles or integral multiples of it from the beginning. It indicates the current DMA cycle is the 128th cycle since the previous MARK output to the selected peripheral device.

Vcc

It is the power signal which is required for the operation of the circuit.

A microcontroller is a small and low-cost microcomputer, which is designed to perform the specific tasks of embedded systems like displaying microwave’s information, receiving remote signals, etc.

The general microcontroller consists of the processor, the memory (RAM, ROM, EPROM), Serial ports, peripherals (timers, counters), etc.

Difference between Microprocessor and Microcontroller

The following table highlights the differences between a microprocessor and a microcontroller −

| Microcontroller | Microprocessor |

|---|---|

| Microcontrollers are used to execute a single task within an application. | Microprocessors are used for big applications. |

| Its designing and hardware cost is low. | Its designing and hardware cost is high. |

| Easy to replace. | Not so easy to replace. |

| It is built with CMOS technology, which requires less power to operate. | Its power consumption is high because it has to control the entire system. |

| It consists of CPU, RAM, ROM, I/O ports. | It doesn’t consist of RAM, ROM, I/O ports. It uses its pins to interface to peripheral devices. |

Types of Microcontrollers

Microcontrollers are divided into various categories based on memory, architecture, bits and instruction sets. Following is the list of their types −

Bit

Based on bit configuration, the microcontroller is further divided into three categories.

8-bit microcontroller − This type of microcontroller is used to execute arithmetic and logical operations like addition, subtraction, multiplication division, etc. For example, Intel 8031 and 8051 are 8 bits microcontroller.

16-bit microcontroller − This type of microcontroller is used to perform arithmetic and logical operations where higher accuracy and performance is required. For example, Intel 8096 is a 16-bit microcontroller.

32-bit microcontroller − This type of microcontroller is generally used in automatically controlled appliances like automatic operational machines, medical appliances, etc.

Memory

Based on the memory configuration, the microcontroller is further divided into two categories.

External memory microcontroller − This type of microcontroller is designed in such a way that they do not have a program memory on the chip. Hence, it is named as external memory microcontroller. For example: Intel 8031 microcontroller.

Embedded memory microcontroller − This type of microcontroller is designed in such a way that the microcontroller has all programs and data memory, counters and timers, interrupts, I/O ports are embedded on the chip. For example: Intel 8051 microcontroller.

Instruction Set

Based on the instruction set configuration, the microcontroller is further divided into two categories.

CISC − CISC stands for complex instruction set computer. It allows the user to insert a single instruction as an alternative to many simple instructions.

RISC − RISC stands for Reduced Instruction Set Computers. It reduces the operational time by shortening the clock cycle per instruction.

Applications of Microcontrollers

Microcontrollers are widely used in various different devices such as −

Light sensing and controlling devices like LED.

Temperature sensing and controlling devices like microwave oven, chimneys.

Fire detection and safety devices like Fire alarm.

Measuring devices like Volt Meter.

8051 microcontroller is designed by Intel in 1981. It is an 8-bit microcontroller. It is built with 40 pins DIP (dual inline package), 4kb of ROM storage and 128 bytes of RAM storage, 2 16-bit timers. It consists of are four parallel 8-bit ports, which are programmable as well as addressable as per the requirement. An on-chip crystal oscillator is integrated in the microcontroller having crystal frequency of 12 MHz.

Let us now discuss the architecture of 8051 Microcontroller.

In the following diagram, the system bus connects all the support devices to the CPU. The system bus consists of an 8-bit data bus, a 16-bit address bus and bus control signals. All other devices like program memory, ports, data memory, serial interface, interrupt control, timers, and the CPU are all interfaced together through the system bus.

The pin diagram of 8051 microcontroller looks as follows −

Pins 1 to 8 − These pins are known as Port 1. This port doesn’t serve any other functions. It is internally pulled up, bi-directional I/O port.

Pin 9 − It is a RESET pin, which is used to reset the microcontroller to its initial values.

Pins 10 to 17 − These pins are known as Port 3. This port serves some functions like interrupts, timer input, control signals, serial communication signals RxD and TxD, etc.

Pins 18 & 19 − These pins are used for interfacing an external crystal to get the system clock.

Pin 20 − This pin provides the power supply to the circuit.

Pins 21 to 28 − These pins are known as Port 2. It serves as I/O port. Higher order address bus signals are also multiplexed using this port.

Pin 29 − This is PSEN pin which stands for Program Store Enable. It is used to read a signal from the external program memory.

Pin 30 − This is EA pin which stands for External Access input. It is used to enable/disable the external memory interfacing.

Pin 31 − This is ALE pin which stands for Address Latch Enable. It is used to demultiplex the address-data signal of port.

Pins 32 to 39 − These pins are known as Port 0. It serves as I/O port. Lower order address and data bus signals are multiplexed using this port.

Pin 40 − This pin is used to provide power supply to the circuit.

8051 microcontrollers have 4 I/O ports each of 8-bit, which can be configured as input or output. Hence, total 32 input/output pins allow the microcontroller to be connected with the peripheral devices.

Pin configuration, i.e. the pin can be configured as 1 for input and 0 for output as per the logic state.

Input/Output (I/O) pin − All the circuits within the microcontroller must be connected to one of its pins except P0 port because it does not have pull-up resistors built-in.

Input pin − Logic 1 is applied to a bit of the P register. The output FE transistor is turned off and the other pin remains connected to the power supply voltage over a pull-up resistor of high resistance.

Port 0 − The P0 (zero) port is characterized by two functions −

When the external memory is used then the lower address byte (addresses A0A7) is applied on it, else all bits of this port are configured as input/output.

When P0 port is configured as an output then other ports consisting of pins with built-in pull-up resistor connected by its end to 5V power supply, the pins of this port have this resistor left out.

Input Configuration

If any pin of this port is configured as an input, then it acts as if it “floats”, i.e. the input has unlimited input resistance and in-determined potential.

Output Configuration