Circuits séquentiels

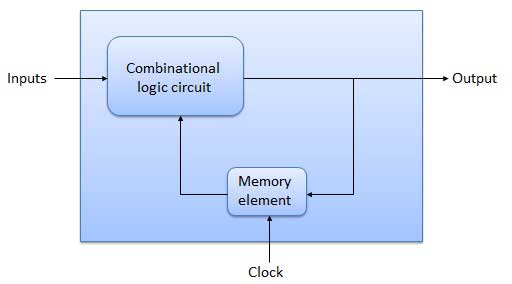

Le circuit combinatoire n'utilise aucune mémoire. Par conséquent, l'état précédent de l'entrée n'a aucun effet sur l'état actuel du circuit. Mais le circuit séquentiel a une mémoire, donc la sortie peut varier en fonction de l'entrée. Ce type de circuits utilise une entrée, une sortie, une horloge et un élément de mémoire précédents.

Diagramme

Tongues

La bascule est un circuit séquentiel qui échantillonne généralement ses entrées et ne modifie ses sorties qu'à des instants de temps particuliers et non en continu. On dit que la bascule est sensible aux bords ou déclenchée par les bords plutôt que d'être déclenchée au niveau comme des verrous.

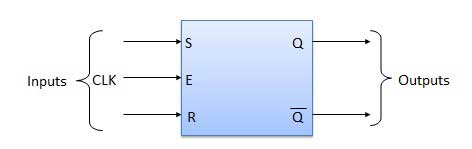

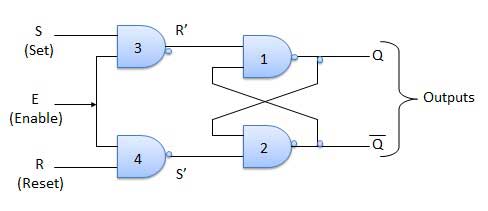

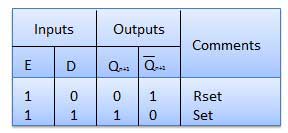

Flip Flop SR

Il s'agit essentiellement d'un verrou SR utilisant des portes NAND avec un enablecontribution. Il est également appelé SR-FF déclenché par niveau. Pour cela, le circuit en sortie aura lieu si et seulement si l'entrée de validation (E) est rendue active. En bref, ce circuit fonctionnera comme un verrou SR si E = 1 mais il n'y a pas de changement dans la sortie si E = 0.

Diagramme

Schéma

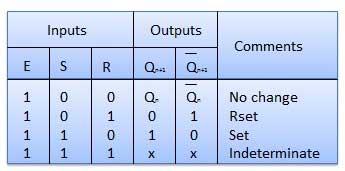

Table de vérité

Opération

| SN | État | Opération |

|---|---|---|

| 1 | S = R = 0 : No change | Si S = R = 0, la sortie des portes NAND 3 et 4 est forcée de devenir 1. Par conséquent, R 'et S' seront tous deux égaux à 1. Puisque S 'et R' sont l'entrée du verrou SR de base utilisant des portes NAND, il n'y aura pas de changement dans l'état des sorties. |

| 2 | S = 0, R = 1, E = 1 | Puisque S = 0, la sortie de NAND-3 c'est-à-dire R '= 1 et E = 1 la sortie de NAND-4 c'est-à-dire S' = 0. D'où Q n + 1 = 0 et Q n + 1 bar = 1. Il s'agit d'une condition de réinitialisation. |

| 3 | S = 1, R = 0, E = 1 | Sortie de NAND-3 c'est-à-dire R '= 0 et sortie de NAND-4 soit S' = 1. Par conséquent, la sortie du verrou SR NAND est Q n + 1 = 1 et Q n + 1 bar = 0. Il s'agit de la condition de réinitialisation. |

| 4 | S = 1, R = 1, E = 1 | Comme S = 1, R = 1 et E = 1, la sortie des portes NAND 3 et 4 est toutes deux 0, c'est-à-dire que S '= R' = 0. D'où le Race condition se produira dans le verrou NAND de base. |

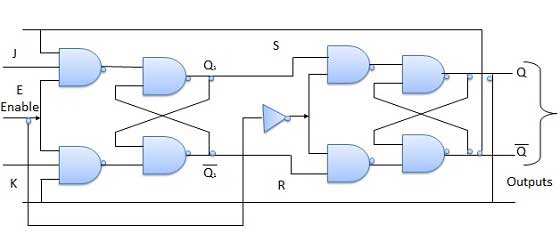

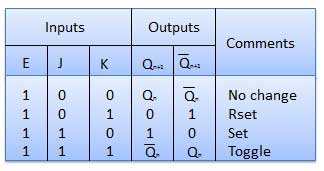

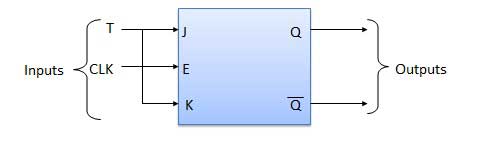

Flip Flop maître esclave JK

Le maître esclave JK FF est une cascade de deux SR FF avec retour de la sortie du second vers l'entrée du premier. Master est un niveau positif déclenché. Mais en raison de la présence de l'onduleur dans la ligne d'horloge, l'esclave répondra au niveau négatif. Par conséquent, lorsque l'horloge = 1 (niveau positif), le maître est actif et l'esclave est inactif. Alors que quand horloge = 0 (niveau bas), l'esclave est actif et le maître est inactif.

Schéma

Table de vérité

Opération

| SN | État | Opération |

|---|---|---|

| 1 | J = K = 0 (No change) | Lorsque clock = 0, l'esclave devient actif et le maître est inactif. Mais comme les entrées S et R n'ont pas changé, les sorties esclaves resteront également inchangées. Par conséquent, les sorties ne changeront pas si J = K = 0. |

| 2 | J = 0 and K = 1 (Reset) | Horloge = 1 - Maître actif, esclave inactif. Par conséquent, les sorties du maître deviennent Q 1 = 0 et Q 1 bar = 1. Cela signifie S = 0 et R = 1. Horloge = 0 - Esclave actif, maître inactif. Par conséquent, les sorties de l'esclave deviennent Q = 0 et Q bar = 1. Encore une fois horloge = 1 - Maître actif, esclave inactif. Par conséquent, même avec les sorties modifiées Q = 0 et Q bar = 1 renvoyées au maître, sa sortie sera Q1 = 0 et Q1 bar = 1. Cela signifie S = 0 et R = 1. Ainsi, avec horloge = 0 et esclave devenant actif, les sorties de l'esclave resteront Q = 0 et Q bar = 1. Ainsi, nous obtenons une sortie stable du maître esclave. |

| 3 | J = 1 and K = 0 (Set) | Horloge = 1 - Maître actif, esclave inactif. Par conséquent, les sorties du maître deviennent Q 1 = 1 et Q 1 bar = 0. Cela signifie S = 1 et R = 0. Horloge = 0 - Esclave actif, maître inactif. Par conséquent, les sorties de l'esclave deviennent Q = 1 et Q bar = 0. Encore une fois clock = 1 - alors on peut montrer que les sorties de l'esclave sont stabilisées à Q = 1 et Q bar = 0. |

| 4 | J = K = 1 (Toggle) | Horloge = 1 - Maître actif, esclave inactif. Les sorties du maître basculeront. Donc S et R seront également inversés. Horloge = 0 - Esclave actif, maître inactif. Les sorties de l'esclave basculeront. Ces sorties modifiées sont renvoyées aux entrées principales. Mais puisque clock = 0, le maître est toujours inactif. Il ne répond donc pas à ces sorties modifiées. Cela évite le basculement multiple qui conduit à la condition de course autour. La bascule maître esclave évitera la condition de contournement. |

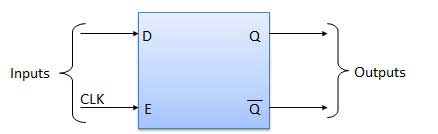

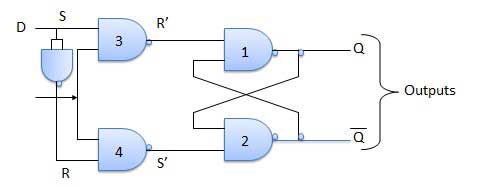

Retard Flip Flop / D Flip Flop

Delay Flip Flop ou D Flip Flop est le verrou SR à déclenchement simple avec un inverseur NAND connecté entre les entrées S et R. Il n'a qu'une seule entrée. Les données d'entrée apparaissent à la sortie après un certain temps. En raison de ce retard de données entre i / p et o / p, on parle de bascule à retard. S et R seront les compléments l'un de l'autre en raison de l'inverseur NAND. Donc S = R = 0 ou S = R = 1, ces conditions d'entrée n'apparaîtront jamais. Ce problème est évité par les conditions SR = 00 et SR = 1.

Diagramme

Schéma

Table de vérité

Opération

| SN | État | Opération |

|---|---|---|

| 1 | E = 0 | Le verrou est désactivé. Donc pas de changement de rendement. |

| 2 | E = 1 and D = 0 | Si E = 1 et D = 0 alors S = 0 et R = 1. Ainsi, quel que soit l'état actuel, l'état suivant est Q n + 1 = 0 et Q n + 1 bar = 1. C'est la condition de réinitialisation. |

| 3 | E = 1 and D = 1 | Si E = 1 et D = 1, alors S = 1 et R = 0. Cela définira le verrou et Q n + 1 = 1 et Q n + 1 bar = 0 quel que soit l'état actuel. |

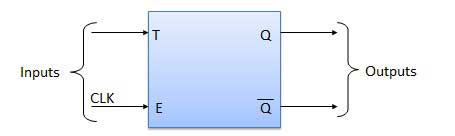

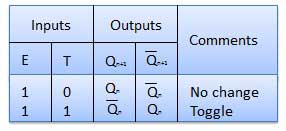

Basculer Flip Flop / T Flip Flop

Bascule bascule est essentiellement une bascule JK avec des bornes J et K connectées en permanence ensemble. Il n'a qu'une entrée désignée parTcomme indiqué dans le diagramme des symboles. Le symbole de la bascule T déclenchée par front montant est indiqué dans le diagramme.

Diagramme de symboles

Diagramme

Table de vérité

Opération

| SN | État | Opération |

|---|---|---|

| 1 | T = 0, J = K = 0 | Les barres Q et Q de sortie ne changeront pas |

| 2 | T = 1, J = K = 1 | La sortie bascule en fonction de chaque front montant du signal d'horloge. |