병렬 컴퓨터 아키텍처-모델

병렬 처리는 실제 응용 프로그램에서 더 높은 성능, 더 낮은 비용 및 정확한 결과에 대한 요구를 충족하기 위해 현대 컴퓨터에서 효과적인 기술로 개발되었습니다. 동시 이벤트는 다중 프로그래밍, 다중 처리 또는 다중 컴퓨팅의 관행으로 인해 오늘날의 컴퓨터에서 일반적입니다.

현대 컴퓨터에는 강력하고 광범위한 소프트웨어 패키지가 있습니다. 컴퓨터 성능의 발전을 분석하려면 먼저 하드웨어와 소프트웨어의 기본적인 발전을 이해해야합니다.

Computer Development Milestones − 컴퓨터 개발에는 크게 두 단계가 있습니다. mechanical 또는 electromechanical부속. 현대 컴퓨터는 전자 부품이 도입 된 후 진화했습니다. 전자 컴퓨터의 높은 이동성 전자가 기계 컴퓨터의 작동 부품을 대체했습니다. 정보 전송의 경우 거의 빛의 속도로 이동하는 전기 신호가 기계식 기어 또는 레버를 대체했습니다.

Elements of Modern computers − 최신 컴퓨터 시스템은 컴퓨터 하드웨어, 명령어 세트, 응용 프로그램, 시스템 소프트웨어 및 사용자 인터페이스로 구성됩니다.

컴퓨팅 문제는 수치 컴퓨팅, 논리적 추론 및 트랜잭션 처리로 분류됩니다. 일부 복잡한 문제는 세 가지 처리 모드를 모두 조합해야 할 수 있습니다.

Evolution of Computer Architecture− 지난 40 년 동안 컴퓨터 아키텍처는 혁신적인 변화를 겪었습니다. 우리는 Von Neumann 아키텍처로 시작했고 이제는 다중 컴퓨터와 다중 프로세서가 있습니다.

Performance of a computer system− 컴퓨터 시스템의 성능은 기계 성능과 프로그램 동작에 따라 다릅니다. 더 나은 하드웨어 기술, 고급 아키텍처 기능 및 효율적인 리소스 관리를 통해 기계 기능을 향상시킬 수 있습니다. 프로그램 동작은 애플리케이션 및 런타임 조건에 따라 달라 지므로 예측할 수 없습니다.

다중 프로세서 및 다중 컴퓨터

이 섹션에서는 두 가지 유형의 병렬 컴퓨터에 대해 설명합니다.

- Multiprocessors

- Multicomputers

공유 메모리 다중 컴퓨터

가장 일반적인 세 가지 공유 메모리 다중 프로세서 모델은 다음과 같습니다.

UMA (Uniform Memory Access)

이 모델에서 모든 프로세서는 물리적 메모리를 균일하게 공유합니다. 모든 프로세서는 모든 메모리 단어에 대해 동일한 액세스 시간을 갖습니다. 각 프로세서에는 개인 캐시 메모리가있을 수 있습니다. 주변 장치에도 동일한 규칙이 적용됩니다.

모든 프로세서가 모든 주변 장치에 동등하게 액세스 할 수있는 경우 시스템을 symmetric multiprocessor. 하나 또는 몇 개의 프로세서 만 주변 장치에 액세스 할 수있는 경우 시스템을asymmetric multiprocessor.

NUMA (Non-Uniform Memory Access)

NUMA 멀티 프로세서 모델에서 액세스 시간은 메모리 워드의 위치에 따라 다릅니다. 여기서 공유 메모리는 로컬 메모리라고하는 모든 프로세서에 물리적으로 분산됩니다. 모든 로컬 메모리의 모음은 모든 프로세서가 액세스 할 수있는 전역 주소 공간을 형성합니다.

캐시 전용 메모리 아키텍처 (COMA)

COMA 모델은 NUMA 모델의 특별한 경우입니다. 여기서 분산 된 모든 메인 메모리는 캐시 메모리로 변환됩니다.

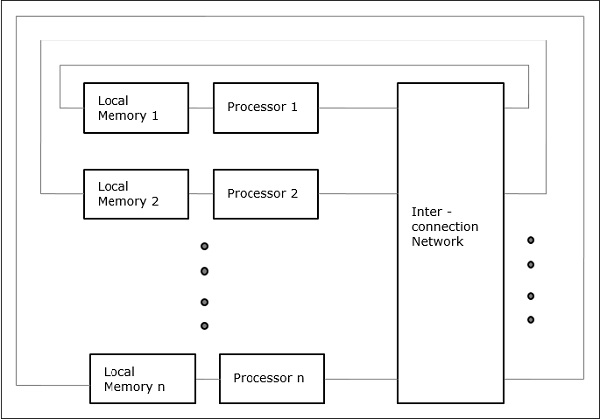

Distributed - Memory Multicomputers− 분산 메모리 다중 컴퓨터 시스템은 메시지 전달 네트워크에 의해 상호 연결된 노드라고하는 여러 컴퓨터로 구성됩니다. 각 노드는 프로세서, 로컬 메모리 및 때때로 I / O 장치가있는 자율 컴퓨터 역할을합니다. 이 경우 모든 로컬 메모리는 비공개이며 로컬 프로세서 만 액세스 할 수 있습니다. 이것이 전통적인 기계가no-remote-memory-access (NORMA) 기계.

다중 벡터 및 SIMD 컴퓨터

이 섹션에서는 벡터 처리 및 데이터 병렬 처리를위한 슈퍼 컴퓨터 및 병렬 프로세서에 대해 설명합니다.

벡터 슈퍼 컴퓨터

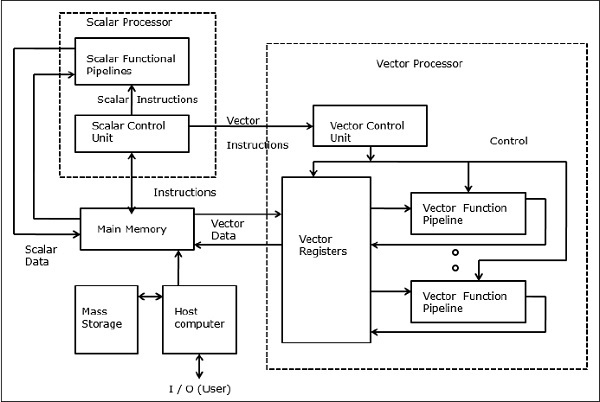

벡터 컴퓨터에서 벡터 프로세서는 옵션 기능으로 스칼라 프로세서에 연결됩니다. 호스트 컴퓨터는 먼저 프로그램과 데이터를 주 메모리에로드합니다. 그런 다음 스칼라 제어 장치는 모든 명령을 디코딩합니다. 디코딩 된 명령어가 스칼라 연산 또는 프로그램 연산 인 경우 스칼라 프로세서는 스칼라 함수 파이프 라인을 사용하여 해당 연산을 실행합니다.

반면에, 디코딩 된 명령어가 벡터 연산이면 명령어는 벡터 제어 유닛으로 전송됩니다.

SIMD 슈퍼 컴퓨터

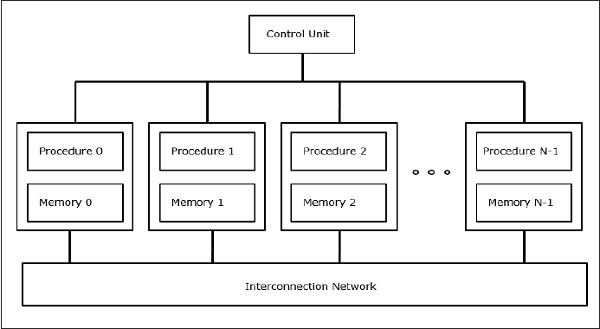

SIMD 컴퓨터에서는 'N'개의 프로세서가 제어 장치에 연결되고 모든 프로세서에는 개별 메모리 장치가 있습니다. 모든 프로세서는 상호 연결 네트워크로 연결됩니다.

PRAM 및 VLSI 모델

이상적인 모델은 물리적 제약이나 구현 세부 사항을 고려하지 않고 병렬 알고리즘을 개발하는 데 적합한 프레임 워크를 제공합니다.

이 모델은 병렬 컴퓨터에서 이론적 인 성능 한계를 얻거나 칩이 제조되기 전에 칩 영역 및 작동 시간에 대한 VLSI 복잡성을 평가하도록 적용 할 수 있습니다.

병렬 랜덤 액세스 머신

Sheperdson과 Sturgis (1963)는 기존의 Uniprocessor 컴퓨터를 RAM (random-access-machines)으로 모델링했습니다. Fortune과 Wyllie (1978)는 메모리 액세스 오버 헤드와 동기화가없는 이상화 된 병렬 컴퓨터를 모델링하기위한 병렬 랜덤 액세스 머신 (PRAM) 모델을 개발했습니다.

N 프로세서 PRAM에는 공유 메모리 장치가 있습니다. 이 공유 메모리는 중앙 집중화되거나 프로세서간에 분산 될 수 있습니다. 이러한 프로세서는 동기화 된 읽기 메모리, 쓰기 메모리 및 컴퓨팅주기에서 작동합니다. 따라서 이러한 모델은 동시 읽기 및 쓰기 작업이 처리되는 방식을 지정합니다.

다음은 가능한 메모리 업데이트 작업입니다.

Exclusive read (ER) −이 방법에서는 각 사이클에서 하나의 프로세서 만 모든 메모리 위치에서 읽을 수 있습니다.

Exclusive write (EW) −이 방법에서는 한 번에 하나 이상의 프로세서가 메모리 위치에 쓸 수 있습니다.

Concurrent read (CR) − 여러 프로세서가 동일한주기에서 동일한 메모리 위치에서 동일한 정보를 읽을 수 있습니다.

Concurrent write (CW)− 동일한 메모리 위치에 동시 쓰기 작업이 가능합니다. 쓰기 충돌을 방지하기 위해 일부 정책이 설정됩니다.

VLSI 복잡성 모델

병렬 컴퓨터는 VLSI 칩을 사용하여 프로세서 어레이, 메모리 어레이 및 대규모 스위칭 네트워크를 제작합니다.

오늘날 VLSI 기술은 2 차원입니다. VLSI 칩의 크기는 해당 칩에서 사용할 수있는 스토리지 (메모리) 공간의 양에 비례합니다.

알고리즘의 VLSI 칩 구현의 칩 영역 (A)으로 알고리즘의 공간 복잡도를 계산할 수 있습니다. T가 알고리즘을 실행하는 데 필요한 시간 (대기 시간)이면 AT는 칩 (또는 I / O)을 통해 처리되는 총 비트 수에 대한 상한을 제공합니다. 특정 컴퓨팅의 경우 하한 f (s)가 있습니다.

AT 2 > = O (f (s))

A = 칩 면적, T = 시간

건축 개발 트랙

병렬 컴퓨터의 진화는 다음과 같은 경로를 따라 퍼졌습니다.

- 다중 프로세서 트랙

- 다중 프로세서 트랙

- 다중 컴퓨터 트랙

- 다중 데이터 트랙

- 벡터 트랙

- SIMD 트랙

- 다중 스레드 추적

- 다중 스레드 트랙

- Dataflow 트랙

에 multiple processor track, 서로 다른 스레드가 서로 다른 프로세서에서 동시에 실행되고 공유 메모리 (다중 프로세서 트랙) 또는 메시지 전달 (다중 컴퓨터 트랙) 시스템을 통해 통신한다고 가정합니다.

에 multiple data track, 방대한 양의 데이터에 대해 동일한 코드가 실행된다고 가정합니다. 데이터 요소 시퀀스 (벡터 트랙)에 대해 동일한 명령을 실행하거나 유사한 데이터 세트 (SIMD 트랙)에 대해 동일한 명령 시퀀스를 실행하여 수행됩니다.

에 multiple threads track, 서로 다른 프로세서에서 실행되는 스레드 간의 동기화 지연을 숨기기 위해 동일한 프로세서에서 다양한 스레드의 인터리빙 실행을 가정합니다. 스레드 인터리빙은 거칠거나 (다중 스레드 트랙) 미세 (데이터 흐름 트랙) 일 수 있습니다.