555 Timer

o 555 TimerO nome do IC vem dos três resistores $ 5K \ Omega $ que são usados em sua rede divisora de tensão. Este IC é útil para gerar oscilações e atrasos de tempo precisos. Este capítulo explica sobre o 555 Timer em detalhes.

Diagrama de Pinos e Diagrama Funcional

Nesta seção, primeiro vamos discutir sobre o diagrama de pinos do 555 Timer IC e, em seguida, seu diagrama funcional.

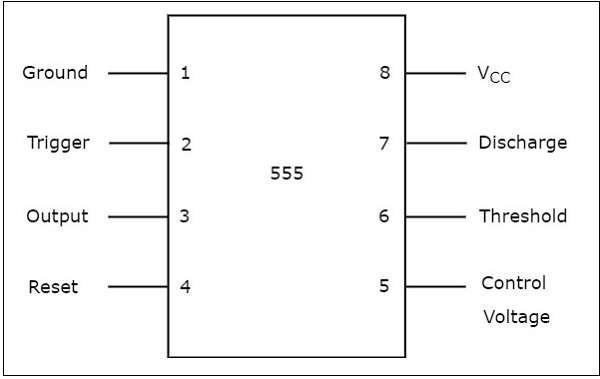

Diagrama de Pin

O 555 Timer IC é um mini Dual-Inline Package (DIP) de 8 pinos. opin diagram de um 555 Timer IC é mostrado na figura a seguir -

O significado de cada pino é autoexplicativo no diagrama acima. Este 555 Timer IC pode ser operado com uma alimentação DC de + 5V a + 18V. É principalmente útil para gerarnon-sinusoidal formas de onda como quadrado, rampa, pulso e etc

Diagrama Funcional

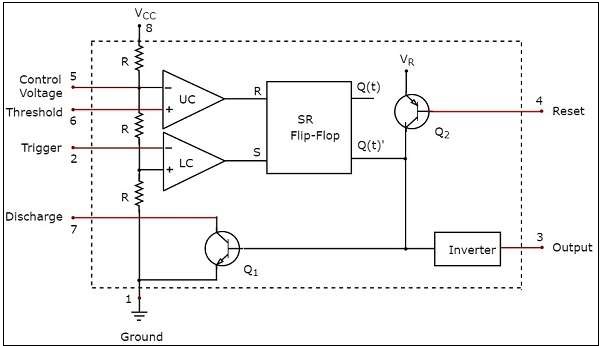

A representação pictórica mostrando os detalhes internos de um temporizador 555 é conhecida como diagrama funcional.

o functional diagram de 555 Timer IC é mostrado na figura a seguir -

Observe que o diagrama funcional do 555 Timer contém uma rede divisora de tensão, dois comparadores, um flip-flop SR, dois transistores e um inversor. Esta seção discute sobre a finalidade de cada bloco ou componente em detalhes -

Rede Divisora de Tensão

A rede do divisor de tensão consiste em três resistores $ 5K \ Omega $ que são conectados em série entre a tensão de alimentação $ V_ {cc} $ e o aterramento.

Esta rede fornece uma tensão de $ \ frac {V_ {cc}} {3} $ entre um ponto e o terra, se existir apenas um resistor $ 5K \ Omega $. Da mesma forma, ele fornece uma tensão de $ \ frac {2V_ {cc}} {3} $ entre um ponto e o aterramento, se houver apenas dois resistores $ 5K \ Omega $.

Comparador

O diagrama funcional de um 555 Timer IC consiste em dois comparadores: um Comparador Superior (UC) e um Comparador Inferior (LC).

Lembre-se de que um comparator compara as duas entradas que são aplicadas a ele e produz uma saída.

Se a tensão presente no terminal não inversor de um amplificador operacional for maior do que a tensão presente em seu terminal inversor, a saída do comparador será $ + V_ {sat} $. Isso pode ser considerado comoLogic High ('1') em representação digital.

Se a tensão presente no terminal não inversor do amplificador operacional for menor ou igual à tensão em seu terminal inversor, a saída do comparador será $ -V_ {sat} $. Isso pode ser considerado comoLogic Low ('0') em representação digital.

SR Flip-Flop

Lembre-se de que um SR flip-flopopera com transições de clock positivas ou negativas. Possui duas entradas: S e R, e duas saídas: Q (t) e Q (t) '. As saídas, Q (t) e Q (t) 'são complementares entre si.

A tabela a seguir mostra o state table de um flip-flop SR

| S | R | Q (t + 1) |

|---|---|---|

| 0 | 0 | Q (t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | - |

Aqui, Q (t) e Q (t + 1) são o estado presente e o próximo estado, respectivamente. Portanto, SR flip-flop pode ser usado para uma dessas três funções, como Hold, Reset e Set com base nas condições de entrada, quando a transição positiva (negativa) do sinal de clock é aplicada.

As saídas do Comparador Inferior (LC) e Comparador Superior (UC) são aplicadas como inputs of SR flip-flop como mostrado no diagrama funcional de 555 Timer IC.

Transistores e Inversor

O diagrama funcional de um 555 Timer IC consiste em um transistor npn $ Q_ {1} $ e um transistor pnp $ Q_ {2} $. O transistor npn $ Q_ {1} $ será ligado se sua base para a voltagem do emissor for positiva e maior que a voltagem de ativação. Caso contrário, ele será DESLIGADO.

O transistor pnp $ Q_ {2} $ é usado como buffer para isolar a entrada de reset do flip-flop SR e do transistor npn $ Q_ {1} $.

o inverter usado no diagrama funcional de um 555 Timer IC não apenas executa a ação de inversão, mas também amplifica o nível de potência.

O 555 Timer IC pode ser usado em operação mono estável para produzir um pulso na saída. Da mesma forma, ele pode ser usado em operação astável para produzir uma onda quadrada na saída.