Circuito de bloqueio de fase IC

Loop de bloqueio de fase (PLL)é um dos blocos vitais em sistemas lineares. É útil em sistemas de comunicação como radares, satélites, FMs, etc.

Este capítulo discute sobre o diagrama de blocos de PLL e IC 565 em detalhes.

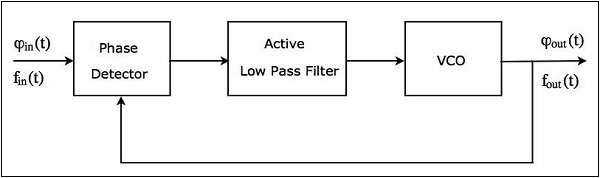

Diagrama de Bloco de PLL

Um Loop Bloqueado por Fase (PLL) consiste principalmente no seguinte three blocks -

- Detector de Fase

- Filtro passa-baixo ativo

- Oscilador de tensão controlada (VCO)

o block diagram de PLL é mostrado na figura a seguir -

A saída de um detector de fase é aplicada como uma entrada do filtro passa-baixo ativo. Da mesma forma, a saída do filtro passa-baixo ativo é aplicada como uma entrada de VCO.

o working de um PLL é o seguinte -

Phase detector produz uma tensão CC, que é proporcional à diferença de fase entre o sinal de entrada com frequência $ f_ {in} $ e o sinal de feedback (saída) com frequência $ f_ {out} $.

UMA Phase detector é um multiplicador e produz dois componentes de frequência em sua saída - soma das frequências $ f_ {in} $ e $ f_ {out} $ e diferença de frequências $ f_ {in} $ & $ f_ {out} $.

A active low pass filterproduz uma tensão DC em sua saída, após eliminar o componente de alta frequência presente na saída do detector de fase. Também amplifica o sinal.

UMA VCOproduz um sinal com uma determinada frequência, quando não há nenhuma entrada aplicada a ele. Esta frequência pode ser mudada para qualquer um dos lados aplicando uma tensão DC a ela. Portanto, o desvio de frequência é diretamente proporcional à tensão CC presente na saída de um filtro passa-baixa.

As operações acima ocorrem até que a frequência do VCO seja igual à frequência do sinal de entrada. Com base no tipo de aplicação, podemos usar a saída do filtro passa-baixo ativo ou a saída de um VCO. PLLs são usados em muitosapplications como demodulador FM, gerador de relógio, etc.

PLL opera em um dos following three modes -

- Modo de corrida livre

- Modo de captura

- Modo de bloqueio

Inicialmente, PLL opera em free running modequando nenhuma entrada é aplicada a ele. Quando um sinal de entrada com alguma frequência é aplicado ao PLL, a frequência do sinal de saída do VCO começa a mudar. Nesta fase, o PLL está operando nocapture mode. A frequência do sinal de saída do VCO mudará continuamente até que seja igual à frequência do sinal de entrada. Agora, diz-se que o PLL está operando nolock mode.

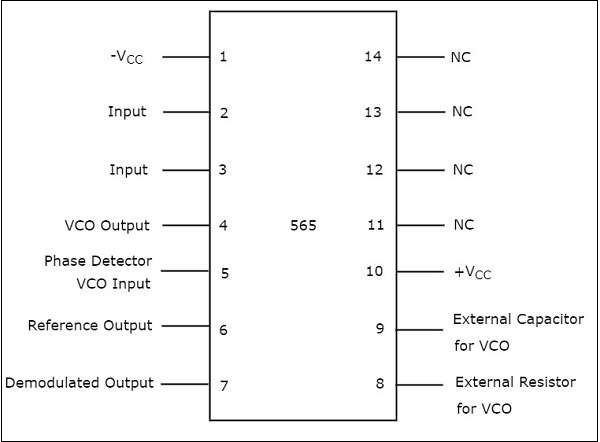

IC 565

IC 565 é o circuito integrado de bloqueio de fase mais comumente usado. É um pacote Dual-Inline (DIP) de 14 pinos. opin diagram de IC 565 é mostrado na figura a seguir -

A finalidade de cada pino é autoexplicativa no diagrama acima. Dos 14 pinos, apenas 10 pinos (pino número 1 a 10) são utilizados para a operação do PLL. Portanto, os 4 pinos restantes (pino número 11 a 14) são rotulados com NC (sem conexão).

o VCOproduz uma saída no pino número 4 do IC 565, quando os pinos 2 e 3 são aterrados. Matematicamente, podemos escrever a frequência de saída, $ f_ {out} $ do VCO como.

$$ f_ {out} = \ frac {0,25} {R_VC_V} $$

Onde,

$ R_ {V} $ é o resistor externo que está conectado ao pino número 8

$ C_ {V} $ é o capacitor externo que está conectado ao pino número 9

Ao escolher os valores adequados de $ R_ {V} $ e $ C_ {V} $, podemos fixar (determinar) a frequência de saída, $ f_ {out} $ de VCO.

Pin numbers 4 and 5devem ser encurtados com um fio externo para que a saída do VCO possa ser aplicada como uma das entradas do detector de fase.

IC 565 tem uma resistência interna de $ 3,6K \ Omega $. Um capacitor C deve ser conectado entre os pinos 7 e 10 para fazer umlow pass filter com essa resistência interna.

Observe que, de acordo com o requisito, temos que configurar corretamente os pinos do IC 565.