VLSI Tasarımı - FPGA Teknolojisi

FPGA - Giriş

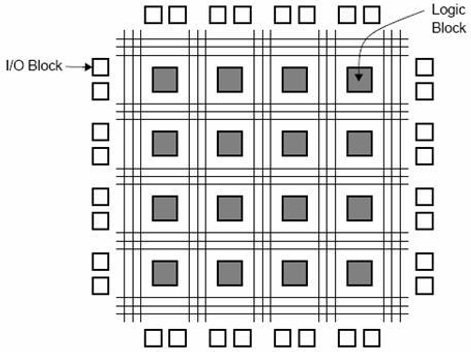

Tam formu FPGA dır-dir "Field Programmable Gate Array”. Programlanabilir ara bağlantıya sahip on binden bir milyona kadar mantık kapısı içerir. Kullanıcıların veya tasarımcıların belirli işlevleri kolayca gerçekleştirmeleri için programlanabilir ara bağlantılar mevcuttur. Tipik bir model FPGA yongası verilen şekilde gösterilmektedir. İşleve göre tasarlanmış ve numaralandırılmış I / O blokları vardır. Her mantık seviyesi kompozisyon modülü için,CLB’s (Configurable Logic Blocks).

CLB, modüle verilen lojik işlemi gerçekleştirir. CLB ve G / Ç blokları arasındaki ara bağlantı, yatay yönlendirme kanalları, dikey yönlendirme kanalları ve PSM (Programlanabilir Çoklayıcılar) yardımıyla yapılır.

İçerdiği CLB sayısı yalnızca FPGA'nın karmaşıklığına karar verir. CLB'lerin ve PSM'nin işlevselliği, VHDL veya diğer herhangi bir donanım tanımlama dili ile tasarlanmıştır. Programlamadan sonra CLB ve PSM çip üzerine yerleştirilir ve yönlendirme kanalları ile birbirine bağlanır.

Avantajlar

- Çok az zaman gerektirir; tasarım sürecinden işlevsel yongaya kadar.

- Hiçbir fiziksel üretim adımı içermez.

- Tek dezavantajı, diğer stillere göre maliyetli olmasıdır.

Kapı Dizisi Tasarımı

gate array (GA)hızlı prototipleme kabiliyeti açısından FPGA'dan sonra ikinci sırada yer almaktadır. Kullanıcı programlaması FPGA yongasının tasarım uygulaması için önemliyken, GA için metal maske tasarımı ve işleme kullanılır. Kapı dizisi uygulaması, iki aşamalı bir üretim süreci gerektirir.

İlk aşama, her GA yongasında bir dizi bağlı olmayan transistörle sonuçlanır. Bu taahhüt edilmeyen yongalar, dizinin transistörleri arasındaki metal ara bağlantıların tanımlanmasıyla tamamlanan daha sonra özelleştirme için saklanabilir. Metalik ara bağlantıların modellemesi, çip üretim sürecinin sonunda yapılır, böylece geri dönüş süresi birkaç günden birkaç haftaya kadar kısa olabilir. Aşağıda verilen şekil, kapı dizisi uygulaması için temel işlem adımlarını gösterir.

Tipik geçit dizisi platformları, MOS transistörlerinin satırları veya sütunları arasında hücreler arası yönlendirme için kanal adı verilen özel alanlar kullanır. Ara bağlantıları basitleştirir. Temel mantık kapılarını gerçekleştiren ara bağlantı modelleri bir kitaplıkta saklanır ve bu daha sonra netlist'e göre bağlanmamış transistörlerin sıralarını özelleştirmek için kullanılabilir.

Modern GA'ların çoğunda, kanal yönlendirme için birden fazla metal katman kullanılır. Birden fazla birbirine bağlı katmanın kullanılmasıyla, yönlendirme aktif hücre alanları üzerinden gerçekleştirilebilir; böylece yönlendirme kanalları Sea-of-Gates (SOG) yongalarında olduğu gibi kaldırılabilir. Burada, tüm yonga yüzeyi taahhüt edilmeyen nMOS ve pMOS transistörlerle kaplıdır. Komşu transistörler, temel mantık kapılarını oluşturmak için metal bir maske kullanılarak özelleştirilebilir.

Hücreler arası yönlendirme için, taahhüt edilmeyen transistörlerin bir kısmı feda edilmelidir. Bu tasarım stili, ara bağlantılar için daha fazla esneklik ve genellikle daha yüksek yoğunlukta sonuçlanır. GA yonga kullanım faktörü, kullanılan yonga alanının toplam yonga alanına bölünmesiyle ölçülür. FPGA'ninkinden daha yüksek ve çip hızı da öyle.

Standart Hücre Tabanlı Tasarım

Standart hücre tabanlı bir tasarım, tam bir özel maske setinin geliştirilmesini gerektirir. Standart hücre aynı zamanda polikel olarak da bilinir. Bu yaklaşımda, yaygın olarak kullanılan tüm mantık hücreleri, standart bir hücre kitaplığında geliştirilir, karakterize edilir ve saklanır.

Bir kitaplık, eviriciler, NAND geçitleri, NOR geçitleri, karmaşık AOI, OAI geçitleri, D-mandalları ve Flip-floplar dahil olmak üzere birkaç yüz hücre içerebilir. Her bir geçit tipi, farklı yayılmalar için yeterli sürüş kabiliyeti sağlamak üzere çeşitli versiyonlarda uygulanabilir. İnvertör geçidi standart boyuta, çift boyuta ve dörtlü boyuta sahip olabilir, böylece çip tasarımcısı yüksek devre hızı ve düzen yoğunluğu elde etmek için uygun boyutu seçebilir.

Her hücre, aşağıdaki gibi birkaç farklı karakterizasyon kategorisine göre karakterize edilir:

- Yük kapasitansına karşı gecikme süresi

- Devre simülasyon modeli

- Zamanlama simülasyon modeli

- Hata simülasyon modeli

- Yer ve rota için hücre verileri

- Verileri maskeleyin

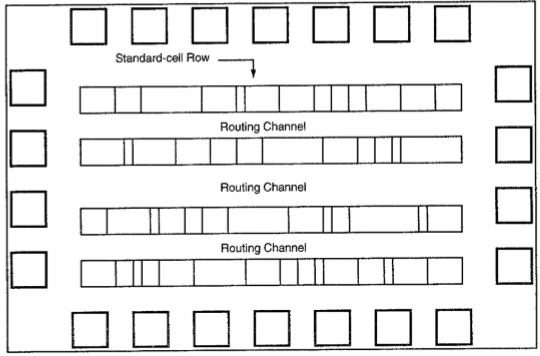

Hücrelerin otomatik olarak yerleştirilmesi ve yönlendirilmesi için, her hücre düzeni sabit bir yükseklikte tasarlanır, böylece bir dizi hücre yan yana sıralar oluşturacak şekilde sınırlanabilir. Güç ve yer rayları hücrenin üst ve alt sınırlarına paralel uzanır. Böylece, komşu hücreler ortak bir güç veri yolu ve ortak bir yer veri yolunu paylaşır. Aşağıda gösterilen şekil, standart hücre tabanlı tasarım için bir kat planıdır.

Tam Özel Tasarım

Tamamen özel bir tasarımda, tüm maske tasarımı herhangi bir kitaplık kullanılmadan yeni yapılır. Bu tasarım stilinin geliştirme maliyeti artıyor. Bu nedenle, tasarımın yeniden kullanımı kavramı, tasarım döngüsü süresini ve geliştirme maliyetini azaltmak için ün kazanmaktadır.

En zor tam özel tasarım, statik veya dinamik bir bellek hücresinin tasarımı olabilir. Mantıksal çip tasarımı için, aynı çip üzerindeki farklı tasarım stillerinin bir kombinasyonu kullanılarak iyi bir görüşme elde edilebilir, yani standart hücreler, veri yolu hücreleri veprogrammable logic arrays (PLAs).

Pratik olarak tasarımcı, her transistörün geometrisini, yönünü ve yerleşimini tam özel düzenini yapar. Tasarım verimliliği genellikle çok düşüktür; tipik olarak tasarımcı başına günde birkaç onlarca transistör. Dijital CMOS VLSI'de, yüksek işçilik maliyeti nedeniyle tam özel tasarım neredeyse hiç kullanılmaz. Bu tasarım stilleri, bellek yongaları, yüksek performanslı mikroişlemciler ve FPGA gibi yüksek hacimli ürünlerin tasarımını içerir.