Mạch logic MOS kết hợp

Các mạch hoặc cổng logic kết hợp, thực hiện các phép toán Boolean trên nhiều biến đầu vào và xác định đầu ra dưới dạng hàm Boolean của đầu vào, là các khối xây dựng cơ bản của tất cả các hệ thống kỹ thuật số. Chúng tôi sẽ xem xét các cấu hình mạch đơn giản như cổng NAND và cổng NOR hai đầu vào và sau đó mở rộng phân tích của chúng tôi sang các trường hợp tổng quát hơn của cấu trúc mạch nhiều đầu vào.

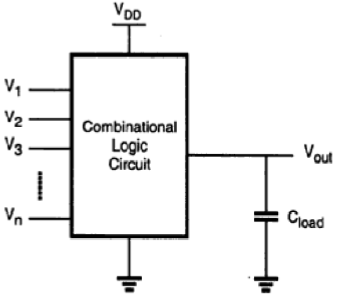

Tiếp theo, các mạch logic CMOS sẽ được trình bày theo cách tương tự. Chúng tôi sẽ nhấn mạnh những điểm giống và khác nhau giữa logic tải cạn nMOS và mạch logic CMOS và chỉ ra những ưu điểm của cổng CMOS với các ví dụ. Ở dạng tổng quát nhất của nó, một mạch logic tổ hợp, hoặc cổng, thực hiện một hàm Boolean có thể được biểu diễn dưới dạng hệ thống nhiều đầu vào, một đầu ra, như được mô tả trong hình.

Điện áp nút, được tham chiếu đến điện thế đất, đại diện cho tất cả các biến đầu vào. Sử dụng quy ước logic dương, giá trị Boolean (hoặc logic) của "1" có thể được biểu diễn bằng điện áp cao của VDD và giá trị Boolean (hoặc logic) của "0" có thể được biểu diễn bằng điện áp thấp là 0. Đầu ra nút được nạp một điện dung C L , biểu thị điện dung tổng hợp của thiết bị ký sinh trong mạch.

Mạch logic CMOS

CMOS Hai cổng NOR đầu vào

Đoạn mạch gồm một n thuần mắc song song và một p thuần phụ mắc nối tiếp. Các điện áp đầu vào V X và V Y được áp dụng cho các cổng của một bóng bán dẫn nMOS và một bóng bán dẫn pMOS.

Khi một hoặc cả hai đầu vào ở mức cao, tức là khi n-net tạo ra một đường dẫn giữa nút đầu ra và mặt đất, thì p-net bị cắt. Nếu cả hai điện áp đầu vào đều thấp, tức là lưới n bị cắt, thì lưới p tạo ra một đường dẫn giữa nút đầu ra và điện áp nguồn.

Đối với bất kỳ kết hợp đầu vào nhất định nào, cấu trúc mạch bổ sung sao cho đầu ra được kết nối với V DD hoặc nối đất qua đường dẫn có điện trở thấp và đường dẫn dòng điện một chiều giữa V DD và đất không được thiết lập cho bất kỳ kết hợp đầu vào nào. Điện áp đầu ra của CMOS, hai cổng NOR đầu vào sẽ nhận được điện áp logic-thấp là V OL = 0 và điện áp cao-logic là V OH = V DD . Phương trình của điện áp ngưỡng chuyển mạch thứ V được cho bởi

$$V_{th}\left ( NOR2 \right ) = \frac{V_{T,n}+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}}}$$

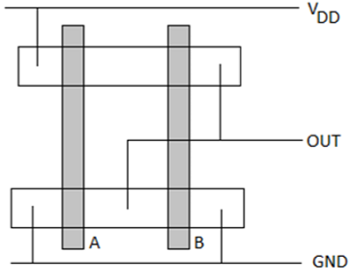

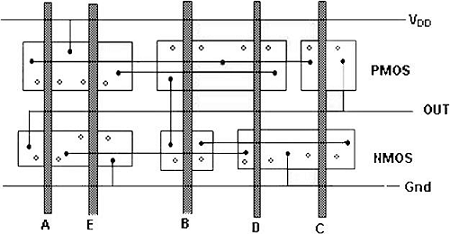

Cách bố trí Cổng NOR 2 đầu vào CMOS

Hình bên cho thấy sơ đồ bố trí mẫu của cổng NOR 2 đầu vào CMOS, sử dụng kim loại một lớp và polysilicon một lớp. Các tính năng của bố cục này là -

- Nhiều đường thẳng đứng đơn cho mỗi đầu vào

- Các hình dạng hoạt động đơn lẻ cho các thiết bị N và P, tương ứng

- Xe buýt kim loại chạy ngang

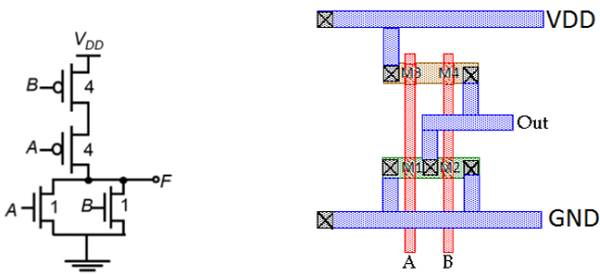

Sơ đồ thanh cho cổng CMOS N0R2 được hiển thị trong hình bên dưới; tương ứng trực tiếp với bố cục, nhưng không chứa thông tin W và L. Các khu vực khuếch tán được mô tả bằng các hình chữ nhật, các kết nối kim loại và các đường liền nét và vòng tròn, tương ứng đại diện cho các điểm tiếp xúc, và các dải gạch chéo đại diện cho các cột đa giác. Sơ đồ thanh rất hữu ích để lập kế hoạch cấu trúc liên kết bố cục tối ưu.

Cổng NAND hai đầu vào CMOS

Sơ đồ mạch của hai cổng CMOS NAND đầu vào được cho trong hình bên dưới.

Nguyên tắc hoạt động của mạch là kép chính xác của hoạt động NOR hai đầu vào CMOS. N - net bao gồm hai bóng bán dẫn nMOS mắc nối tiếp tạo ra một đường dẫn giữa nút đầu ra và mặt đất, nếu cả hai điện áp đầu vào đều ở mức logic cao. Cả hai bóng bán dẫn pMOS được kết nối song song trong p-net sẽ bị tắt.

Đối với tất cả các kết hợp đầu vào khác, một hoặc cả hai bóng bán dẫn pMOS sẽ được BẬT, trong khi p-net bị ngắt, do đó, tạo ra một đường dẫn dòng điện giữa nút đầu ra và điện áp nguồn cung cấp. Ngưỡng chuyển đổi cho cổng này nhận được là:

$$V_{th}\left ( NAND2 \right ) = \frac{V_{T,n}+2\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+2\sqrt{\frac{k_{p}}{k_{n}}}}$$

Các tính năng của bố cục này như sau:

- Các đường polysilicon đơn cho đầu vào chạy theo chiều dọc trên cả vùng hoạt động N và P.

- Các hình dạng hoạt động đơn được sử dụng để xây dựng cả thiết bị nMOS và cả thiết bị pMOS.

- Đường dẫn điện chạy ngang trên cùng và dưới cùng của bố cục.

- Dây đầu ra chạy ngang để dễ dàng kết nối với mạch lân cận.

Mạch logic phức tạp

Cổng logic phức tạp tải cạn NMOS

Để thực hiện các chức năng phức tạp của nhiều biến đầu vào, các cấu trúc mạch cơ bản và nguyên tắc thiết kế được phát triển cho NOR và NAND có thể được mở rộng đến các cổng logic phức tạp. Khả năng nhận ra các chức năng logic phức tạp, sử dụng một số lượng nhỏ bóng bán dẫn là một trong những đặc điểm hấp dẫn nhất của mạch logic nMOS và CMOS. Hãy xem xét hàm Boolean sau đây làm ví dụ.

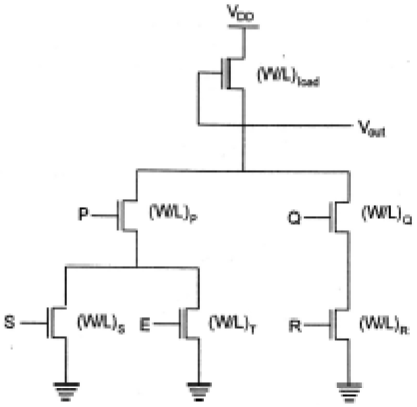

$$\overline{Z=P\left ( S+T \right )+QR}$$

Cổng logic phức tạp tải cạn nMOS được sử dụng để thực hiện chức năng này được thể hiện trong hình. Trong hình này, nhánh trình điều khiển nMOS bên trái của ba bóng bán dẫn trình điều khiển được sử dụng để thực hiện chức năng logic P (S + T), trong khi nhánh bên phải thực hiện chức năng QR. Bằng cách kết nối hai nhánh song song và bằng cách đặt bóng bán dẫn tải giữa nút đầu ra và điện áp cung cấpVDD,chúng ta có được hàm phức đã cho. Mỗi biến đầu vào chỉ được gán cho một trình điều khiển.

Kiểm tra cấu trúc liên kết mạch cung cấp các nguyên tắc thiết kế đơn giản của mạng kéo xuống -

- Các hoạt động HOẶC được thực hiện bởi các trình điều khiển được kết nối song song.

- Các hoạt động AND được thực hiện bởi các trình điều khiển được kết nối loạt.

- Đảo ngược được cung cấp bởi bản chất của hoạt động mạch MOS.

Nếu tất cả các biến đầu vào có mức logic cao trong mạch nhận ra chức năng, trình điều khiển tương đương (W/L) tỷ lệ của mạng kéo xuống bao gồm năm bóng bán dẫn nMOS là

$$\frac{W}{L}=\frac{1}{\frac{1}{\left ( W/L \right )Q}+\frac{1}{\left ( W/L \right )R}}+\frac{1}{\frac{1}{\left ( W/L \right )P}+\frac{1}{\left ( W/L \right )S+\left ( W/L \right )Q}}$$

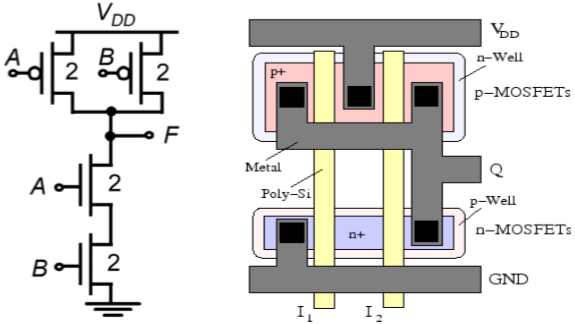

Cổng logic CMOS phức tạp

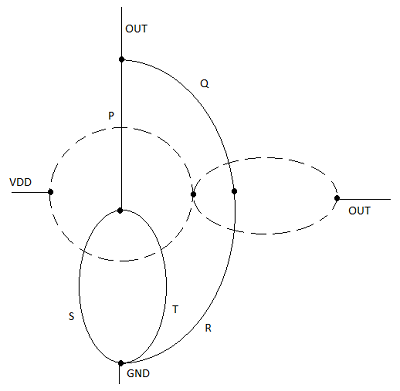

Việc thực hiện mạng n-net, hay mạng kéo xuống, dựa trên cùng các nguyên tắc thiết kế cơ bản được kiểm tra đối với cổng logic phức tạp tải suy giảm nMOS. Mạng kéo lên pMOS phải là mạng kép của n-net.

Nó có nghĩa là tất cả các kết nối song song trong mạng nMOS sẽ tương ứng với kết nối nối tiếp trong mạng pMOS và tất cả kết nối nối tiếp trong mạng nMOS tương ứng với kết nối song song trong mạng pMOS. Hình bên cho thấy một cách xây dựng đơn giản của đồ thị p-net (kéo lên) từ đồ thị n-net (kéo xuống).

Mỗi bóng bán dẫn trình điều khiển trong mạng kéo xuống được hiển thị bằng ai và mỗi nút được hiển thị bằng một đỉnh trong đồ thị kéo xuống. Tiếp theo, một đỉnh mới được tạo trong mỗi vùng giới hạn trong đồ thị kéo và các đỉnh lân cận được nối với nhau bằng các cạnh mà chỉ vượt qua mỗi cạnh trong đồ thị kéo xuống một lần. Biểu đồ mới này cho thấy mạng kéo lên.

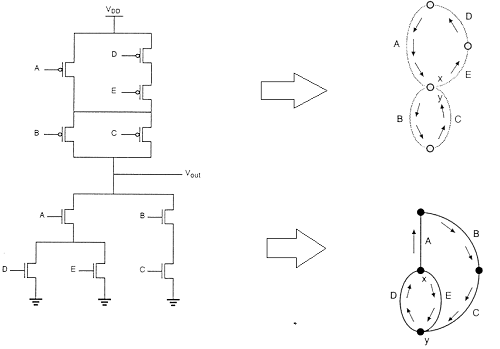

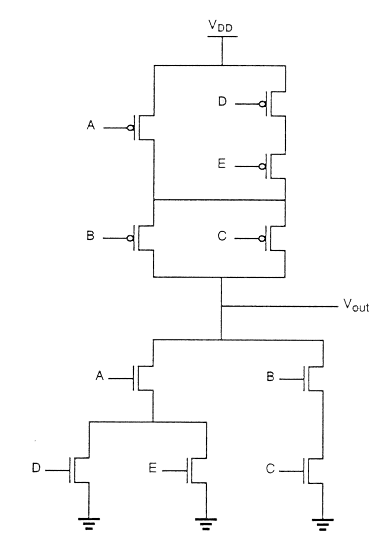

Kỹ thuật bố cục sử dụng phương pháp đồ thị Euler

Hình bên cho thấy việc triển khai CMOS của một chức năng phức tạp và sơ đồ thanh của nó được thực hiện với thứ tự cổng tùy ý mang lại bố cục không tối ưu cho cổng CMOS.

Trong trường hợp này, sự phân tách giữa các cột polysilicon phải cho phép phân tách khuếch tán-todiffusion ở giữa. Điều này chắc chắn tiêu tốn một lượng đáng kể diện tích silicon bổ sung.

Bằng cách sử dụng đường dẫn Euler, chúng ta có thể có được một bố cục tối ưu. Đường Euler được định nghĩa là một đường liên tục đi qua mỗi cạnh (nhánh) của biểu đồ đúng một lần. Tìm đường dẫn Euler trong cả biểu đồ cây kéo xuống và đồ thị cây kéo lên với thứ tự đầu vào giống hệt nhau.