Thiết kế VLSI - Mạch logic MOS tuần tự

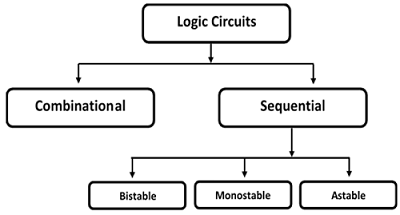

Mạch logic được chia thành hai loại - (a) Mạch kết hợp, và (b) Mạch tuần tự.

Trong mạch Kết hợp, đầu ra chỉ phụ thuộc vào điều kiện của đầu vào mới nhất.

Trong các mạch Tuần tự, đầu ra không chỉ phụ thuộc vào các đầu vào mới nhất mà còn phụ thuộc vào điều kiện của các đầu vào trước đó. Các mạch tuần tự chứa các phần tử nhớ.

Mạch tuần tự có ba loại:

Bistable- Mạch điện sử dụng có hai điểm hoạt động ổn định và sẽ ở một trong hai trạng thái. Ví dụ - Các ô nhớ, chốt, flip-flop và thanh ghi.

Monostable- Các mạch đơn ổn chỉ có một điểm hoạt động ổn định và ngay cả khi chúng bị xáo trộn tạm thời sang trạng thái ngược lại, chúng sẽ kịp thời quay trở lại điểm hoạt động ổn định. Ví dụ: Bộ định thời, bộ tạo xung.

Astable- mạch không có điểm hoạt động ổn định và dao động giữa một số trạng thái. Ví dụ - Bộ dao động vòng.

Mạch logic CMOS

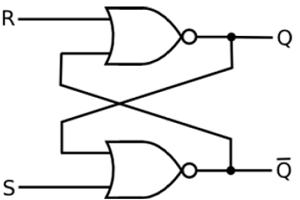

SR Latch dựa trên Cổng NOR

Nếu đầu vào đã đặt (S) bằng logic "1" và đầu vào đặt lại bằng logic "0." thì đầu ra Q sẽ buộc phải logic "1". Trong khi $ \ overline {Q} $ buộc phải logic"0". Điều này có nghĩa là chốt SR sẽ được thiết lập, bất kể trạng thái trước đó của nó.

Tương tự, nếu S bằng "0" và R bằng "1" thì đầu ra Q sẽ buộc phải "0" trong khi $ \ overline {Q} $ buộc phải "1". Điều này có nghĩa là chốt được đặt lại, bất kể trạng thái được giữ trước đó của nó. Cuối cùng, nếu cả hai đầu vào S và R bằng logic"1" thì cả hai đầu ra sẽ được buộc phải logic "0" mâu thuẫn với sự bổ sung của Q và $ \ overline {Q} $.

Do đó, kết hợp đầu vào này không được phép trong quá trình hoạt động bình thường. Bảng chân trị của chốt SR dựa trên NOR được đưa ra trong bảng.

| S | R | Q | $ \ overline {Q} $ | Hoạt động |

|---|---|---|---|---|

| 0 | 0 | Q | $ \ overline {Q} $ | Giữ |

| 1 | 0 | 1 | 0 | Bộ |

| 0 | 1 | 0 | 1 | Cài lại |

| 1 | 1 | 0 | 0 | Không cho phép |

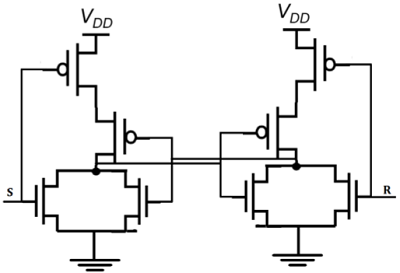

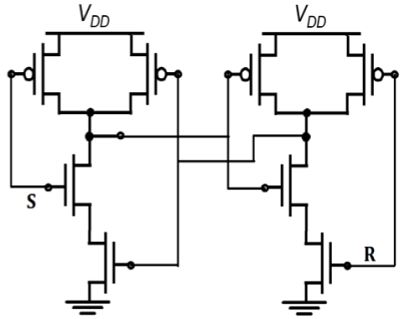

Chốt CMOS SR dựa trên cổng NOR được hiển thị trong hình bên dưới.

Nếu S bằng V OH và R bằng V OL thì cả hai bóng bán dẫn mắc song song M1 và M2 sẽ ON. Điện áp trên nút $ \ overline {Q} $ sẽ giả định mức logic thấp là V OL = 0.

Đồng thời, cả M3 và M4 đều bị tắt, dẫn đến điện áp cao logic V OH tại nút Q. Nếu R bằng V OH và S bằng V OL , M1 và M2 bị tắt và M3 và M4 đã bật.

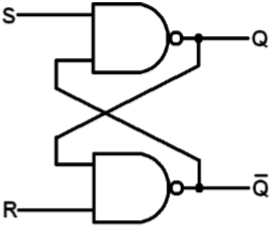

SR Latch dựa trên Cổng NAND

Sơ đồ khối và sơ đồ mức cổng của chốt SR dựa trên NAND được thể hiện trong hình. Các vòng tròn nhỏ ở các cực đầu vào S và R biểu thị rằng mạch phản ứng với các tín hiệu đầu vào thấp đang hoạt động. Bảng sự thật của chốt SR dựa trên NAND được đưa ra trong bảng

| S | R | Q | Q ′ | |

| 0 | 0 | NC | NC | Không thay đổi. Chốt vẫn ở trạng thái hiện tại. |

| 1 | 0 | 1 | 0 | Latch SET. |

| 0 | 1 | 0 | 1 | Chốt ĐẶT LẠI. |

| 1 | 1 | 0 | 0 | Điều kiện không hợp lệ. |

Nếu S về 0 (trong khi R = 1), Q lên cao, kéo $ \ overline {Q} $ xuống thấp và chốt chuyển sang trạng thái Đặt

S = 0 thì Q = 1 (nếu R = 1)

Nếu R về 0 (trong khi S = 1), Q lên cao, kéo $ \ overline {Q} $ xuống thấp và chốt được Đặt lại

R = 0 thì Q = 1 (nếu S = 1)

Trạng thái giữ yêu cầu cả S và R phải cao. Nếu S = R = 0 thì đầu ra không được phép, vì nó sẽ dẫn đến trạng thái không xác định. CMOS SR Latch dựa trên Cổng NAND được thể hiện trong hình.

Chốt nMOS SR cạn kiệt tải dựa trên Cổng NAND được thể hiện trong hình. Hoạt động tương tự như của chốt CMOS NAND SR. Việc triển khai mạch CMOS có mức tiêu tán công suất tĩnh thấp và biên độ nhiễu cao.

Mạch logic CMOS

Chốt SR được khóa

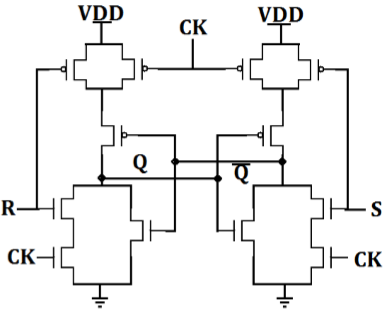

Hình cho thấy chốt SR dựa trên NOR có thêm đồng hồ. Chốt chỉ đáp ứng với đầu vào S và R khi CLK cao.

Khi CLK thấp, chốt giữ nguyên trạng thái hiện tại của nó. Quan sát Q thay đổi trạng thái -

- Khi S tăng cao trong CLK dương.

- Trên cạnh CLK hàng đầu sau những thay đổi trong S & R trong thời gian CLK thấp.

- Một trục trặc tích cực trong S trong khi CLK cao

- Khi R tăng cao trong CLK tích cực.

Việc triển khai CMOS AOI của chốt SR dựa trên NOR xung nhịp được thể hiện trong hình. Lưu ý rằng chỉ cần 12 bóng bán dẫn.

Khi CLK ở mức thấp, hai đầu nối tiếp trong cây N mở và hai bóng bán dẫn song song trong cây P được BẬT, do đó vẫn giữ trạng thái trong ô nhớ.

Khi xung nhịp cao, mạch đơn giản trở thành chốt CMOS dựa trên NOR sẽ phản hồi với đầu vào S và R.

Clocked SR Latch based on NAND Gate

Mạch được thực hiện với bốn cổng NAND. Nếu mạch này được thực hiện với CMOS thì nó yêu cầu 16 bóng bán dẫn.

- Chốt chỉ phản hồi S hoặc R nếu CLK cao.

- Nếu cả tín hiệu đầu vào và tín hiệu CLK đều ở mức cao: tức là, đầu ra chốt Q sẽ được đặt khi CLK = "1" S = "1" và R = "0"

- Tương tự, chốt sẽ được đặt lại khi CLK = "1," S = "0" và

Khi CLK thấp, chốt giữ nguyên trạng thái hiện tại.

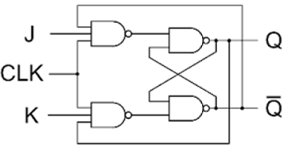

Chốt JK được khóa

Hình trên cho thấy một chốt JK có xung nhịp, dựa trên các cổng NAND. Nhược điểm của chốt SR là khi cả S và R đều ở mức cao, trạng thái đầu ra của nó trở nên không xác định. Chốt JK loại bỏ vấn đề này bằng cách sử dụng phản hồi từ đầu ra đến đầu vào, sao cho tất cả các trạng thái đầu vào của bảng chân trị đều cho phép. Nếu J = K = 0, chốt sẽ giữ trạng thái hiện tại.

Nếu J = 1 và K = 0, chốt sẽ đặt ở cạnh đồng hồ dương tiếp theo, tức là Q = 1, $ \ overline {Q} $ = 0

Nếu J = 0 và K = 1, chốt sẽ đặt lại trên cạnh đồng hồ dương tiếp theo, tức là Q = 1 và $ \ overline {Q} $ = 0.

Nếu J = K = 1, chốt sẽ bật tắt trên cạnh đồng hồ dương tiếp theo

Hoạt động của chốt JK đồng hồ được tóm tắt trong bảng sự thật được đưa ra trong bảng.

J |

K |

Q |

$ \ overline {Q} $ | S |

R |

Q |

$ \ overline {Q} $ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Giữ |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | Cài lại |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | Bộ |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | chuyển đổi |

| 1 | 0 | 1 | 0 | 0 | 1 |

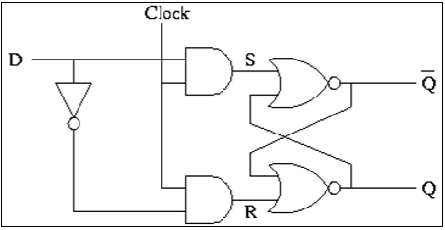

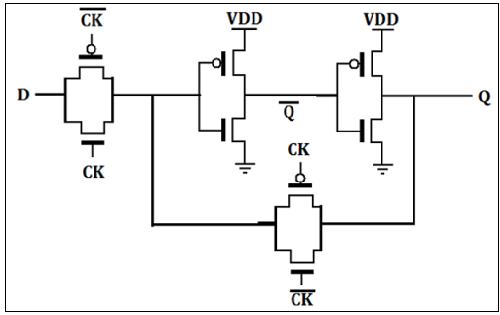

Triển khai chốt CMOS D

Chốt D thông thường, được thực hiện với các công tắc cổng truyền (TG) như thể hiện trong hình. TG đầu vào được kích hoạt với CLK trong khi TG vòng phản hồi chốt được kích hoạt với CLK. Đầu vào D được chấp nhận khi CLK cao. Khi CLK xuống thấp, đầu vào được mở và chốt được đặt với dữ liệu trước đó D.