Thiết kế VLSI - Giới thiệu VHDL

VHDL là viết tắt của ngôn ngữ mô tả phần cứng mạch tích hợp tốc độ rất cao. Nó là một ngôn ngữ lập trình được sử dụng để mô hình hóa hệ thống kỹ thuật số theo luồng dữ liệu, hành vi và phong cách cấu trúc của mô hình hóa. Ngôn ngữ này lần đầu tiên được giới thiệu vào năm 1981 cho Bộ Quốc phòng (DoD) theo chương trình VHSIC.

Mô tả một thiết kế

Trong VHDL một thực thể được sử dụng để mô tả một mô-đun phần cứng. Một thực thể có thể được mô tả bằng cách sử dụng,

- Khai báo thực thể

- Architecture

- Configuration

- Khai báo gói hàng

- Gói cơ thể

Hãy xem đây là những gì?

Khai báo thực thể

Nó xác định tên, tín hiệu đầu ra đầu vào và chế độ của một mô-đun phần cứng.

Syntax -

entity entity_name is

Port declaration;

end entity_name;Khai báo thực thể phải bắt đầu bằng 'thực thể' và kết thúc bằng từ khóa 'kết thúc'. Hướng sẽ là đầu vào, đầu ra hoặc inout.

| Trong | Cổng có thể được đọc |

| Ngoài | Cổng có thể được viết |

| Inout | Cổng có thể được đọc và ghi |

| Đệm | Cổng có thể được đọc và ghi, nó có thể chỉ có một nguồn. |

Architecture -

Kiến trúc có thể được mô tả bằng cách sử dụng cấu trúc, luồng dữ liệu, phong cách hành vi hoặc hỗn hợp.

Syntax -

architecture architecture_name of entity_name

architecture_declarative_part;

begin

Statements;

end architecture_name;Ở đây, chúng ta nên chỉ định tên thực thể mà chúng ta đang viết phần thân kiến trúc. Các câu lệnh kiến trúc phải nằm trong từ khóa 'begin' và 'énd'. Phần khai báo kiến trúc có thể chứa các biến, hằng số hoặc khai báo thành phần.

Mô hình luồng dữ liệu

Trong phong cách mô hình hóa này, luồng dữ liệu qua thực thể được thể hiện bằng cách sử dụng tín hiệu đồng thời (song song). Các câu lệnh đồng thời trong VHDL là WHEN và GENERATE.

Bên cạnh đó, các phép gán chỉ sử dụng toán tử (AND, NOT, +, *, sll, v.v.) cũng có thể được sử dụng để xây dựng mã.

Cuối cùng, một loại nhiệm vụ đặc biệt, được gọi là BLOCK, cũng có thể được sử dụng trong loại mã này.

Trong mã đồng thời, có thể sử dụng những điều sau:

- Operators

- Câu lệnh WHEN (WHEN / ELSE hoặc WITH / SELECT / WHEN);

- Câu lệnh GENERATE;

- Câu lệnh BLOCK

Mô hình hành vi

Trong phong cách mô hình hóa này, hành vi của một thực thể như một tập hợp các câu lệnh được thực thi tuần tự theo thứ tự đã chỉ định. Chỉ các câu lệnh được đặt bên trong PROCESS, FUNCTION hoặc PROCEDURE là tuần tự.

QUY TRÌNH, CHỨC NĂNG và THỦ TỤC là các phần mã duy nhất được thực thi tuần tự.

Tuy nhiên, về tổng thể, bất kỳ khối nào trong số này vẫn đồng thời với bất kỳ câu lệnh nào khác được đặt bên ngoài nó.

Một khía cạnh quan trọng của mã hành vi là nó không bị giới hạn ở logic tuần tự. Thật vậy, với nó, chúng ta có thể xây dựng các mạch tuần tự cũng như mạch tổ hợp.

Các câu lệnh hành vi là IF, WAIT, CASE và LOOP. BIẾN cũng bị hạn chế và chúng chỉ được sử dụng trong mã tuần tự. VARIABLE không bao giờ có thể là toàn cục, vì vậy giá trị của nó không thể được truyền trực tiếp.

Mô hình cấu trúc

Trong mô hình này, một thực thể được mô tả như một tập hợp các thành phần được kết nối với nhau. Một câu lệnh khởi tạo thành phần là một câu lệnh đồng thời. Do đó, thứ tự của các câu lệnh này không quan trọng. Phong cách cấu trúc của mô hình chỉ mô tả sự kết nối với nhau của các thành phần (được xem như hộp đen), mà không ngụ ý bất kỳ hành vi nào của bản thân các thành phần cũng như của thực thể mà chúng đại diện chung.

Trong mô hình cấu trúc, phần thân kiến trúc bao gồm hai phần - phần khai báo (trước từ khóa bắt đầu) và phần câu lệnh (sau từ khóa bắt đầu).

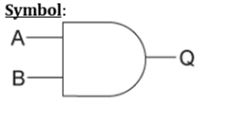

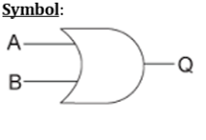

Hoạt động logic - VÀ CỔNG

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity and1 is

port(x,y:in bit ; z:out bit);

end and1;

architecture virat of and1 is

begin

z<=x and y;

end virat;Dạng sóng

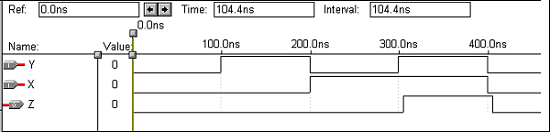

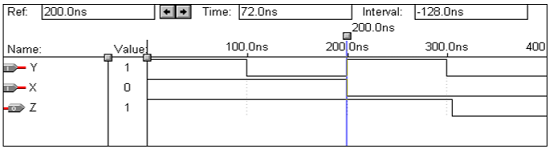

Hoạt động logic - Cổng HOẶC

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity or1 is

port(x,y:in bit ; z:out bit);

end or1;

architecture virat of or1 is

begin

z<=x or y;

end virat;Dạng sóng

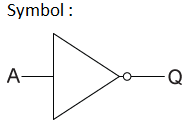

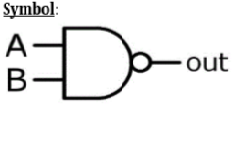

Hoạt động logic - KHÔNG phải cổng

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity not1 is

port(x:in bit ; y:out bit);

end not1;

architecture virat of not1 is

begin

y<=not x;

end virat;Dạng sóng

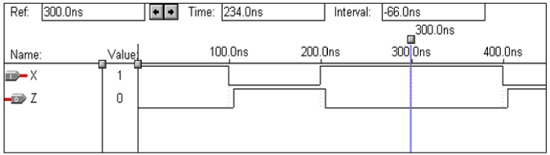

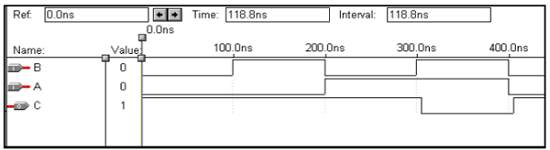

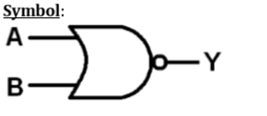

Hoạt động logic - Cổng NAND

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nand1 is

port(a,b:in bit ; c:out bit);

end nand1;

architecture virat of nand1 is

begin

c<=a nand b;

end virat;Dạng sóng

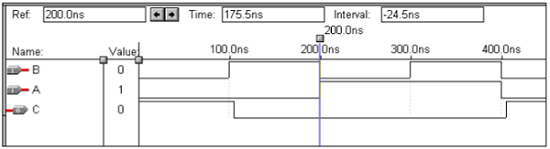

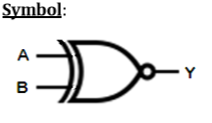

Hoạt động logic - Cổng NOR

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nor1 is

port(a,b:in bit ; c:out bit);

end nor1;

architecture virat of nor1 is

begin

c<=a nor b;

end virat;Dạng sóng

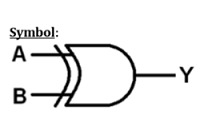

Hoạt động logic - Cổng XOR

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xor1 is

port(a,b:in bit ; c:out bit);

end xor1;

architecture virat of xor1 is

begin

c<=a xor b;

end virat;Dạng sóng

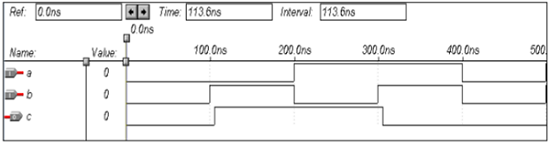

Hoạt động logic - Cổng X-NOR

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xnor1 is

port(a,b:in bit ; c:out bit);

end xnor1;

architecture virat of xnor1 is

begin

c<=not(a xor b);

end virat;Dạng sóng