Thiết kế VLSI - Công nghệ FPGA

FPGA - Giới thiệu

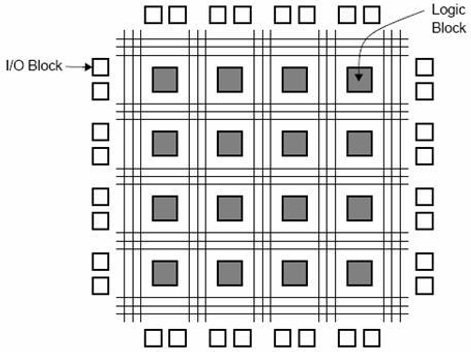

Hình thức đầy đủ của FPGA Là "Field Programmable Gate Array”. Nó chứa mười nghìn đến hơn một triệu cổng logic với khả năng kết nối có thể lập trình được. Các kết nối có thể lập trình có sẵn cho người dùng hoặc nhà thiết kế để thực hiện các chức năng nhất định một cách dễ dàng. Một chip FPGA mô hình điển hình được hiển thị trong hình bên. Có các khối I / O, được thiết kế và đánh số theo chức năng. Đối với mỗi mô-đun của thành phần mức logic, cóCLB’s (Configurable Logic Blocks).

CLB thực hiện hoạt động logic được cung cấp cho mô-đun. Kết nối giữa các khối CLB và I / O được thực hiện với sự trợ giúp của các kênh định tuyến ngang, các kênh định tuyến dọc và PSM (Bộ ghép kênh có thể lập trình).

Số lượng CLB mà nó chứa chỉ quyết định độ phức tạp của FPGA. Chức năng của CLB và PSM được thiết kế bởi VHDL hoặc bất kỳ ngôn ngữ mô tả phần cứng nào khác. Sau khi lập trình, CLB và PSM được đặt trên chip và kết nối với nhau bằng các kênh định tuyến.

Ưu điểm

- Nó đòi hỏi thời gian rất nhỏ; bắt đầu từ quy trình thiết kế đến chip chức năng.

- Không có bước sản xuất vật lý nào liên quan đến nó.

- Bất lợi duy nhất là, nó là tốn kém hơn so với các phong cách khác.

Thiết kế mảng cổng

Các gate array (GA)đứng thứ hai sau FPGA, về khả năng tạo mẫu nhanh. Trong khi lập trình của người dùng là quan trọng đối với việc triển khai thiết kế của chip FPGA, thiết kế và xử lý mặt nạ kim loại được sử dụng cho GA. Việc triển khai mảng cổng yêu cầu quy trình sản xuất hai bước.

Giai đoạn đầu tiên dẫn đến một loạt các bóng bán dẫn không được cam kết trên mỗi chip GA. Các chip không được cam kết này có thể được lưu trữ để tùy chỉnh sau này, quá trình này được hoàn thành bằng cách xác định các kết nối kim loại giữa các bóng bán dẫn của mảng. Việc tạo mẫu các mối liên kết kim loại được thực hiện ở giai đoạn cuối của quá trình chế tạo chip, do đó thời gian quay vòng vẫn có thể ngắn, vài ngày đến vài tuần. Hình dưới đây cho thấy các bước xử lý cơ bản để thực hiện mảng cổng.

Các nền tảng mảng cổng điển hình sử dụng các khu vực dành riêng được gọi là kênh, để định tuyến liên ô giữa các hàng hoặc cột của bóng bán dẫn MOS. Chúng đơn giản hóa các kết nối. Các mẫu kết nối thực hiện các cổng logic cơ bản được lưu trữ trong một thư viện, sau đó có thể được sử dụng để tùy chỉnh các hàng bóng bán dẫn không được chuyển theo danh sách mạng.

Trong hầu hết các GA hiện đại, nhiều lớp kim loại được sử dụng để định tuyến kênh. Với việc sử dụng nhiều lớp được kết nối với nhau, việc định tuyến có thể đạt được trên các vùng ô hoạt động; để có thể loại bỏ các kênh định tuyến như trong chip Sea-of-Gates (SOG). Ở đây, toàn bộ bề mặt chip được bao phủ bởi các bóng bán dẫn nMOS và pMOS không cam kết. Các bóng bán dẫn lân cận có thể được tùy chỉnh bằng cách sử dụng một mặt nạ kim loại để tạo thành các cổng logic cơ bản.

Đối với định tuyến giữa các ô, một số bóng bán dẫn không được cam kết phải được hy sinh. Phong cách thiết kế này mang lại sự linh hoạt hơn cho các kết nối và thường ở mật độ cao hơn. Hệ số sử dụng chip GA được đo bằng diện tích chip đã sử dụng chia cho tổng diện tích chip. Nó cao hơn FPGA và tốc độ chip cũng vậy.

Thiết kế dựa trên ô tiêu chuẩn

Một thiết kế dựa trên ô tiêu chuẩn yêu cầu phát triển một bộ mặt nạ tùy chỉnh đầy đủ. Tế bào tiêu chuẩn còn được gọi là polycell. Theo cách tiếp cận này, tất cả các ô logic thường được sử dụng đều được phát triển, đặc trưng và lưu trữ trong một thư viện ô tiêu chuẩn.

Một thư viện có thể chứa vài trăm ô bao gồm bộ nghịch lưu, cổng NAND, cổng NOR, AOI phức tạp, cổng OAI, chốt D và Flip-flops. Mỗi loại cổng có thể được thực hiện trong nhiều phiên bản để cung cấp khả năng dẫn động phù hợp cho các đầu ra quạt khác nhau. Cổng biến tần có thể có kích thước tiêu chuẩn, kích thước gấp đôi và kích thước gấp bốn lần để nhà thiết kế chip có thể chọn kích thước phù hợp để có được tốc độ mạch cao và mật độ bố trí.

Mỗi ô được đặc trưng theo một số loại đặc điểm khác nhau, chẳng hạn như,

- Thời gian trễ so với điện dung tải

- Mô hình mô phỏng mạch

- Mô hình mô phỏng thời gian

- Mô hình mô phỏng lỗi

- Dữ liệu di động cho địa điểm và tuyến đường

- Dữ liệu mặt nạ

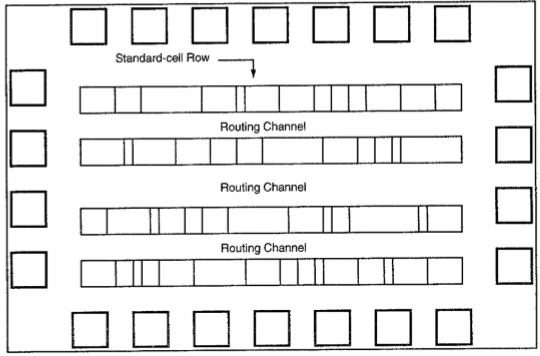

Để tự động sắp xếp các ô và định tuyến, mỗi bố cục ô được thiết kế với một chiều cao cố định, để một số ô có thể được giới hạn cạnh nhau để tạo thành các hàng. Nguồn điện và đường ray nối đất chạy song song với ranh giới trên và dưới của ô. Vì vậy, các ô lân cận chia sẻ một bus nguồn chung và một bus chung. Hình bên dưới là sơ đồ mặt bằng cho thiết kế dựa trên ô tiêu chuẩn.

Thiết kế tùy chỉnh đầy đủ

Trong một thiết kế hoàn toàn tùy chỉnh, toàn bộ thiết kế mặt nạ được tạo mới mà không cần sử dụng bất kỳ thư viện nào. Chi phí phát triển của phong cách thiết kế này đang tăng cao. Do đó, khái niệm tái sử dụng thiết kế đang trở nên nổi tiếng để giảm thời gian chu kỳ thiết kế và chi phí phát triển.

Thiết kế tùy chỉnh đầy đủ khó nhất có thể là thiết kế của một ô nhớ, có thể là tĩnh hoặc động. Đối với thiết kế chip logic, một thương lượng tốt có thể đạt được bằng cách sử dụng kết hợp các kiểu thiết kế khác nhau trên cùng một chip, tức là các ô tiêu chuẩn, ô đường dẫn dữ liệu vàprogrammable logic arrays (PLAs).

Trên thực tế, nhà thiết kế thực hiện bố cục tùy chỉnh đầy đủ, tức là hình dạng, hướng và vị trí của mọi bóng bán dẫn. Năng suất thiết kế thường rất thấp; thường là vài chục bóng bán dẫn mỗi ngày, mỗi nhà thiết kế. Trong CMOS VLSI kỹ thuật số, thiết kế tùy chỉnh hoàn toàn hầu như không được sử dụng do chi phí nhân công cao. Những phong cách thiết kế này bao gồm việc thiết kế các sản phẩm có dung lượng lớn như chip nhớ, bộ vi xử lý hiệu suất cao và FPGA.