Thiết kế VLSI - Biến tần MOS

Biến tần thực sự là hạt nhân của tất cả các thiết kế kỹ thuật số. Một khi hoạt động và đặc tính của nó được hiểu rõ ràng, việc thiết kế các cấu trúc phức tạp hơn như cổng NAND, bộ cộng, bộ nhân và bộ vi xử lý được đơn giản hóa rất nhiều. Hoạt động điện của các mạch phức tạp này có thể được suy ra gần như hoàn toàn bằng cách ngoại suy các kết quả thu được đối với biến tần.

Việc phân tích các bộ biến tần có thể được mở rộng để giải thích hoạt động của các cổng phức tạp hơn như NAND, NOR hoặc XOR, từ đó tạo thành các khối xây dựng cho các mô-đun như bộ nhân và bộ xử lý. Trong chương này, chúng tôi tập trung vào một hiện thân duy nhất của cổng biến tần, là biến tần CMOS tĩnh - hay ngắn gọn là biến tần CMOS. Điều này chắc chắn là phổ biến nhất hiện nay và do đó đáng được chúng tôi đặc biệt quan tâm.

Nguyên lý hoạt động

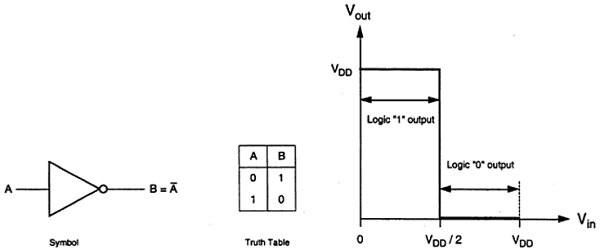

Biểu tượng logic và bảng sự thật của biến tần lý tưởng được thể hiện trong hình dưới đây. Ở đây A là đầu vào và B là đầu ra đảo ngược được biểu thị bằng điện áp nút của chúng. Sử dụng logic dương, giá trị Boolean của logic 1 được biểu thị bằng V dd và logic 0 được biểu thị bằng 0. V th là điện áp ngưỡng của bộ nghịch lưu, là V dd / 2, trong đó V dd là điện áp đầu ra.

Đầu ra được chuyển từ 0 sang V dd khi đầu vào nhỏ hơn V th . Vì vậy, đối với 0 <V trong <V thứ đầu ra bằng logic 0 đầu vào và V thứ <V trong <V dd bằng logic 1 đầu vào cho biến tần.

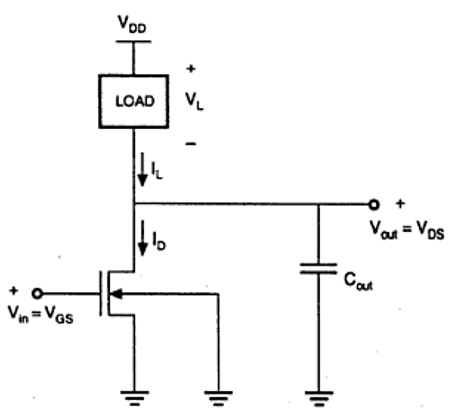

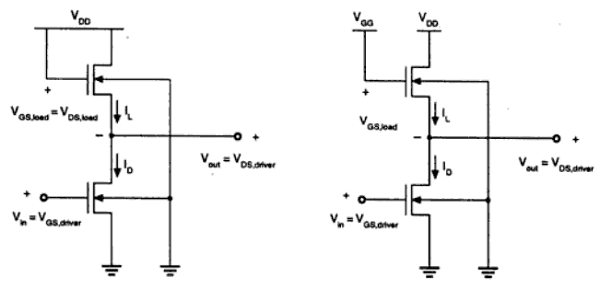

Các đặc điểm thể hiện trong hình là lý tưởng. Cấu trúc mạch tổng quát của biến tần nMOS được thể hiện trong hình bên dưới.

Từ hình cho trước, chúng ta có thể thấy rằng điện áp đầu vào của biến tần bằng cổng vào nguồn của bóng bán dẫn nMOS và điện áp đầu ra của biến tần bằng với điện áp nguồn của bóng bán dẫn nMOS. Nguồn đến điện áp nền của nMOS còn được gọi là trình điều khiển cho bóng bán dẫn được nối đất; nên V SS = 0. Nút đầu ra được nối với một điện dung gộp dùng cho VTC.

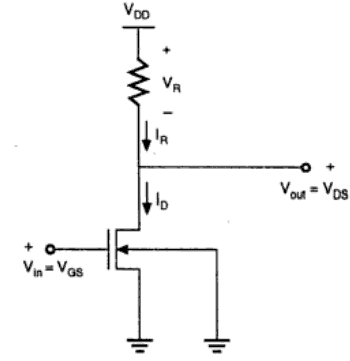

Biến tần tải điện trở

Cấu trúc cơ bản của biến tần tải điện trở được trình bày trong hình bên dưới. Ở đây, nMOS loại nâng cao hoạt động như bóng bán dẫn trình điều khiển. Tải bao gồm một đơn giản tuyến tính điện trở R L . Việc cung cấp điện của mạch là V DD và cống hiện tại tôi D là tương đương với tải trọng hiện tại tôi R .

Hoạt động mạch

Khi đầu vào của bóng bán dẫn trình điều khiển nhỏ hơn điện áp ngưỡng V TH (V in <V TH ), bóng bán dẫn điều khiển nằm trong vùng cắt và không dẫn bất kỳ dòng điện nào. Vì vậy, điện áp rơi trên điện trở tải là KHÔNG và điện áp đầu ra bằng V DD . Bây giờ, khi điện áp đầu vào tăng hơn nữa, bóng bán dẫn điều khiển sẽ bắt đầu dẫn dòng khác 0 và nMOS đi trong vùng bão hòa.

Về mặt toán học,

$$ I_ {D} = \ frac {K_ {n}} {2} \ left [V_ {GS} -V_ {TO} \ right] ^ {2} $$

Tăng điện áp đầu vào hơn nữa, bóng bán dẫn trình điều khiển sẽ đi vào vùng tuyến tính và đầu ra của bóng bán dẫn điều khiển giảm.

$$ I_ {D} = \ frac {K_ {n}} {2} 2 \ left [V_ {GS} -V_ {TO} \ right] V_ {DS} -V_ {DS} ^ {2} $$

VTC của biến tần tải điện trở, được hiển thị bên dưới, cho biết chế độ hoạt động của bóng bán dẫn trình điều khiển và các điểm điện áp.

Biến tần với tải MOSFET loại N

Ưu điểm chính của việc sử dụng MOSFET làm thiết bị tải là diện tích silicon chiếm bởi bóng bán dẫn nhỏ hơn diện tích chiếm bởi tải điện trở. Ở đây, MOSFET là tải hoạt động và biến tần có tải hoạt động cho hiệu suất tốt hơn biến tần có tải điện trở.

Tải nâng cao NMOS

Hai biến tần với thiết bị tải kiểu nâng cao được thể hiện trong hình. Transistor tải có thể được vận hành, trong vùng bão hòa hoặc trong vùng tuyến tính, tùy thuộc vào điện áp phân cực được áp dụng cho cực cổng của nó. Biến tần tải tăng cường bão hòa được hiển thị trong hình. (a). Nó đòi hỏi một nguồn cung cấp điện áp đơn và quá trình chế tạo đơn giản và do đó V OH được giới hạn ở những V DD - V T .

Biến tần tải tăng cường tuyến tính được hiển thị trong hình. (b). Nó luôn hoạt động trong vùng tuyến tính; nên V OH bằng V DD .

Biến tần tải tuyến tính có biên độ nhiễu cao hơn so với biến tần tăng cường bão hòa. Nhưng nhược điểm của biến tần tăng cường tuyến tính là nó yêu cầu hai nguồn điện riêng biệt và cả hai mạch đều bị tiêu tán công suất cao. Do đó, biến tần tăng cường không được sử dụng trong bất kỳ ứng dụng kỹ thuật số quy mô lớn nào.

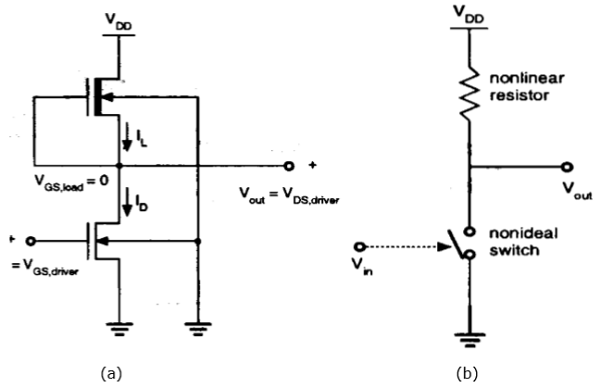

Tải cạn kiệt NMOS

Hạn chế của bộ biến tần phụ tải nâng cao có thể được khắc phục bằng cách sử dụng bộ biến tần tải suy giảm. So với biến tần tải nâng cao, biến tần tải suy giảm yêu cầu thêm một số bước chế tạo để cấy kênh để điều chỉnh điện áp ngưỡng của tải.

Ưu điểm của biến tần tải suy giảm là - chuyển tiếp VTC sắc nét, biên độ nhiễu tốt hơn, cấp nguồn đơn và diện tích bố trí tổng thể nhỏ hơn.

Như trong hình, cổng và đầu cuối nguồn của tải được kết nối; Vì vậy, V GS = 0. Như vậy, điện áp ngưỡng của tải là âm. Vì thế,

$$ V_ {GS, load}> V_ {T, load} $$ hài lòng

Do đó, thiết bị tải luôn có kênh dẫn không phụ thuộc vào mức điện áp đầu vào và đầu ra.

Khi bóng bán dẫn tải ở trong vùng bão hòa, dòng tải được cho bởi

$$ I_ {D, load} = \ frac {K_ {n, load}} {2} \ left [-V_ {T, load} \ left (V_ {out} \ right) \ right] ^ {2} $ $

Khi bóng bán dẫn tải ở vùng tuyến tính, dòng tải được cho bởi

$$ I_ {D, load} = \ frac {K_ {n, load}} {2} \ left [2 \ left | V_ {T, load} \ left (V_ {out} \ right) \ right |. \ Left (V_ {DD} -V_ {out} \ right) - \ left (V_ {DD} -V_ {out} \ right ) ^ {2} \ right] $$

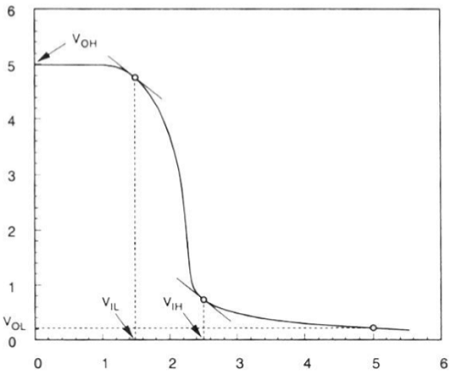

Đặc tính truyền điện áp của biến tần tải suy giảm được thể hiện trong hình bên dưới:

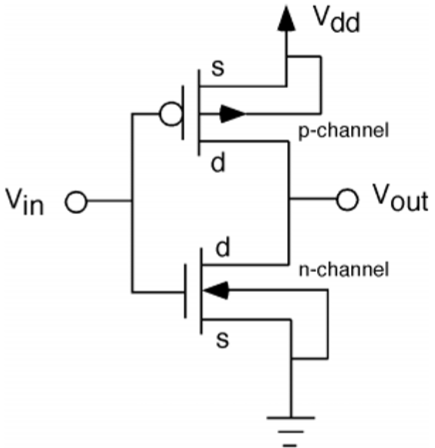

Biến tần CMOS - Mạch, Hoạt động và Mô tả

Mạch biến tần CMOS được hiển thị trong hình. Ở đây, bóng bán dẫn nMOS và pMOS hoạt động như bóng bán dẫn trình điều khiển; khi một bóng bán dẫn BẬT, bóng bán dẫn khác TẮT.

Cấu hình này được gọi là complementary MOS (CMOS). Đầu vào được kết nối với cực cổng của cả hai bóng bán dẫn sao cho cả hai đều có thể được điều khiển trực tiếp với điện áp đầu vào. Chất nền của nMOS được kết nối với mặt đất và chất nền của pMOS được kết nối với nguồn điện, V DD .

Vì vậy, V SB = 0 cho cả hai bóng bán dẫn.

$$ V_ {GS, n} = V_ {in} $$

$$ V_ {DS, n} = V_ {out} $$

Và,

$$ V_ {GS, p} = V_ {in} -V_ {DD} $$

$$ V_ {DS, p} = V_ {out} -V_ {DD} $$

Khi đầu vào của nMOS nhỏ hơn điện áp ngưỡng (V in <V TO, n ), nMOS bị ngắt và pMOS ở trong vùng tuyến tính. Vì vậy, dòng tiêu của cả hai bóng bán dẫn bằng không.

$$ I_ {D, n} = I_ {D, p} = 0 $$

Do đó, điện áp đầu ra V OH bằng điện áp cung cấp.

$$ V_ {out} = V_ {OH} = V_ {DD} $$

Khi điện áp đầu vào lớn hơn V DD + V TO, p , bóng bán dẫn pMOS nằm trong vùng cắt và nMOS ở vùng tuyến tính, do đó dòng tiêu của cả hai bóng bán dẫn bằng không.

$$ I_ {D, n} = I_ {D, p} = 0 $$

Do đó, điện áp đầu ra V OL bằng không.

$$ V_ {out} = V_ {OL} = 0 $$

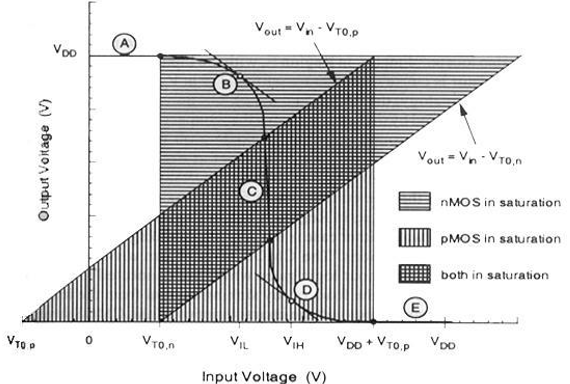

NMOS hoạt động trong vùng bão hòa nếu V in > V TO và nếu các điều kiện sau được thỏa mãn.

$$ V_ {DS, n} \ geq V_ {GS, n} -V_ {TO, n} $$

$$ V_ {out} \ geq V_ {in} -V_ {TO, n} $$

PMOS hoạt động trong vùng bão hòa nếu V trong <V DD + V TO, p và nếu các điều kiện sau được thỏa mãn.

$$ V_ {DS, p} \ leq V_ {GS, p} -V_ {TO, p} $$

$$ V_ {out} \ leq V_ {in} -V_ {TO, p} $$

Đối với các giá trị khác nhau của điện áp đầu vào, các vùng hoạt động được liệt kê bên dưới cho cả hai bóng bán dẫn.

| Khu vực | V trong | V ra | nMOS | pMOS |

|---|---|---|---|---|

| A | <V TO, n | V OH | Cắt | Tuyến tính |

| B | V IL | ≈ V OH cao | Bão hòa | Tuyến tính |

| C | V th | V th | Bão hòa | Bão hòa |

| D | V IH | V OL thấp | Tuyến tính | Bão hòa |

| E | > (V DD + V TO, p ) | V CV | Tuyến tính | Cắt |

VTC của CMOS được thể hiện trong hình dưới đây -