Thiết kế VLSI - Transistor MOS

Công nghệ MOSFET bổ sung (CMOS) được sử dụng rộng rãi ngày nay để tạo thành mạch trong nhiều ứng dụng khác nhau. Máy tính, CPU và điện thoại di động ngày nay sử dụng CMOS do một số ưu điểm chính. CMOS cung cấp khả năng tiêu tán điện năng thấp, tốc độ tương đối cao, biên độ nhiễu cao ở cả hai trạng thái và sẽ hoạt động trên nhiều loại điện áp nguồn và điện áp đầu vào (miễn là điện áp nguồn là cố định)

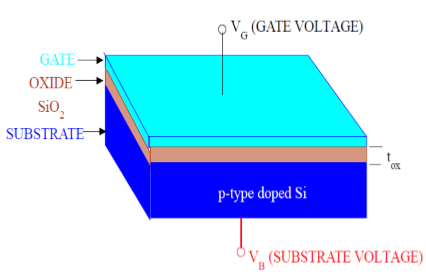

Đối với các quá trình chúng ta sẽ thảo luận, loại bóng bán dẫn có sẵn là Bóng bán dẫn hiệu ứng trường kim loại-oxit-bán dẫn (MOSFET). Các bóng bán dẫn này được hình thànhas a ‘sandwich’bao gồm một lớp bán dẫn, thường là một lát, hoặc tấm mỏng, từ một tinh thể silicon; một lớp silicon dioxide (oxit) và một lớp kim loại.

Cấu trúc của MOSFET

Như thể hiện trong hình, cấu trúc MOS chứa ba lớp:

The Metal Gate Electrode

The Insulating Oxide Layer (SiO2)

P – type Semiconductor (Substrate)

Cấu trúc MOS tạo thành một tụ điện, với cổng và chất nền là hai tấm và lớp oxit làm vật liệu điện môi. Độ dày của vật liệu điện môi (SiO 2 ) thường từ 10 nm đến 50 nm. Nồng độ và sự phân bố sóng mang bên trong chất nền có thể được điều khiển bởi điện áp bên ngoài đặt vào cổng và thiết bị đầu cuối chất nền. Bây giờ, để hiểu cấu trúc của MOS, trước tiên hãy xem xét các đặc tính điện cơ bản của chất nền bán dẫn loại P.

Nồng độ hạt tải điện trong vật liệu bán dẫn luôn tuân theo Mass Action Law. Luật Hành động Quần chúng được đưa ra bởi -

$$ np = n_ {i} ^ {2} $$

Ở đâu,

n là nồng độ hạt tải điện của các electron

p là nồng độ hạt tải điện của các lỗ

ni là nồng độ chất mang nội tại của Silicon

Bây giờ giả sử chất nền được bình đẳng với pha tạp chất nhận (Boron) Nồng độ N Một . Vì vậy, nồng độ điện tử và lỗ trống trong chất nền loại p là

$$ n_ {po} = \ frac {n_ {i} ^ {2}} {N_ {A}} $$

$$ p_ {po} = N_ {A} $$

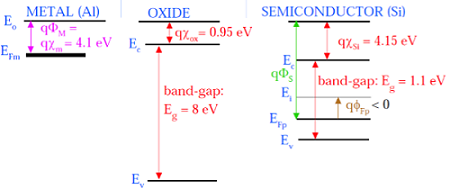

Đây, nồng độ doping NAlớn hơn (10 15 đến 10 16 cm −3 ) so với nồng độ nội tại ni. Bây giờ, để hiểu cấu trúc MOS, hãy xem xét biểu đồ mức năng lượng của chất nền silicon loại p.

Như trong hình, độ rộng vùng cấm giữa vùng dẫn và vùng hóa trị là 1,1eV. Ở đây, tiềm năng Fermi Φ F là hiệu số giữa mức Fermi nội tại (E i ) và mức Fermi (E FP ).

Trong đó Fermi cấp E F phụ thuộc vào nồng độ pha tạp. Điện thế Fermi Φ F là hiệu số giữa mức Fermi nội tại (E i ) và mức Fermi (E FP ).

Về mặt toán học,

$$ \ Phi_ {Fp} = \ frac {E_ {F} -E_ {i}} {q} $$

Hiệu điện thế giữa vùng dẫn và không gian tự do được gọi là ái lực điện tử và được ký hiệu là qx.

Vì vậy, năng lượng cần thiết để một electron di chuyển từ mức Fermi sang không gian tự do được gọi là hàm làm việc (qΦ S ) và nó được cho bởi

$$ q \ Phi _ {s} = (E_ {c} -E_ {F}) + qx $$

Hình dưới đây mô tả sơ đồ dải năng lượng của các thành phần tạo nên MOS.

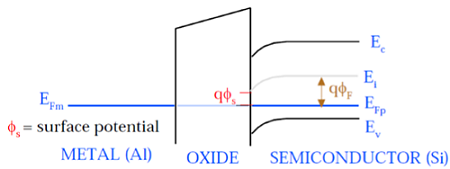

Như hình trên, lớp SiO 2 cách điện có vùng cấm năng lượng lớn 8eV và cơ năng làm việc là 0,95 eV. Cổng kim loại có chức năng làm việc 4,1eV. Ở đây, các chức năng làm việc khác nhau nên sẽ tạo ra sụt áp trên toàn hệ thống MOS. Hình dưới đây cho thấy biểu đồ dải năng lượng kết hợp của hệ thống MOS.

Như thể hiện trong hình này, mức điện thế fermi của cổng kim loại và chất bán dẫn (Si) có cùng tiềm năng. Điện thế Fermi tại bề mặt được gọi là điện thế bề mặt Φ S và nó nhỏ hơn điện thế Fermi Φ F về độ lớn.

Hoạt động của MOSFET

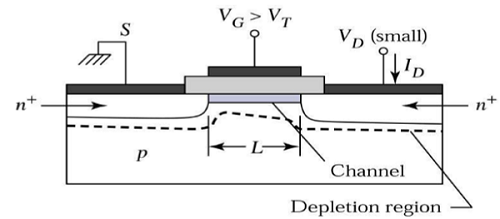

MOSFET bao gồm một tụ điện MOS với hai tiếp giáp pn được đặt đóng vào vùng kênh và vùng này được điều khiển bởi điện áp cổng. Để làm cho cả hai điểm tiếp giáp pn được phân cực ngược, điện thế cơ chất được giữ thấp hơn điện thế ba đầu cuối còn lại.

Nếu điện áp cổng được tăng lên vượt quá điện áp ngưỡng (V GS > V TO ), lớp đảo ngược sẽ được thiết lập trên bề mặt và kênh loại n sẽ được hình thành giữa nguồn và cống. Kênh loại n này sẽ mang dòng tiêu theo giá trị V DS .

Đối với các giá trị khác nhau của V DS , MOSFET có thể được vận hành ở các vùng khác nhau như được giải thích bên dưới.

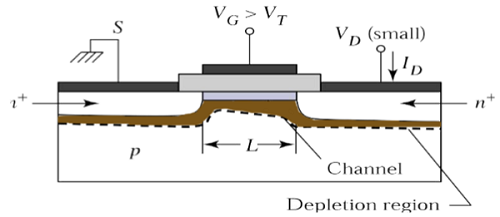

Vùng tuyến tính

Tại V DS = 0, cân bằng nhiệt tồn tại trong vùng kênh đảo ngược và dòng thoát I D = 0. Bây giờ nếu điện áp thoát nhỏ, V DS > 0 được áp dụng, một dòng thoát tỷ lệ với V DS sẽ bắt đầu chạy từ nguồn sang thoát nước qua kênh.

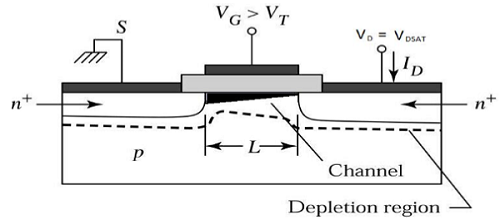

Kênh cung cấp một đường dẫn liên tục cho dòng điện từ nguồn đến cống. Phương thức hoạt động này được gọi làlinear region. Hình cắt ngang của MOSFET kênh n, hoạt động trong vùng tuyến tính, được thể hiện trong hình bên dưới.

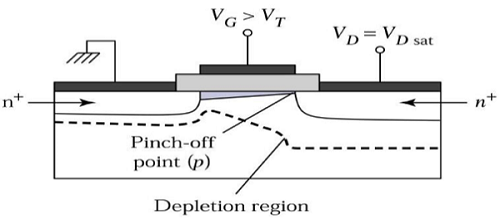

Ở rìa của vùng bão hòa

Bây giờ nếu V DS tăng lên, phí trong kênh và độ sâu kênh giảm ở cuối cống. Đối với V DS = V DSAT , phí trong kênh giảm xuống 0, được gọi làpinch – off point. Hình cắt ngang của MOSFET kênh n hoạt động ở rìa của vùng bão hòa được thể hiện trong hình bên dưới.

Vùng bão hòa

Đối với V DS > V DSAT , bề mặt cạn kiệt hình thành gần chỗ thoát nước, và bằng cách tăng điện áp thoát nước, vùng cạn kiệt này mở rộng đến nguồn.

Phương thức hoạt động này được gọi là Saturation region. Các điện tử đi từ nguồn đến đầu kênh, đi vào vùng cạn kiệt và được gia tốc về phía rãnh trong điện trường cao.

MOSFET Dòng điện - Đặc tính điện áp

Để hiểu đặc tính dòng điện - điện áp của MOSFET, thực hiện tính gần đúng cho kênh. Nếu không có sự gần đúng này, phân tích ba chiều của hệ thống MOS trở nên phức tạp. CácGradual Channel Approximation (GCA) đối với đặc tính dòng điện - điện áp sẽ làm giảm vấn đề phân tích.

Xấp xỉ kênh dần dần (GCA)

Xem xét hình cắt ngang của MOSFET kênh n hoạt động ở chế độ tuyến tính. Ở đây, nguồn và chất nền được kết nối với mặt đất. V S = V B = 0. Các cổng - để - nguồn (V GS ) và cống - để - Điện áp nguồn (V DS ) điện áp là các thông số bên ngoài điều khiển cống hiện tại tôi D .

Điện áp, V GS được đặt thành điện áp lớn hơn điện áp ngưỡng V TO , để tạo kênh giữa nguồn và cống. Như trong hình, hướng x vuông góc với bề mặt và hướng y song song với bề mặt.

Ở đây, y = 0 ở đầu nguồn như trong hình. Điện áp kênh, đối với nguồn, được biểu thị bằngVC(Y). Giả sử rằng điện áp ngưỡng VTO là không đổi dọc theo vùng kênh, trong khoảng từ y = 0 đến y = L. Điều kiện biên đối với điện áp kênh V C là:

$$ V_ {c} \ left (y = 0 \ right) = V_ {s} = 0 \ và \, V_ {c} \ left (y = L \ right) = V_ {DS} $$

Chúng ta cũng có thể cho rằng

$$ V_ {GS} \ geq V_ {TO} $$ và

$$ V_ {GD} = V_ {GS} -V_ {DS} \ geq V_ {TO} $$

Gọi Q1 (y) là tổng điện tích electron di động trong lớp nghịch đảo bề mặt. Điện tích electron này có thể được biểu thị bằng:

$$ Q1 (y) = - C_ {ox}. [V_ {GS} -V_ {C (Y)} - V_ {TO}] $$

Hình dưới đây cho thấy dạng hình học không gian của lớp đảo ngược bề mặt và cho biết kích thước của nó. Lớp đảo ngược giảm dần khi chúng ta di chuyển từ cống sang nguồn. Bây giờ, nếu chúng ta xem xét vùng dy nhỏ của chiều dài kênh L thì điện trở gia tăng dR do vùng này cung cấp có thể được biểu thị bằng:

$$ dR = - \ frac {dy} {w. \ mu _ {n} .Q1 (y)} $$

Ở đây, dấu trừ là do độ phân cực âm của điện tích lớp nghịch đảo Q1 và μ n là độ linh động bề mặt, không đổi. Bây giờ, thay giá trị của Q1 (y) vào phương trình dR -

$$ dR = - \ frac {dy} {w. \ mu _ {n}. \ left \ {-C_ {ox} \ left [V_ {GS} -V_ {C \ left (Y \ right)} \ right ] -V_ {TO} \ right \}} $$

$$ dR = \ frac {dy} {w. \ mu _ {n} .C_ {ox} \ left [V_ {GS} -V_ {C \ left (Y \ right)} \ right] -V_ {TO} } $$

Bây giờ điện áp giảm trong vùng dy nhỏ có thể được đưa ra bởi

$$ dV_ {c} = I_ {D} .dR $$

Đặt giá trị của dR vào phương trình trên

$$ dV_ {C} = I_ {D}. \ frac {dy} {w. \ mu_ {n} .C_ {ox} \ left [V_ {GS} -V_ {C (Y)} \ right] -V_ {TO}} $$

$$ w. \ mu _ {n} .C_ {ox} \ left [V_ {GS} -V_ {C (Y)} - V_ {TO} \ right] .dV_ {C} = I_ {D} .dy $$

Để có được ID dòng xả trên toàn bộ vùng kênh, phương trình trên có thể được tích hợp dọc theo kênh từ y = 0 đến y = L và điện áp V C (y) = 0 đến V C (y) = V DS ,

$$ C_ {ox} .w. \ Mu _ {n}. \ Int_ {V_ {c} = 0} ^ {V_ {DS}} \ left [V_ {GS} -V_ {C \ left (Y \ right )} - V_ {TO} \ right] .dV_ {C} = \ int_ {Y = 0} ^ {L} I_ {D} .dy $$

$$ \ frac {C_ {ox} .w. \ mu _ {n}} {2} \ left (2 \ left [V_ {GS} -V_ {TO} \ right] V_ {DS} -V_ {DS} ^ {2} \ right) = I_ {D} \ left [L-0 \ right] $$

$$ I_ {D} = \ frac {C_ {ox}. \ Mu _ {n}} {2}. \ Frac {w} {L} \ left (2 \ left [V_ {GS} -V_ {TO} \ right] V_ {DS} -V_ {DS} ^ {2} \ right) $$

Đối với vùng tuyến tính V DS <V GS - V TO . Đối với vùng bão hòa, giá trị của V DS lớn hơn (V GS - V TO ). Do đó, đối với vùng bão hòa V DS = (V GS - V TO ).

$$ I_ {D} = C_ {ox}. \ Mu _ {n}. \ Frac {w} {2} \ left (\ frac {\ left [2V_ {DS} \ right] V_ {DS} -V_ { DS} ^ {2}} {L} \ right) $$

$$ I_ {D} = C_ {ox}. \ Mu _ {n}. \ Frac {w} {2} \ left (\ frac {2V_ {DS} ^ {2} -V_ {DS} ^ {2} } {L} \ right) $$

$$ I_ {D} = C_ {ox}. \ Mu _ {n}. \ Frac {w} {2} \ left (\ frac {V_ {DS} ^ {2}} {L} \ right) $$

$$ I_ {D} = C_ {ox}. \ Mu _ {n}. \ Frac {w} {2} \ left (\ frac {\ left [V_ {GS} -V_ {TO} \ right] ^ { 2}} {L} \ right) $$