Thiết kế VLSI - Hướng dẫn nhanh

Tích hợp quy mô rất lớn (VLSI) là quá trình tạo ra một integrated circuit (IC) bằng cách kết hợp hàng nghìn transistorsthành một con chip duy nhất. VLSI bắt đầu vào những năm 1970 khi phức tạpsemiconductor và communicationcông nghệ đang được phát triển. Cácmicroprocessor là một thiết bị VLSI.

Trước khi công nghệ VLSI ra đời, hầu hết các vi mạch đều có một số chức năng hạn chế mà chúng có thể thực hiện. Anelectronic circuit có thể bao gồm một CPU, ROM, RAM và khác glue logic. VLSI cho phép các nhà thiết kế vi mạch thêm tất cả những thứ này vào một chip.

Ngành công nghiệp điện tử đã đạt được sự tăng trưởng phi thường trong vài thập kỷ qua, chủ yếu là do những tiến bộ nhanh chóng trong công nghệ tích hợp quy mô lớn và các ứng dụng thiết kế hệ thống. Với sự ra đời của các thiết kế tích hợp quy mô rất lớn (VLSI), số lượng các ứng dụng của mạch tích hợp (IC) trong tính toán hiệu năng cao, điều khiển, viễn thông, xử lý hình ảnh và video và điện tử tiêu dùng đã tăng lên với tốc độ rất nhanh.

Các công nghệ tiên tiến hiện nay như độ phân giải cao và video tốc độ bit thấp và truyền thông di động cung cấp cho người dùng cuối một lượng ứng dụng tuyệt vời, sức mạnh xử lý và tính di động. Xu hướng này dự kiến sẽ phát triển nhanh chóng, có ý nghĩa rất quan trọng đối với thiết kế VLSI và thiết kế hệ thống.

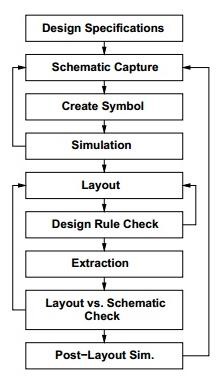

Luồng thiết kế VLSI

Luồng thiết kế vi mạch VLSI được thể hiện trong hình bên dưới. Các cấp độ thiết kế khác nhau được đánh số và các khối hiển thị các quy trình trong quy trình thiết kế.

Các thông số kỹ thuật có trước, chúng mô tả một cách trừu tượng, chức năng, giao diện và kiến trúc của mạch vi mạch kỹ thuật số sẽ được thiết kế.

Sau đó, mô tả hành vi được tạo ra để phân tích thiết kế về chức năng, hiệu suất, sự tuân thủ các tiêu chuẩn nhất định và các thông số kỹ thuật khác.

Mô tả RTL được thực hiện bằng HDLs. Mô tả RTL này được mô phỏng để kiểm tra chức năng. Từ đây trở đi chúng ta cần sự trợ giúp của các công cụ EDA.

Mô tả RTL sau đó được chuyển đổi thành danh sách mạng cấp cổng bằng các công cụ tổng hợp logic. Một netlist tập hợp là một mô tả về mạch theo các cổng và kết nối giữa chúng, được tạo ra theo cách mà chúng đáp ứng các thông số kỹ thuật về thời gian, công suất và diện tích.

Cuối cùng, một bố cục vật lý được thực hiện, sẽ được xác minh và sau đó được gửi đến chế tạo.

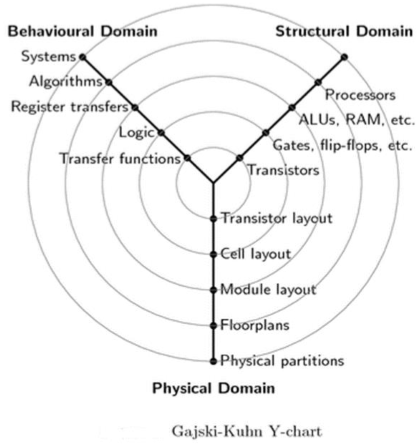

Biểu đồ Y

Biểu đồ Gajski-Kuhn Y là một mô hình ghi lại những cân nhắc khi thiết kế các thiết bị bán dẫn.

Ba miền của biểu đồ Gajski-Kuhn Y nằm trên các trục xuyên tâm. Mỗi lĩnh vực có thể được chia thành các cấp độ trừu tượng, sử dụng các vòng đồng tâm.

Ở cấp cao nhất (vòng ngoài), chúng tôi xem xét kiến trúc của chip; ở các cấp thấp hơn (vòng trong), chúng tôi liên tiếp tinh chỉnh thiết kế để triển khai chi tiết hơn -

Tạo mô tả cấu trúc từ một hành vi được thực hiện thông qua các quá trình tổng hợp cấp cao hoặc tổng hợp logic.

Tạo mô tả vật lý từ cấu trúc được thực hiện thông qua tổng hợp bố cục.

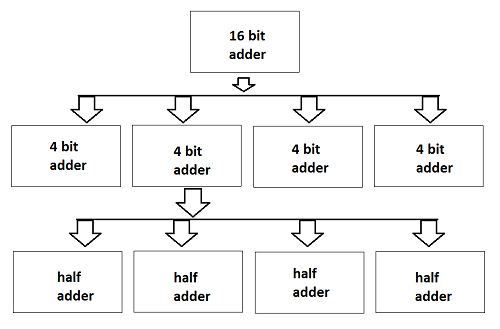

Cấu trúc phân cấp thiết kế

Hệ thống phân cấp thiết kế liên quan đến nguyên tắc "Chia rẽ và Chinh phục." Nó không là gì khác ngoài việc chia nhiệm vụ thành các nhiệm vụ nhỏ hơn cho đến khi nó đạt đến mức đơn giản nhất. Quy trình này là phù hợp nhất vì sự phát triển cuối cùng của thiết kế đã trở nên đơn giản đến mức việc sản xuất nó trở nên dễ dàng hơn.

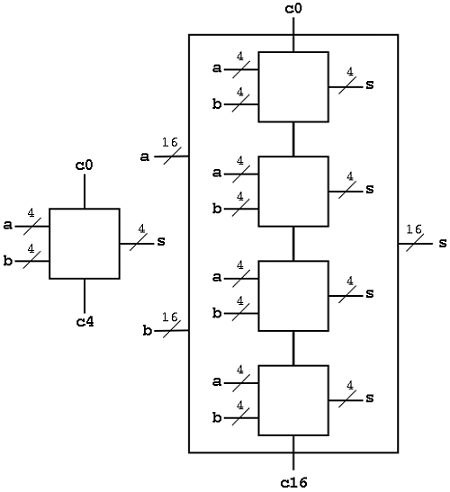

Chúng ta có thể thiết kế nhiệm vụ đã cho vào miền của quy trình thiết kế (Hành vi, Cấu trúc và Hình học). Để hiểu điều này, chúng ta hãy lấy một ví dụ về việc thiết kế một bộ cộng 16-bit, như thể hiện trong hình bên dưới.

Ở đây, toàn bộ chip của bộ cộng 16 bit được chia thành bốn mô-đun của bộ cộng 4 bit. Hơn nữa, chia bộ cộng 4 bit thành bộ cộng 1 bit hoặc bộ cộng nửa. Ngoài ra 1 bit là quá trình thiết kế đơn giản nhất và mạch bên trong của nó cũng dễ chế tạo trên chip. Bây giờ, kết nối tất cả bốn bộ cộng cuối cùng, chúng ta có thể thiết kế bộ cộng 4 bit và tiếp tục, chúng ta có thể thiết kế bộ cộng 16 bit.

FPGA - Giới thiệu

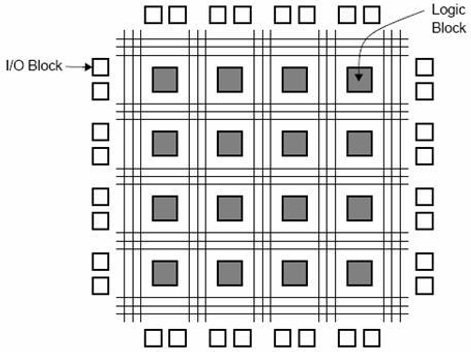

Hình thức đầy đủ của FPGA Là "Field Programmable Gate Array”. Nó chứa mười nghìn đến hơn một triệu cổng logic với kết nối liên thông có thể lập trình được. Các kết nối có thể lập trình có sẵn cho người dùng hoặc nhà thiết kế để thực hiện các chức năng đã cho một cách dễ dàng. Một mẫu chip FPGA điển hình được thể hiện trong hình bên. Có các khối I / O, được thiết kế và đánh số theo chức năng. Đối với mỗi mô-đun của thành phần mức logic, cóCLB’s (Configurable Logic Blocks).

CLB thực hiện hoạt động logic được cung cấp cho mô-đun. Kết nối giữa các khối CLB và I / O được thực hiện với sự trợ giúp của các kênh định tuyến ngang, kênh định tuyến dọc và PSM (Bộ ghép kênh có thể lập trình).

Số lượng CLB mà nó chứa chỉ quyết định độ phức tạp của FPGA. Chức năng của CLB và PSM được thiết kế bởi VHDL hoặc bất kỳ ngôn ngữ mô tả phần cứng nào khác. Sau khi lập trình, CLB và PSM được đặt trên chip và kết nối với nhau bằng các kênh định tuyến.

Ưu điểm

- Nó đòi hỏi thời gian rất nhỏ; bắt đầu từ quy trình thiết kế đến chip chức năng.

- Không có bước sản xuất vật lý nào liên quan đến nó.

- Bất lợi duy nhất là, nó là tốn kém hơn so với các phong cách khác.

Thiết kế mảng cổng

Các gate array (GA)đứng thứ hai sau FPGA, về khả năng tạo mẫu nhanh. Trong khi lập trình của người dùng là quan trọng đối với việc triển khai thiết kế của chip FPGA, thiết kế và xử lý mặt nạ kim loại được sử dụng cho GA. Việc triển khai mảng cổng yêu cầu quy trình sản xuất gồm hai bước.

Giai đoạn đầu tiên dẫn đến một loạt các bóng bán dẫn không được cam kết trên mỗi chip GA. Các chip chưa được cam kết này có thể được lưu trữ để tùy chỉnh sau này, quá trình này được hoàn thành bằng cách xác định các kết nối kim loại giữa các bóng bán dẫn của mảng. Việc tạo mẫu các mối liên kết kim loại được thực hiện ở giai đoạn cuối của quá trình chế tạo chip, do đó thời gian quay vòng vẫn có thể ngắn, vài ngày đến vài tuần. Hình dưới đây cho thấy các bước xử lý cơ bản để thực hiện mảng cổng.

Nền tảng mảng cổng điển hình sử dụng các khu vực dành riêng được gọi là kênh, để định tuyến giữa các ô giữa các hàng hoặc cột của bóng bán dẫn MOS. Chúng đơn giản hóa các kết nối. Các mẫu kết nối thực hiện các cổng logic cơ bản được lưu trữ trong thư viện, thư viện này sau đó có thể được sử dụng để tùy chỉnh các hàng bóng bán dẫn không được chuyển theo danh sách mạng.

Trong hầu hết các GA hiện đại, nhiều lớp kim loại được sử dụng để định tuyến kênh. Với việc sử dụng nhiều lớp được kết nối với nhau, việc định tuyến có thể đạt được trên các vùng ô hoạt động; để có thể loại bỏ các kênh định tuyến như trong chip Sea-of-Gates (SOG). Ở đây, toàn bộ bề mặt chip được bao phủ bởi các bóng bán dẫn nMOS và pMOS không cam kết. Các bóng bán dẫn lân cận có thể được tùy chỉnh bằng cách sử dụng mặt nạ kim loại để tạo thành các cổng logic cơ bản.

Đối với định tuyến giữa các ô, một số bóng bán dẫn không được cam kết phải được hy sinh. Phong cách thiết kế này mang lại sự linh hoạt hơn cho các kết nối và thường ở mật độ cao hơn. Hệ số sử dụng chip GA được đo bằng diện tích chip đã sử dụng chia cho tổng diện tích chip. Nó cao hơn FPGA và tốc độ chip cũng vậy.

Thiết kế dựa trên ô tiêu chuẩn

Một thiết kế dựa trên ô tiêu chuẩn yêu cầu phát triển một bộ mặt nạ tùy chỉnh đầy đủ. Tế bào tiêu chuẩn còn được gọi là polycell. Theo cách tiếp cận này, tất cả các ô logic thường được sử dụng đều được phát triển, đặc trưng và lưu trữ trong một thư viện ô chuẩn.

Một thư viện có thể chứa vài trăm ô bao gồm bộ nghịch lưu, cổng NAND, cổng NOR, AOI phức tạp, cổng OAI, chốt D và Flip-flops. Mỗi loại cổng có thể được thực hiện trong một số phiên bản để cung cấp khả năng dẫn động thích hợp cho các đầu ra quạt khác nhau. Cổng biến tần có thể có kích thước tiêu chuẩn, kích thước gấp đôi và kích thước gấp bốn lần để nhà thiết kế chip có thể chọn kích thước phù hợp để có được tốc độ mạch cao và mật độ bố trí.

Mỗi ô được đặc trưng theo một số loại đặc điểm khác nhau, chẳng hạn như,

- Thời gian trễ so với điện dung tải

- Mô hình mô phỏng mạch

- Mô hình mô phỏng thời gian

- Mô hình mô phỏng lỗi

- Dữ liệu di động cho địa điểm và tuyến đường

- Dữ liệu mặt nạ

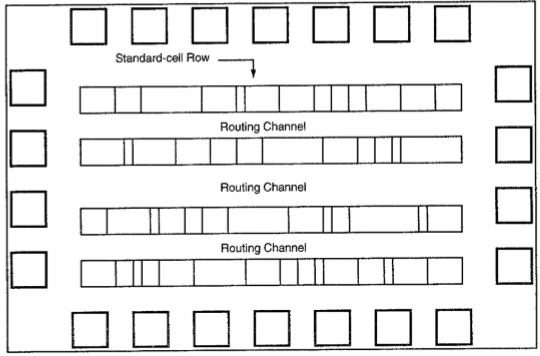

Để tự động sắp xếp các ô và định tuyến, mỗi bố cục ô được thiết kế với chiều cao cố định, để một số ô có thể được giới hạn cạnh nhau để tạo thành các hàng. Nguồn điện và đường ray nối đất chạy song song với ranh giới trên và dưới của ô. Vì vậy, các ô lân cận chia sẻ một bus nguồn chung và một bus mặt đất chung. Hình dưới đây là sơ đồ mặt bằng cho thiết kế dựa trên ô tiêu chuẩn.

Thiết kế tùy chỉnh đầy đủ

Trong một thiết kế hoàn toàn tùy chỉnh, toàn bộ thiết kế mặt nạ được tạo mới mà không cần sử dụng bất kỳ thư viện nào. Chi phí phát triển của phong cách thiết kế này đang tăng cao. Do đó, khái niệm tái sử dụng thiết kế đang trở nên nổi tiếng để giảm thời gian chu kỳ thiết kế và chi phí phát triển.

Thiết kế tùy chỉnh đầy đủ khó nhất có thể là thiết kế của một ô nhớ, có thể là tĩnh hoặc động. Đối với thiết kế chip logic, có thể đạt được một thương lượng tốt khi sử dụng kết hợp các kiểu thiết kế khác nhau trên cùng một chip, tức là các ô tiêu chuẩn, ô đường dẫn dữ liệu vàprogrammable logic arrays (PLAs).

Thực tế, nhà thiết kế thực hiện bố cục tùy chỉnh đầy đủ, tức là hình dạng, hướng và vị trí của mọi bóng bán dẫn. Năng suất thiết kế thường rất thấp; thường là vài chục bóng bán dẫn mỗi ngày, mỗi nhà thiết kế. Trong CMOS VLSI kỹ thuật số, thiết kế tùy chỉnh hoàn toàn hầu như không được sử dụng do chi phí nhân công cao. Những phong cách thiết kế này bao gồm việc thiết kế các sản phẩm có dung lượng lớn như chip nhớ, bộ vi xử lý hiệu suất cao và FPGA.

Công nghệ MOSFET bổ sung (CMOS) được sử dụng rộng rãi ngày nay để tạo thành mạch trong nhiều ứng dụng khác nhau. Máy tính, CPU và điện thoại di động ngày nay sử dụng CMOS do một số ưu điểm chính. CMOS cung cấp khả năng tiêu tán điện năng thấp, tốc độ tương đối cao, biên độ nhiễu cao ở cả hai trạng thái và sẽ hoạt động trên nhiều loại điện áp nguồn và điện áp đầu vào (miễn là điện áp nguồn là cố định)

Đối với các quá trình chúng ta sẽ thảo luận, loại bóng bán dẫn có sẵn là Bóng bán dẫn hiệu ứng trường kim loại-oxit-bán dẫn (MOSFET). Các bóng bán dẫn này được hình thànhas a ‘sandwich’bao gồm một lớp bán dẫn, thường là một lát, hoặc tấm mỏng, từ một tinh thể silicon; một lớp silicon dioxide (oxit) và một lớp kim loại.

Cấu trúc của MOSFET

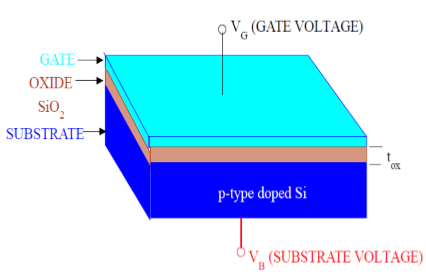

Như thể hiện trong hình, cấu trúc MOS chứa ba lớp:

The Metal Gate Electrode

The Insulating Oxide Layer (SiO2)

P – type Semiconductor (Substrate)

Cấu trúc MOS tạo thành một tụ điện, với cổng và chất nền là hai tấm và lớp oxit như vật liệu điện môi. Độ dày của vật liệu điện môi (SiO 2 ) thường từ 10 nm đến 50 nm. Nồng độ và sự phân bố sóng mang trong chất nền có thể được điều khiển bởi điện áp bên ngoài đặt vào cổng và thiết bị đầu cuối chất nền. Bây giờ, để hiểu cấu trúc của MOS, trước tiên hãy xem xét các đặc tính điện cơ bản của chất nền bán dẫn loại P.

Nồng độ hạt tải điện trong vật liệu bán dẫn luôn tuân theo Mass Action Law. Luật Hành động Quần chúng được đưa ra bởi -

$$n.p=n_{i}^{2}$$

Ở đâu,

n là nồng độ hạt tải điện của các electron

p là nồng độ hạt tải điện của các lỗ

ni là nồng độ chất mang nội tại của Silicon

Bây giờ giả sử chất nền được bình đẳng với pha tạp chất nhận (Boron) Nồng độ N Một . Vì vậy, nồng độ điện tử và lỗ trống trong chất nền loại p là

$$n_{po}=\frac{n_{i}^{2}}{N_{A}}$$

$$p_{po}=N_{A}$$

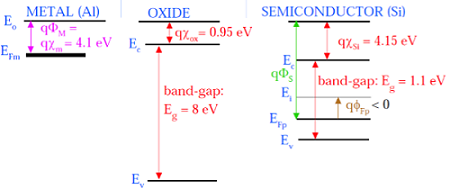

Đây, nồng độ doping NAlớn hơn (10 15 đến 10 16 cm −3 ) so với nồng độ nội tại ni. Bây giờ, để hiểu cấu trúc MOS, hãy xem xét biểu đồ mức năng lượng của chất nền silicon loại p.

Như trong hình, độ rộng vùng cấm giữa vùng dẫn và vùng hóa trị là 1,1eV. Ở đây, tiềm năng Fermi Φ F là hiệu số giữa mức Fermi nội tại (E i ) và mức Fermi (E FP ).

Trong đó mức Fermi E F phụ thuộc vào nồng độ pha tạp. Điện thế Fermi Φ F là hiệu số giữa mức Fermi nội tại (E i ) và mức Fermi (E FP ).

Về mặt toán học,

$$\Phi_{Fp}=\frac{E_{F}-E_{i}}{q}$$

Hiệu điện thế giữa vùng dẫn và vùng không gian tự do được gọi là ái lực điện tử và được ký hiệu là qx.

Vì vậy, năng lượng cần thiết để một electron di chuyển từ mức Fermi sang không gian tự do được gọi là hàm công việc (qΦ S ) và nó được cho bởi

$$q\Phi _{s}=(E_{c}-E_{F})+qx$$

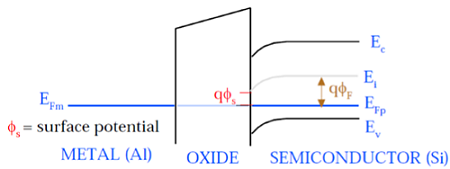

Hình sau đây cho thấy biểu đồ dải năng lượng của các thành phần tạo nên MOS.

Như hình trên, lớp SiO 2 cách điện có vùng cấm năng lượng lớn 8eV và cơ năng làm việc là 0,95 eV. Cổng kim loại có chức năng làm việc 4,1eV. Ở đây, các chức năng làm việc khác nhau nên sẽ tạo ra sụt áp trên toàn hệ thống MOS. Hình dưới đây cho thấy biểu đồ dải năng lượng kết hợp của hệ thống MOS.

Như thể hiện trong hình này, mức điện thế fermi của cổng kim loại và chất bán dẫn (Si) có cùng tiềm năng. Điện thế Fermi tại bề mặt được gọi là điện thế bề mặt Φ S và nó nhỏ hơn điện thế Fermi Φ F về độ lớn.

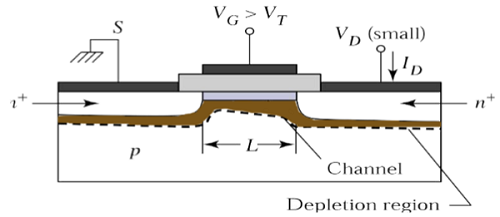

Hoạt động của MOSFET

MOSFET bao gồm một tụ điện MOS với hai tiếp giáp pn được đặt đóng vào vùng kênh và vùng này được điều khiển bởi điện áp cổng. Để làm cho cả hai điểm tiếp giáp pn được phân cực ngược, điện thế cơ chất được giữ thấp hơn điện thế ba đầu cuối còn lại.

Nếu điện áp cổng tăng lên vượt quá điện áp ngưỡng (V GS > V TO ), lớp đảo ngược sẽ được thiết lập trên bề mặt và kênh loại n sẽ được hình thành giữa nguồn và cống. Kênh loại n này sẽ mang dòng tiêu theo giá trị V DS .

Đối với các giá trị khác nhau của V DS , MOSFET có thể được vận hành ở các vùng khác nhau như được giải thích bên dưới.

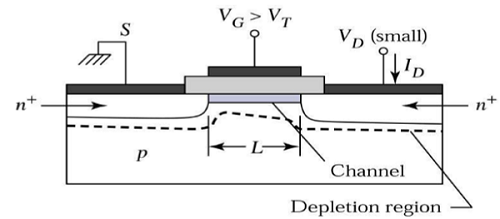

Vùng tuyến tính

Tại V DS = 0, cân bằng nhiệt tồn tại trong vùng kênh đảo ngược và dòng thoát I D = 0. Bây giờ nếu điện áp thoát nhỏ, V DS > 0 được áp dụng, một dòng thoát tỷ lệ với V DS sẽ bắt đầu chạy từ nguồn sang thoát nước qua kênh.

Kênh cung cấp một đường dẫn liên tục cho dòng điện từ nguồn đến cống. Phương thức hoạt động này được gọi làlinear region. Hình chiếu cắt ngang của MOSFET kênh n, hoạt động trong vùng tuyến tính, được thể hiện trong hình bên dưới.

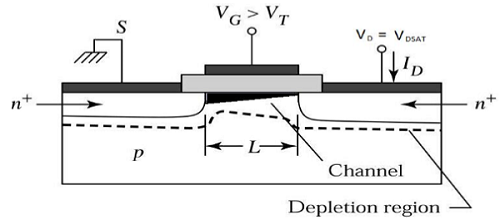

Ở rìa của vùng bão hòa

Bây giờ nếu V DS được tăng lên, phí trong kênh và độ sâu của kênh giảm ở cuối cống. Đối với V DS = V DSAT , phí trong kênh giảm xuống 0, được gọi làpinch – off point. Hình cắt ngang của MOSFET kênh n hoạt động ở rìa của vùng bão hòa được thể hiện trong hình bên dưới.

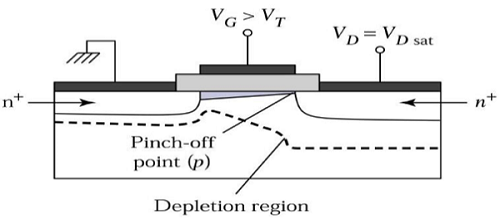

Vùng bão hòa

Đối với V DS > V DSAT , bề mặt cạn kiệt hình thành gần chỗ thoát nước, và bằng cách tăng điện áp thoát nước, vùng cạn kiệt này mở rộng đến nguồn.

Phương thức hoạt động này được gọi là Saturation region. Các điện tử đi từ nguồn đến đầu kênh, đi vào vùng cạn kiệt và được gia tốc về phía rãnh trong điện trường cao.

MOSFET Dòng điện - Đặc tính điện áp

Để hiểu đặc tính dòng điện - điện áp của MOSFET, thực hiện tính gần đúng cho kênh. Nếu không có sự gần đúng này, việc phân tích ba chiều của hệ thống MOS trở nên phức tạp. CácGradual Channel Approximation (GCA) đối với đặc tính dòng điện - điện áp sẽ làm giảm vấn đề phân tích.

Xấp xỉ kênh dần dần (GCA)

Xem xét hình cắt ngang của MOSFET kênh n hoạt động ở chế độ tuyến tính. Ở đây, nguồn và chất nền được kết nối với mặt đất. V S = V B = 0. Các cổng - để - nguồn (V GS ) và cống - để - Điện áp nguồn (V DS ) điện áp là các thông số bên ngoài điều khiển cống hiện tại tôi D .

Điện áp, V GS được đặt thành điện áp lớn hơn điện áp ngưỡng V TO , để tạo kênh giữa nguồn và cống. Như trong hình, phương x vuông góc với bề mặt và phương y song song với bề mặt.

Ở đây, y = 0 ở đầu nguồn như trong hình. Điện áp kênh, đối với nguồn, được biểu thị bằngVC(Y). Giả sử rằng điện áp ngưỡng VTO là không đổi dọc theo vùng kênh, trong khoảng từ y = 0 đến y = L. Điều kiện biên đối với điện áp kênh V C là:

$$V_{c}\left ( y = 0 \right ) = V_{s} = 0 \,and\,V_{c}\left ( y = L \right ) = V_{DS}$$

Chúng ta cũng có thể cho rằng

$$V_{GS}\geq V_{TO}$$ và

$$V_{GD} = V_{GS}-V_{DS}\geq V_{TO}$$

Gọi Q1 (y) là tổng điện tích electron di động trong lớp nghịch đảo bề mặt. Điện tích electron này có thể được biểu thị bằng:

$$Q1(y)=-C_{ox}.[V_{GS}-V_{C(Y)}-V_{TO}]$$

Hình dưới đây cho thấy dạng hình học không gian của lớp đảo ngược bề mặt và cho biết kích thước của nó. Lớp đảo ngược giảm dần khi chúng ta di chuyển từ cống sang nguồn. Bây giờ, nếu chúng ta xem xét vùng dy nhỏ của chiều dài kênh L thì điện trở gia tăng dR do vùng này cung cấp có thể được biểu thị bằng:

$$dR=-\frac{dy}{w.\mu _{n}.Q1(y)}$$

Ở đây, dấu trừ là do độ phân cực âm của điện tích lớp nghịch đảo Q1 và μ n là độ linh động bề mặt, không đổi. Bây giờ, hãy thay giá trị của Q1 (y) vào phương trình dR -

$$dR=-\frac{dy}{w.\mu _{n}.\left \{ -C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO} \right \}}$$

$$dR=\frac{dy}{w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C\left ( Y \right )} \right ]-V_{TO}}$$

Bây giờ điện áp giảm trong vùng dy nhỏ có thể được đưa ra bởi

$$dV_{c}=I_{D}.dR$$

Đặt giá trị của dR vào phương trình trên

$$dV_{C}=I_{D}.\frac{dy}{w.\mu_{n}.C_{ox}\left [ V_{GS}-V_{C(Y)} \right ]-V_{TO}}$$

$$w.\mu _{n}.C_{ox}\left [ V_{GS}-V_{C(Y)}-V_{TO} \right ].dV_{C}=I_{D}.dy$$

Để có được ID dòng xả trên toàn bộ vùng kênh, phương trình trên có thể được tích hợp dọc theo kênh từ y = 0 đến y = L và điện áp V C (y) = 0 đến V C (y) = V DS ,

$$C_{ox}.w.\mu _{n}.\int_{V_{c}=0}^{V_{DS}} \left [ V_{GS}-V_{C\left ( Y \right )}-V_{TO} \right ].dV_{C} = \int_{Y=0}^{L}I_{D}.dy$$

$$\frac{C_{ox}.w.\mu _{n}}{2}\left ( 2\left [ V_{GS}-V_{TO} \right ] V_{DS}-V_{DS}^{2}\right ) = I_{D}\left [ L-0 \right ]$$

$$I_{D} = \frac{C_{ox}.\mu _{n}}{2}.\frac{w}{L}\left ( 2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2} \right )$$

Đối với vùng tuyến tính V DS <V GS - V TO . Đối với vùng bão hòa, giá trị của V DS lớn hơn (V GS - V TO ). Do đó, đối với vùng bão hòa V DS = (V GS - V TO ).

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ 2V_{DS} \right ]V_{DS}-V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{2V_{DS}^{2}-V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{V_{DS}^{2}}{L} \right )$$

$$I_{D} = C_{ox}.\mu _{n}.\frac{w}{2}\left ( \frac{\left [ V_{GS}-V_{TO} \right ]^{2}}{L} \right )$$

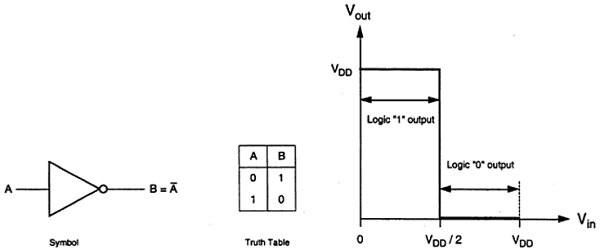

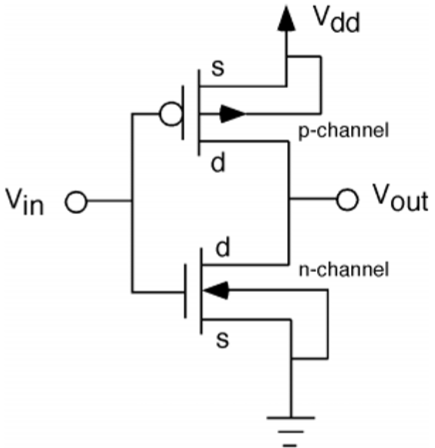

Biến tần thực sự là hạt nhân của tất cả các thiết kế kỹ thuật số. Khi đã hiểu rõ hoạt động và các đặc tính của nó, việc thiết kế các cấu trúc phức tạp hơn như cổng NAND, bộ cộng, bộ nhân và bộ vi xử lý được đơn giản hóa rất nhiều. Hoạt động điện của các mạch phức tạp này có thể được suy ra gần như hoàn toàn bằng cách ngoại suy các kết quả thu được đối với biến tần.

Việc phân tích các bộ biến tần có thể được mở rộng để giải thích hoạt động của các cổng phức tạp hơn như NAND, NOR hoặc XOR, từ đó tạo thành các khối xây dựng cho các mô-đun như bộ nhân và bộ xử lý. Trong chương này, chúng tôi tập trung vào một hiện thân duy nhất của cổng biến tần, là biến tần CMOS tĩnh - hay ngắn gọn là biến tần CMOS. Đây chắc chắn là phổ biến nhất hiện nay và do đó đáng được chúng tôi đặc biệt quan tâm.

Nguyên lý hoạt động

Biểu tượng logic và bảng sự thật của biến tần lý tưởng được thể hiện trong hình dưới đây. Ở đây A là đầu vào và B là đầu ra đảo ngược được biểu thị bằng điện áp nút của chúng. Sử dụng logic dương, giá trị Boolean của logic 1 được biểu thị bằng V dd và logic 0 được biểu thị bằng 0. V th là điện áp ngưỡng của bộ nghịch lưu, là V dd / 2, trong đó V dd là điện áp đầu ra.

Đầu ra được chuyển từ 0 sang V dd khi đầu vào nhỏ hơn V th . Vì vậy, đối với 0 <V trong <V thứ đầu ra bằng logic 0 đầu vào và V thứ <V trong <V dd bằng logic 1 đầu vào cho biến tần.

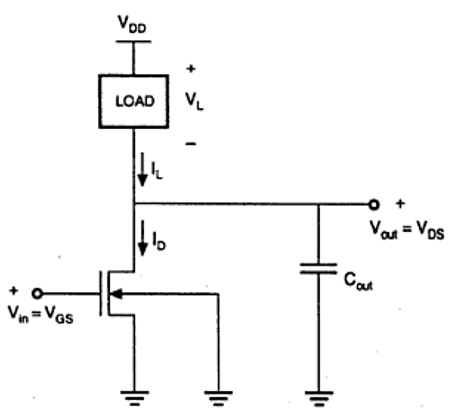

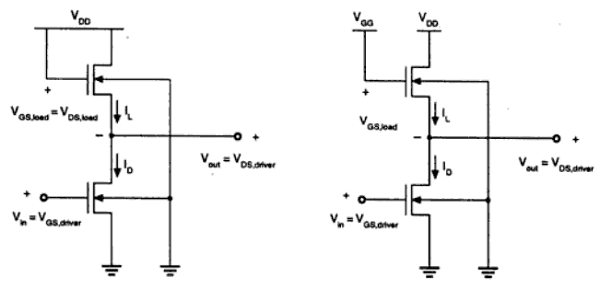

Các đặc điểm thể hiện trong hình là lý tưởng. Cấu trúc mạch tổng quát của biến tần nMOS được thể hiện trong hình bên dưới.

Từ hình cho trước, chúng ta có thể thấy rằng điện áp đầu vào của biến tần bằng cổng vào điện áp nguồn của bóng bán dẫn nMOS và điện áp đầu ra của biến tần bằng điện áp nguồn của bóng bán dẫn nMOS. Nguồn đến điện áp nền của nMOS còn được gọi là trình điều khiển cho bóng bán dẫn được nối đất; nên V SS = 0. Nút đầu ra được nối với một điện dung gộp dùng cho VTC.

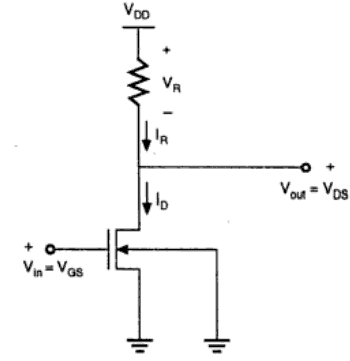

Biến tần tải điện trở

Cấu trúc cơ bản của biến tần tải điện trở được thể hiện trong hình bên dưới. Ở đây, nMOS loại nâng cao hoạt động như bóng bán dẫn trình điều khiển. Tải bao gồm một đơn giản tuyến tính điện trở R L . Việc cung cấp điện của mạch là V DD và cống hiện tại tôi D là tương đương với tải trọng hiện tại tôi R .

Hoạt động mạch

Khi đầu vào của bóng bán dẫn trình điều khiển nhỏ hơn điện áp ngưỡng V TH (V in <V TH ), bóng bán dẫn điều khiển nằm trong vùng cắt và không dẫn bất kỳ dòng điện nào. Vì vậy, điện áp rơi trên điện trở tải là KHÔNG và điện áp đầu ra bằng V DD . Bây giờ, khi điện áp đầu vào tăng hơn nữa, bóng bán dẫn điều khiển sẽ bắt đầu dẫn dòng khác 0 và nMOS đi trong vùng bão hòa.

Về mặt toán học,

$$I_{D} = \frac{K_{n}}{2}\left [ V_{GS}-V_{TO} \right ]^{2}$$

Tăng điện áp đầu vào hơn nữa, bóng bán dẫn trình điều khiển sẽ đi vào vùng tuyến tính và đầu ra của bóng bán dẫn điều khiển giảm.

$$I_{D} = \frac{K_{n}}{2}2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2}$$

VTC của biến tần tải điện trở, được hiển thị bên dưới, cho biết chế độ hoạt động của bóng bán dẫn trình điều khiển và các điểm điện áp.

Biến tần với tải MOSFET loại N

Ưu điểm chính của việc sử dụng MOSFET làm thiết bị tải là diện tích silicon được sử dụng bởi bóng bán dẫn nhỏ hơn diện tích chiếm bởi tải điện trở. Ở đây, MOSFET là tải hoạt động và biến tần có tải hoạt động cho hiệu suất tốt hơn so với biến tần có tải điện trở.

Tải nâng cao NMOS

Hai biến tần với thiết bị tải kiểu nâng cao được thể hiện trong hình. Bóng bán dẫn tải có thể được vận hành, trong vùng bão hòa hoặc trong vùng tuyến tính, tùy thuộc vào điện áp phân cực được áp dụng cho cực cổng của nó. Biến tần tải tăng cường bão hòa được hiển thị trong hình. (a). Nó đòi hỏi một nguồn cung cấp điện áp đơn và quá trình chế tạo đơn giản và do đó V OH được giới hạn ở những V DD - V T .

Biến tần tải tăng cường tuyến tính được hiển thị trong hình. (b). Nó luôn hoạt động trong vùng tuyến tính; nên V OH bằng V DD .

Biến tần tải tuyến tính có biên độ nhiễu cao hơn so với biến tần tăng cường bão hòa. Tuy nhiên, nhược điểm của biến tần tăng cường tuyến tính là nó yêu cầu hai nguồn điện riêng biệt và cả hai mạch đều bị tiêu tán công suất cao. Do đó, biến tần tăng cường không được sử dụng trong bất kỳ ứng dụng kỹ thuật số quy mô lớn nào.

Tải cạn kiệt NMOS

Hạn chế của bộ biến tần phụ tải nâng cao có thể được khắc phục bằng cách sử dụng bộ biến tần tải suy giảm. So với biến tần tải nâng cao, biến tần tải suy giảm yêu cầu thêm vài bước chế tạo để cấy kênh để điều chỉnh điện áp ngưỡng của tải.

Ưu điểm của bộ biến tần tải suy giảm là - chuyển tiếp VTC sắc nét, biên độ nhiễu tốt hơn, cấp nguồn đơn và diện tích bố trí tổng thể nhỏ hơn.

Như trong hình, cổng và đầu cuối nguồn của tải được kết nối; Vì vậy, V GS = 0. Như vậy, điện áp ngưỡng của tải là âm. Vì thế,

$$V_{GS,load}> V_{T,load}$$ đã hài lòng

Do đó, thiết bị tải luôn có kênh dẫn không phụ thuộc vào mức điện áp đầu vào và đầu ra.

Khi bóng bán dẫn tải ở trong vùng bão hòa, dòng tải được cho bởi

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ -V_{T,load}\left ( V_{out} \right ) \right ]^{2}$$

Khi bóng bán dẫn tải ở trong vùng tuyến tính, dòng tải được cho bởi

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ 2\left | V_{T,load}\left ( V_{out} \right ) \right |.\left ( V_{DD}-V_{out} \right )-\left ( V_{DD}-V_{out} \right )^{2} \right ]$$

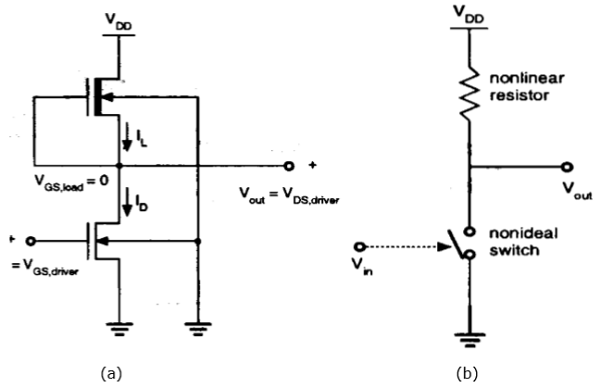

Đặc tính truyền điện áp của biến tần tải suy giảm được thể hiện trong hình bên dưới:

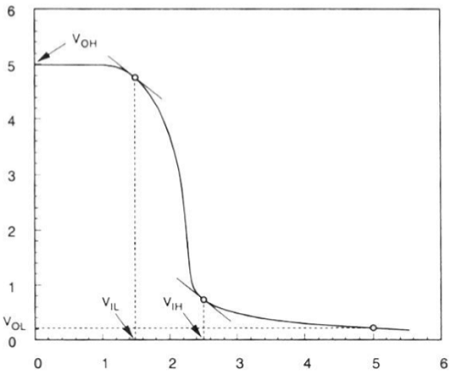

Biến tần CMOS - Mạch, Hoạt động và Mô tả

Mạch biến tần CMOS được hiển thị trong hình. Ở đây, bóng bán dẫn nMOS và pMOS hoạt động như bóng bán dẫn trình điều khiển; khi một bóng bán dẫn BẬT, bóng bán dẫn khác TẮT.

Cấu hình này được gọi là complementary MOS (CMOS). Đầu vào được kết nối với cực cổng của cả hai bóng bán dẫn sao cho cả hai đều có thể được điều khiển trực tiếp với điện áp đầu vào. Chất nền của nMOS được kết nối với mặt đất và chất nền của pMOS được kết nối với nguồn điện, V DD .

Vì vậy, V SB = 0 cho cả hai bóng bán dẫn.

$$V_{GS,n}=V_{in}$$

$$V_{DS,n}=V_{out}$$

Và,

$$V_{GS,p}=V_{in}-V_{DD}$$

$$V_{DS,p}=V_{out}-V_{DD}$$

Khi đầu vào của nMOS nhỏ hơn điện áp ngưỡng (V in <V TO, n ), nMOS bị ngắt và pMOS ở trong vùng tuyến tính. Vì vậy, dòng chảy của cả hai bóng bán dẫn bằng không.

$$I_{D,n}=I_{D,p}=0$$

Do đó, điện áp đầu ra V OH bằng điện áp cung cấp.

$$V_{out}=V_{OH}=V_{DD}$$

Khi điện áp đầu vào lớn hơn V DD + V TO, p , bóng bán dẫn pMOS nằm trong vùng cắt và nMOS nằm trong vùng tuyến tính, do đó dòng tiêu của cả hai bóng bán dẫn bằng không.

$$I_{D,n}=I_{D,p}=0$$

Do đó, điện áp đầu ra V OL bằng không.

$$V_{out}=V_{OL}=0$$

NMOS hoạt động trong vùng bão hòa nếu V in > V TO và nếu các điều kiện sau được thỏa mãn.

$$V_{DS,n}\geq V_{GS,n}-V_{TO,n} $$

$$V_{out}\geq V_{in}-V_{TO,n} $$

PMOS hoạt động trong vùng bão hòa nếu V trong <V DD + V TO, p và nếu các điều kiện sau được thỏa mãn.

$$V_{DS,p}\leq V_{GS,p}-V_{TO,p} $$

$$V_{out}\leq V_{in}-V_{TO,p} $$

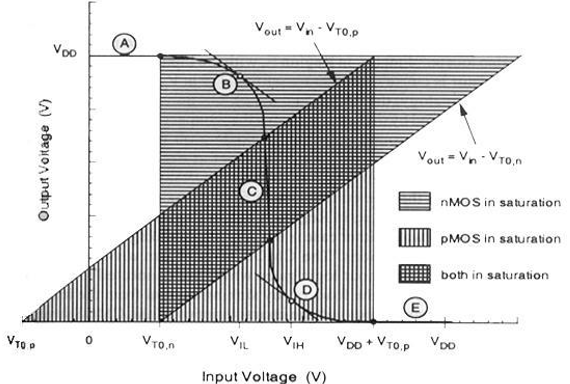

Đối với các giá trị khác nhau của điện áp đầu vào, các vùng hoạt động được liệt kê dưới đây cho cả hai bóng bán dẫn.

| Khu vực | V trong | V ra | nMOS | pMOS |

|---|---|---|---|---|

| A | <V TO, n | V OH | Cắt | Tuyến tính |

| B | V IL | ≈ V OH cao | Bão hòa | Tuyến tính |

| C | V th | V th | Bão hòa | Bão hòa |

| D | V IH | V CV thấp | Tuyến tính | Bão hòa |

| E | > (V DD + V TO, p ) | V CV | Tuyến tính | Cắt |

VTC của CMOS được thể hiện trong hình dưới đây -

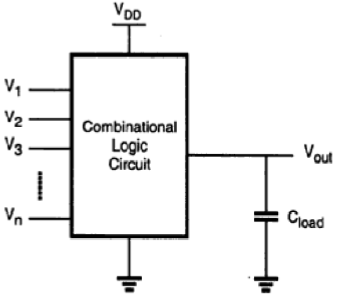

Các mạch hoặc cổng logic kết hợp, thực hiện các phép toán Boolean trên nhiều biến đầu vào và xác định đầu ra dưới dạng hàm Boolean của đầu vào, là các khối xây dựng cơ bản của tất cả các hệ thống kỹ thuật số. Chúng tôi sẽ xem xét các cấu hình mạch đơn giản như cổng NAND và cổng NOR hai đầu vào và sau đó mở rộng phân tích của chúng tôi sang các trường hợp tổng quát hơn của cấu trúc mạch nhiều đầu vào.

Tiếp theo, các mạch logic CMOS sẽ được trình bày theo cách tương tự. Chúng tôi sẽ nhấn mạnh những điểm giống và khác nhau giữa mạch logic tải cạn nMOS và mạch logic CMOS và chỉ ra những ưu điểm của cổng CMOS với các ví dụ. Ở dạng tổng quát nhất của nó, một mạch logic tổ hợp, hoặc cổng, thực hiện một hàm Boolean có thể được biểu diễn dưới dạng một hệ thống nhiều đầu vào, một đầu ra, như được mô tả trong hình.

Điện áp nút, được tham chiếu đến điện thế đất, đại diện cho tất cả các biến đầu vào. Sử dụng quy ước logic dương, giá trị Boolean (hoặc logic) của "1" có thể được biểu diễn bằng điện áp cao của VDD và giá trị Boolean (hoặc logic) của "0" có thể được biểu diễn bằng điện áp thấp là 0. Đầu ra nút được nạp một điện dung C L , biểu thị các điện dung tổng hợp của thiết bị ký sinh trong mạch.

Mạch logic CMOS

CMOS Hai cổng NOR đầu vào

Đoạn mạch gồm một n thuần mắc song song và một p thuần phụ mắc nối tiếp. Các điện áp đầu vào V X và V Y được áp dụng cho các cổng của một bóng bán dẫn nMOS và một bóng bán dẫn pMOS.

Khi một hoặc cả hai đầu vào ở mức cao, tức là khi n-net tạo ra một đường dẫn giữa nút đầu ra và mặt đất, thì p-net bị cắt. Nếu cả hai điện áp đầu vào đều thấp, tức là lưới n bị cắt, thì lưới p tạo ra một đường dẫn giữa nút đầu ra và điện áp nguồn.

Đối với bất kỳ kết hợp đầu vào nhất định nào, cấu trúc mạch bổ sung sao cho đầu ra được kết nối với V DD hoặc nối đất qua đường dẫn điện trở thấp và đường dẫn dòng điện một chiều giữa V DD và đất không được thiết lập cho bất kỳ kết hợp đầu vào nào. Điện áp đầu ra của CMOS, hai cổng NOR đầu vào sẽ nhận được điện áp thấp-logic là V OL = 0 và điện áp cao-logic là V OH = V DD . Phương trình của điện áp ngưỡng chuyển mạch thứ V được cho bởi

$$V_{th}\left ( NOR2 \right ) = \frac{V_{T,n}+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}}}$$

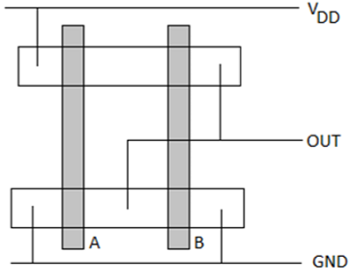

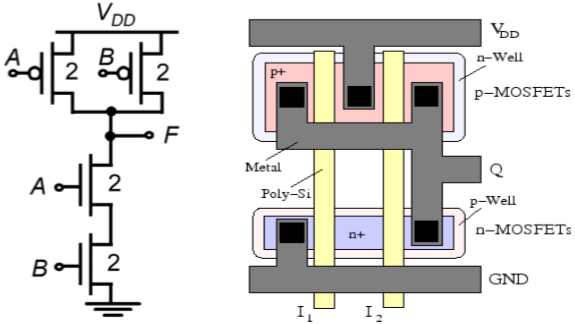

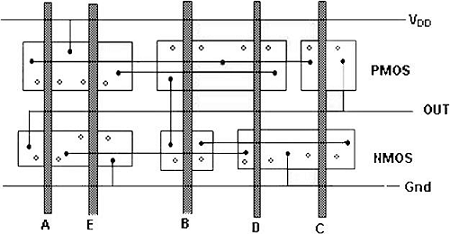

Bố cục của Cổng NOR 2 đầu vào CMOS

Hình bên cho thấy bố trí mẫu của cổng NOR 2 đầu vào CMOS, sử dụng kim loại một lớp và polysilicon một lớp. Các tính năng của bố cục này là -

- Nhiều đường thẳng đứng đơn cho mỗi đầu vào

- Các hình dạng hoạt động đơn lẻ cho các thiết bị N và P, tương ứng

- Xe buýt kim loại chạy ngang

Sơ đồ thanh cho cổng CMOS N0R2 được hiển thị trong hình bên dưới; tương ứng trực tiếp với bố cục, nhưng không chứa thông tin W và L. Các khu vực khuếch tán được mô tả bằng hình chữ nhật, các kết nối kim loại và các đường liền khối và vòng tròn, tương ứng đại diện cho các điểm tiếp xúc, và các dải gạch chéo thể hiện các cột đa giác. Sơ đồ thanh rất hữu ích để lập kế hoạch cấu trúc liên kết bố cục tối ưu.

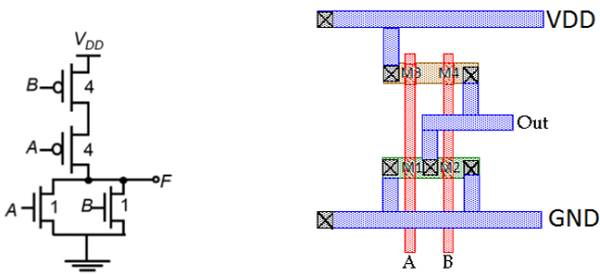

Cổng NAND hai đầu vào CMOS

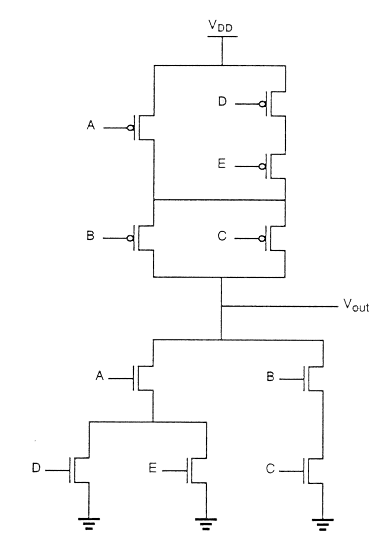

Sơ đồ mạch của hai cổng CMOS NAND đầu vào được cho trong hình bên dưới.

Nguyên tắc hoạt động của mạch là kép chính xác của hoạt động NOR hai đầu vào CMOS. N - net bao gồm hai bóng bán dẫn nMOS mắc nối tiếp tạo ra một đường dẫn giữa nút đầu ra và mặt đất, nếu cả hai điện áp đầu vào đều ở mức logic cao. Cả hai bóng bán dẫn pMOS được kết nối song song trong p-net sẽ bị tắt.

Đối với tất cả các kết hợp đầu vào khác, một hoặc cả hai bóng bán dẫn pMOS sẽ được BẬT, trong khi p-net bị ngắt, do đó, tạo ra một đường dẫn dòng điện giữa nút đầu ra và điện áp nguồn. Ngưỡng chuyển đổi cho cổng này nhận được là:

$$V_{th}\left ( NAND2 \right ) = \frac{V_{T,n}+2\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+2\sqrt{\frac{k_{p}}{k_{n}}}}$$

Các tính năng của bố cục này như sau:

- Các đường polysilicon đơn cho đầu vào chạy dọc trên cả vùng hoạt động N và P.

- Các hình dạng hoạt động đơn lẻ được sử dụng để tạo cả thiết bị nMOS và cả thiết bị pMOS.

- Đường dẫn điện chạy ngang trên cùng và dưới cùng của bố cục.

- Dây đầu ra chạy ngang để dễ dàng kết nối với mạch lân cận.

Mạch logic phức tạp

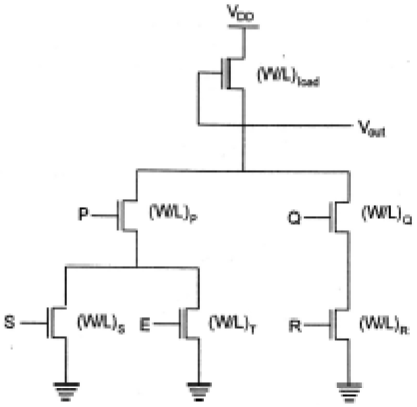

Cổng logic phức tạp tải cạn NMOS

Để thực hiện các chức năng phức tạp của nhiều biến đầu vào, các cấu trúc mạch cơ bản và các nguyên tắc thiết kế được phát triển cho NOR và NAND có thể được mở rộng cho các cổng logic phức tạp. Khả năng nhận ra các hàm logic phức tạp, sử dụng một số lượng nhỏ bóng bán dẫn là một trong những đặc điểm hấp dẫn nhất của mạch logic nMOS và CMOS. Hãy xem xét hàm Boolean sau đây làm ví dụ.

$$\overline{Z=P\left ( S+T \right )+QR}$$

Cổng logic phức tạp tải cạn nMOS được sử dụng để thực hiện chức năng này được thể hiện trong hình. Trong hình này, nhánh trình điều khiển nMOS bên trái của ba bóng bán dẫn trình điều khiển được sử dụng để thực hiện chức năng logic P (S + T), trong khi nhánh bên phải thực hiện chức năng QR. Bằng cách kết nối hai nhánh song song và bằng cách đặt bóng bán dẫn tải giữa nút đầu ra và điện áp cung cấpVDD,chúng ta có được hàm phức đã cho. Mỗi biến đầu vào chỉ được gán cho một trình điều khiển.

Kiểm tra cấu trúc liên kết mạch cung cấp các nguyên tắc thiết kế đơn giản của mạng kéo xuống -

- Các hoạt động HOẶC được thực hiện bởi các trình điều khiển được kết nối song song.

- Các hoạt động AND được thực hiện bởi các trình điều khiển được kết nối theo chuỗi.

- Sự nghịch đảo được cung cấp bởi bản chất của hoạt động mạch MOS.

Nếu tất cả các biến đầu vào có mức logic cao trong mạch thực hiện chức năng, trình điều khiển tương đương (W/L) tỷ lệ của mạng kéo xuống bao gồm năm bóng bán dẫn nMOS là

$$\frac{W}{L}=\frac{1}{\frac{1}{\left ( W/L \right )Q}+\frac{1}{\left ( W/L \right )R}}+\frac{1}{\frac{1}{\left ( W/L \right )P}+\frac{1}{\left ( W/L \right )S+\left ( W/L \right )Q}}$$

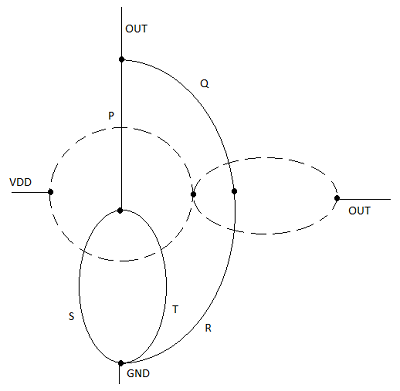

Cổng logic CMOS phức tạp

Việc thực hiện mạng n-net, hay mạng kéo xuống, dựa trên các nguyên tắc thiết kế cơ bản tương tự được kiểm tra đối với cổng logic phức tạp tải suy giảm nMOS. Mạng kéo lên pMOS phải là mạng kép của n-net.

Nó có nghĩa là tất cả các kết nối song song trong mạng nMOS sẽ tương ứng với kết nối nối tiếp trong mạng pMOS và tất cả kết nối nối tiếp trong mạng nMOS tương ứng với kết nối song song trong mạng pMOS. Hình bên cho thấy một cấu trúc đơn giản của đồ thị p-net kép (kéo lên) từ đồ thị n-net (kéo xuống).

Mỗi bóng bán dẫn trình điều khiển trong mạng kéo xuống được hiển thị bằng ai và mỗi nút được hiển thị bằng một đỉnh trong đồ thị kéo xuống. Tiếp theo, một đỉnh mới được tạo trong mỗi vùng giới hạn trong đồ thị kéo và các đỉnh lân cận được nối với nhau bằng các cạnh mà chỉ vượt qua mỗi cạnh trong đồ thị kéo xuống một lần. Biểu đồ mới này cho thấy mạng kéo lên.

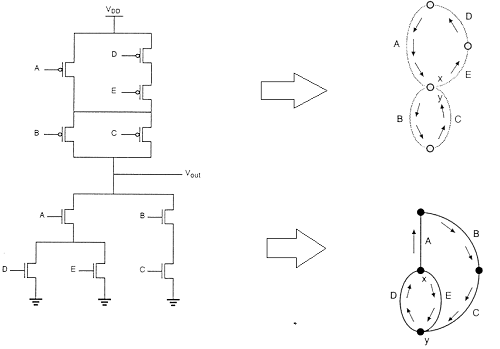

Kỹ thuật bố cục sử dụng phương pháp đồ thị Euler

Hình bên cho thấy việc triển khai CMOS của một chức năng phức tạp và sơ đồ thanh của nó được thực hiện với thứ tự cổng tùy ý tạo ra bố cục không tối ưu cho cổng CMOS.

Trong trường hợp này, sự phân tách giữa các cột polysilicon phải cho phép phân tách khuếch tán-todiffusion ở giữa. Điều này chắc chắn tiêu tốn đáng kể diện tích silicon bổ sung.

Bằng cách sử dụng đường dẫn Euler, chúng ta có thể có được một bố cục tối ưu. Đường Euler được định nghĩa là một đường không bị gián đoạn đi qua mỗi cạnh (nhánh) của biểu đồ đúng một lần. Tìm đường dẫn Euler trong cả biểu đồ cây kéo xuống và đồ thị cây kéo lên với thứ tự đầu vào giống hệt nhau.

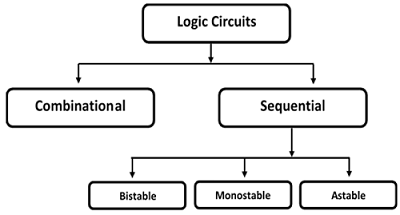

Mạch logic được chia thành hai loại - (a) Mạch kết hợp, và (b) Mạch tuần tự.

Trong mạch Kết hợp, đầu ra chỉ phụ thuộc vào điều kiện của đầu vào mới nhất.

Trong mạch tuần tự, đầu ra không chỉ phụ thuộc vào đầu vào mới nhất mà còn phụ thuộc vào điều kiện của đầu vào trước đó. Các mạch tuần tự chứa các phần tử nhớ.

Các mạch tuần tự có ba loại:

Bistable- Mạch điện có hai điểm hoạt động ổn định và sẽ ở một trong hai trạng thái. Ví dụ - Các ô nhớ, chốt, flip-flop và thanh ghi.

Monostable- Các mạch đơn ổn chỉ có một điểm hoạt động ổn định và ngay cả khi chúng bị xáo trộn tạm thời sang trạng thái ngược lại, chúng sẽ kịp thời quay trở lại điểm hoạt động ổn định. Ví dụ: Bộ định thời, bộ tạo xung.

Astable- mạch không có điểm hoạt động ổn định và dao động giữa một số trạng thái. Ví dụ - Bộ dao động vòng.

Mạch logic CMOS

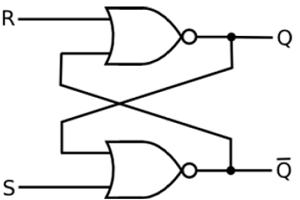

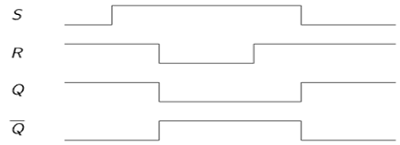

SR Latch dựa trên Cổng NOR

Nếu đầu vào đã đặt (S) bằng logic "1" và đầu vào đặt lại bằng logic "0." thì đầu ra Q sẽ buộc phải logic "1". Trong khi$\overline{Q}$ buộc phải logic "0". Điều này có nghĩa là chốt SR sẽ được thiết lập, bất kể trạng thái trước đó của nó.

Tương tự, nếu S bằng "0" và R bằng "1" thì đầu ra Q sẽ buộc phải "0" trong khi $\overline{Q}$ buộc phải "1". Điều này có nghĩa là chốt được đặt lại, bất kể trạng thái được giữ trước đó của nó. Cuối cùng, nếu cả hai đầu vào S và R bằng logic"1" thì cả hai đầu ra sẽ được buộc phải logic "0" mâu thuẫn với tính bổ sung của Q và $\overline{Q}$.

Do đó, kết hợp đầu vào này không được phép trong quá trình hoạt động bình thường. Bảng sự thật của chốt SR dựa trên NOR được đưa ra trong bảng.

| S | R | Q | $\overline{Q}$ | Hoạt động |

|---|---|---|---|---|

| 0 | 0 | Q | $\overline{Q}$ | Giữ |

| 1 | 0 | 1 | 0 | Bộ |

| 0 | 1 | 0 | 1 | Cài lại |

| 1 | 1 | 0 | 0 | Không cho phép |

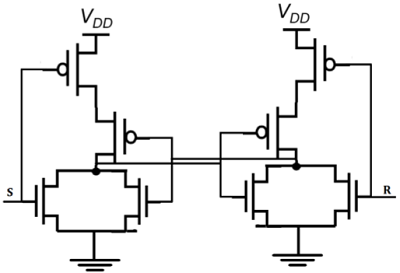

Chốt CMOS SR dựa trên cổng NOR được hiển thị trong hình bên dưới.

Nếu S bằng V OH và R bằng V OL thì cả hai bóng bán dẫn mắc song song M1 và M2 sẽ ON. Điện áp trên nút$\overline{Q}$sẽ giả sử mức logic thấp là V OL = 0.

Đồng thời, cả M3 và M4 đều bị tắt, dẫn đến điện áp cao logic V OH tại nút Q. Nếu R bằng V OH và S bằng V OL , M1 và M2 bị tắt và M3 và M4 đã bật.

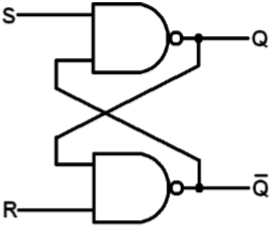

SR Latch dựa trên Cổng NAND

Sơ đồ khối và sơ đồ mức cổng của chốt SR dựa trên NAND được thể hiện trong hình. Các vòng tròn nhỏ ở các cực đầu vào S và R biểu thị rằng mạch phản ứng với các tín hiệu đầu vào thấp đang hoạt động. Bảng sự thật của chốt SR dựa trên NAND được đưa ra trong bảng

| S | R | Q | Q ′ | |

| 0 | 0 | NC | NC | Không thay đổi. Chốt vẫn ở trạng thái hiện tại. |

| 1 | 0 | 1 | 0 | Latch SET. |

| 0 | 1 | 0 | 1 | Chốt ĐẶT LẠI. |

| 1 | 1 | 0 | 0 | Điều kiện không hợp lệ. |

Nếu S tiến về 0 (trong khi R = 1), Q lên cao, kéo $\overline{Q}$ thấp và chốt chuyển sang trạng thái Đặt

S = 0 thì Q = 1 (nếu R = 1)

Nếu R tiến về 0 (trong khi S = 1), Q lên cao, kéo $\overline{Q}$ thấp và chốt được Đặt lại

R = 0 thì Q = 1 (nếu S = 1)

Trạng thái giữ yêu cầu cả S và R phải cao. Nếu S = R = 0 thì đầu ra không được phép, vì nó sẽ dẫn đến trạng thái không xác định. CMOS SR Latch dựa trên Cổng NAND được thể hiện trong hình.

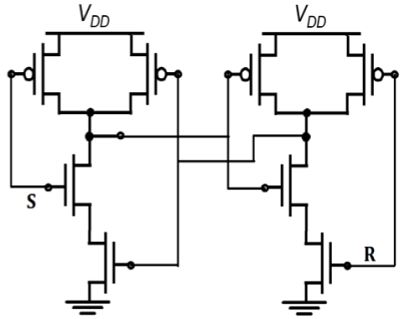

NMOS SR Latch cạn kiệt tải dựa trên Cổng NAND được thể hiện trong hình. Hoạt động tương tự như của chốt CMOS NAND SR. Việc triển khai mạch CMOS có khả năng tiêu tán công suất tĩnh thấp và biên độ nhiễu cao.

Mạch logic CMOS

Chốt SR được khóa

Hình cho thấy chốt SR dựa trên NOR có thêm đồng hồ. Chốt chỉ đáp ứng với đầu vào S và R khi CLK cao.

Khi CLK thấp, chốt giữ nguyên trạng thái hiện tại của nó. Quan sát Q thay đổi trạng thái -

- Khi S tăng cao trong CLK dương.

- Trên cạnh CLK hàng đầu sau những thay đổi trong S & R trong thời gian CLK thấp.

- Một trục trặc tích cực trong S trong khi CLK cao

- Khi R tăng cao trong CLK dương.

Việc triển khai CMOS AOI của chốt SR dựa trên NOR xung nhịp được thể hiện trong hình. Lưu ý rằng chỉ cần 12 bóng bán dẫn.

Khi CLK ở mức thấp, hai thiết bị đầu cuối nối tiếp trong N cây N mở và hai bóng bán dẫn song song trong cây P được BẬT, do đó vẫn giữ trạng thái trong ô nhớ.

Khi xung nhịp cao, mạch đơn giản trở thành chốt CMOS dựa trên NOR sẽ phản hồi với đầu vào S và R.

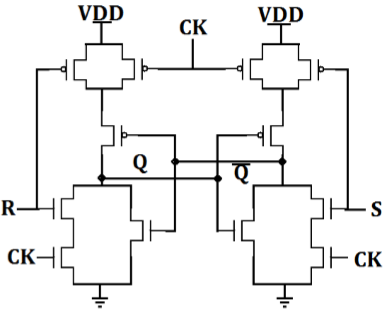

Clocked SR Latch based on NAND Gate

Mạch được thực hiện với bốn cổng NAND. Nếu mạch này được thực hiện với CMOS thì nó yêu cầu 16 bóng bán dẫn.

- Chốt chỉ phản hồi với S hoặc R nếu CLK cao.

- Nếu cả hai tín hiệu đầu vào và tín hiệu CLK đều hoạt động ở mức cao: tức là, đầu ra chốt Q sẽ được đặt khi CLK = "1" S = "1" và R = "0"

- Tương tự, chốt sẽ được đặt lại khi CLK = "1," S = "0" và

Khi CLK thấp, chốt giữ nguyên trạng thái hiện tại.

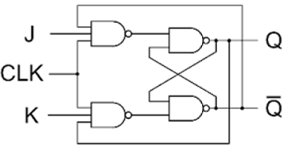

Chốt JK được khóa

Hình trên cho thấy một chốt JK có xung nhịp, dựa trên các cổng NAND. Nhược điểm của chốt SR là khi cả S và R đều ở mức cao, trạng thái đầu ra của nó trở nên không xác định. Chốt JK loại bỏ vấn đề này bằng cách sử dụng phản hồi từ đầu ra đến đầu vào, sao cho tất cả các trạng thái đầu vào của bảng chân trị đều cho phép. Nếu J = K = 0, chốt sẽ giữ trạng thái hiện tại.

Nếu J = 1 và K = 0, chốt sẽ đặt trên cạnh đồng hồ dương tiếp theo, tức là Q = 1, $\overline{Q}$ = 0

Nếu J = 0 và K = 1, chốt sẽ đặt lại trên cạnh đồng hồ tích cực tiếp theo, tức là Q = 1 và $\overline{Q}$ = 0.

Nếu J = K = 1, chốt sẽ chuyển đổi trên cạnh đồng hồ dương tiếp theo

Hoạt động của chốt JK đồng hồ được tóm tắt trong bảng sự thật được đưa ra trong bảng.

J |

K |

Q |

$\overline{Q}$ | S |

R |

Q |

$\overline{Q}$ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Giữ |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | Cài lại |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | Bộ |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | chuyển đổi |

| 1 | 0 | 1 | 0 | 0 | 1 |

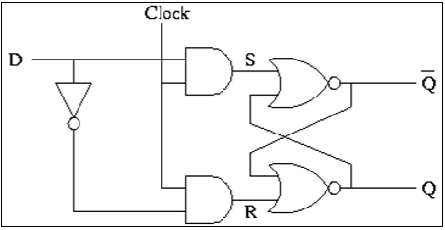

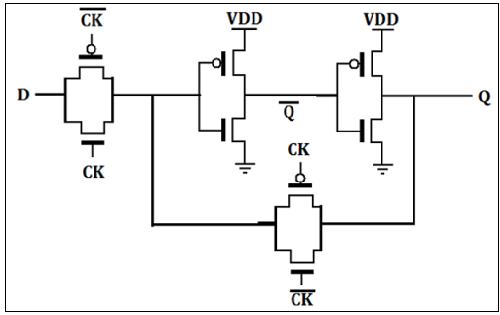

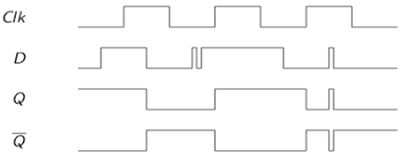

Triển khai chốt CMOS D

Chốt D thông thường, được thực hiện với các công tắc cổng truyền (TG) như thể hiện trong hình. TG đầu vào được kích hoạt với CLK trong khi TG vòng phản hồi chốt được kích hoạt với CLK. Đầu vào D được chấp nhận khi CLK cao. Khi CLK xuống thấp, đầu vào được mở và chốt được đặt với dữ liệu trước đó D.

VHDL là viết tắt của ngôn ngữ mô tả phần cứng mạch tích hợp tốc độ rất cao. Nó là một ngôn ngữ lập trình được sử dụng để mô hình một hệ thống kỹ thuật số theo luồng dữ liệu, hành vi và phong cách cấu trúc của mô hình hóa. Ngôn ngữ này lần đầu tiên được giới thiệu vào năm 1981 cho Bộ Quốc phòng (DoD) theo chương trình VHSIC.

Mô tả một thiết kế

Trong VHDL một thực thể được sử dụng để mô tả một mô-đun phần cứng. Một thực thể có thể được mô tả bằng cách sử dụng,

- Khai báo thực thể

- Architecture

- Configuration

- Khai báo gói hàng

- Gói thân

Hãy xem đây là những gì?

Khai báo thực thể

Nó xác định tên, tín hiệu đầu ra đầu vào và chế độ của mô-đun phần cứng.

Syntax -

entity entity_name is

Port declaration;

end entity_name;Một khai báo thực thể phải bắt đầu bằng 'thực thể' và kết thúc bằng từ khóa 'kết thúc'. Hướng sẽ là đầu vào, đầu ra hoặc inout.

| Trong | Cổng có thể được đọc |

| Ngoài | Cổng có thể được viết |

| Inout | Cổng có thể được đọc và ghi |

| Đệm | Cổng có thể được đọc và ghi, nó chỉ có thể có một nguồn. |

Architecture -

Kiến trúc có thể được mô tả bằng cách sử dụng cấu trúc, luồng dữ liệu, hành vi hoặc phong cách hỗn hợp.

Syntax -

architecture architecture_name of entity_name

architecture_declarative_part;

begin

Statements;

end architecture_name;Ở đây, chúng ta nên chỉ định tên thực thể mà chúng ta đang viết phần thân kiến trúc. Các câu lệnh kiến trúc phải nằm trong từ khóa 'begin' và 'énd'. Phần khai báo kiến trúc có thể chứa các biến, hằng số hoặc khai báo thành phần.

Mô hình luồng dữ liệu

Trong phong cách mô hình hóa này, luồng dữ liệu qua thực thể được thể hiện bằng cách sử dụng tín hiệu đồng thời (song song). Các câu lệnh đồng thời trong VHDL là WHEN và GENERATE.

Bên cạnh đó, các phép gán chỉ sử dụng toán tử (AND, NOT, +, *, sll, v.v.) cũng có thể được sử dụng để xây dựng mã.

Cuối cùng, một loại nhiệm vụ đặc biệt, được gọi là BLOCK, cũng có thể được sử dụng trong loại mã này.

Trong mã đồng thời, những điều sau có thể được sử dụng:

- Operators

- Câu lệnh WHEN (WHEN / ELSE hoặc WITH / SELECT / WHEN);

- Câu lệnh GENERATE;

- Câu lệnh BLOCK

Mô hình hành vi

Trong phong cách mô hình hóa này, hành vi của một thực thể với tư cách là tập hợp các câu lệnh được thực thi tuần tự theo thứ tự được chỉ định. Chỉ những câu lệnh được đặt bên trong một PROCESS, FUNCTION hoặc PROCEDURE là tuần tự.

QUY TRÌNH, CHỨC NĂNG và THỦ TỤC là những phần mã duy nhất được thực thi tuần tự.

Tuy nhiên, về tổng thể, bất kỳ khối nào trong số này vẫn đồng thời với bất kỳ câu lệnh nào khác được đặt bên ngoài nó.

Một khía cạnh quan trọng của mã hành vi là nó không giới hạn ở logic tuần tự. Thật vậy, với nó, chúng ta có thể xây dựng các mạch tuần tự cũng như mạch tổ hợp.

Các câu lệnh hành vi là IF, WAIT, CASE và LOOP. BIẾN TẦN cũng bị hạn chế và chúng chỉ được sử dụng trong mã tuần tự. VARIABLE không bao giờ có thể là toàn cục, vì vậy giá trị của nó không thể được truyền trực tiếp.

Mô hình cấu trúc

Trong mô hình này, một thực thể được mô tả như một tập hợp các thành phần được kết nối với nhau. Một câu lệnh khởi tạo thành phần là một câu lệnh đồng thời. Do đó, thứ tự của các câu lệnh này không quan trọng. Phong cách cấu trúc của mô hình chỉ mô tả sự kết nối với nhau của các thành phần (được xem như hộp đen), mà không ngụ ý bất kỳ hành vi nào của bản thân các thành phần cũng như của thực thể mà chúng đại diện chung.

Trong mô hình cấu trúc, phần thân kiến trúc bao gồm hai phần - phần khai báo (trước từ khóa bắt đầu) và phần câu lệnh (sau từ khóa bắt đầu).

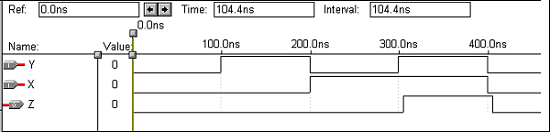

Hoạt động logic - VÀ CỔNG

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity and1 is

port(x,y:in bit ; z:out bit);

end and1;

architecture virat of and1 is

begin

z<=x and y;

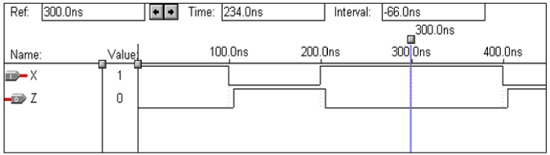

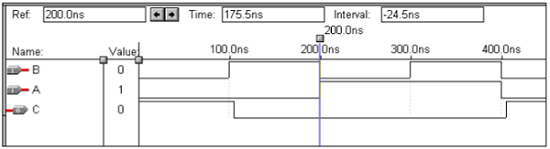

end virat;Dạng sóng

Hoạt động logic - Cổng HOẶC

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity or1 is

port(x,y:in bit ; z:out bit);

end or1;

architecture virat of or1 is

begin

z<=x or y;

end virat;Dạng sóng

Hoạt động logic - KHÔNG phải cổng

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity not1 is

port(x:in bit ; y:out bit);

end not1;

architecture virat of not1 is

begin

y<=not x;

end virat;Dạng sóng

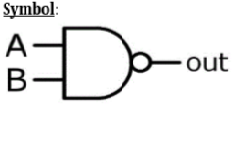

Hoạt động logic - Cổng NAND

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nand1 is

port(a,b:in bit ; c:out bit);

end nand1;

architecture virat of nand1 is

begin

c<=a nand b;

end virat;Dạng sóng

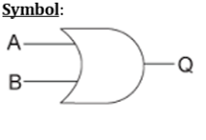

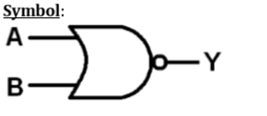

Hoạt động logic - Cổng NOR

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nor1 is

port(a,b:in bit ; c:out bit);

end nor1;

architecture virat of nor1 is

begin

c<=a nor b;

end virat;Dạng sóng

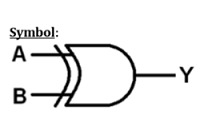

Hoạt động logic - Cổng XOR

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xor1 is

port(a,b:in bit ; c:out bit);

end xor1;

architecture virat of xor1 is

begin

c<=a xor b;

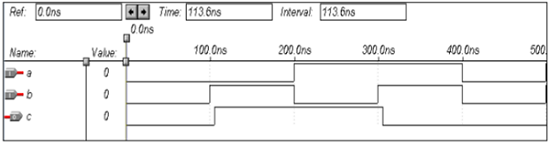

end virat;Dạng sóng

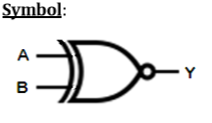

Hoạt động logic - Cổng X-NOR

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xnor1 is

port(a,b:in bit ; c:out bit);

end xnor1;

architecture virat of xnor1 is

begin

c<=not(a xor b);

end virat;Dạng sóng

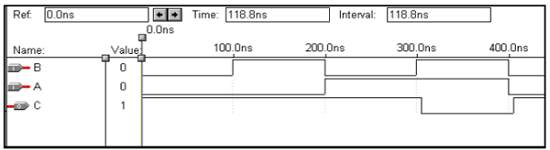

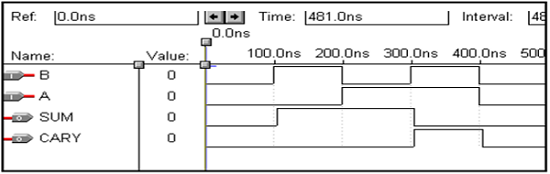

Chương này giải thích lập trình VHDL cho Mạch tổ hợp.

Mã VHDL dành cho người bán quảng cáo

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity half_adder is

port(a,b:in bit; sum,carry:out bit);

end half_adder;

architecture data of half_adder is

begin

sum<= a xor b;

carry <= a and b;

end data;Dạng sóng

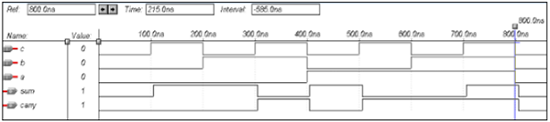

Mã VHDL cho nhà quảng cáo đầy đủ

Library ieee;

use ieee.std_logic_1164.all;

entity full_adder is port(a,b,c:in bit; sum,carry:out bit);

end full_adder;

architecture data of full_adder is

begin

sum<= a xor b xor c;

carry <= ((a and b) or (b and c) or (a and c));

end data;Dạng sóng

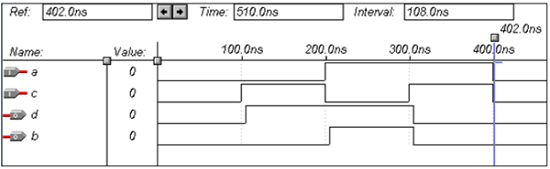

Mã VHDL cho Dấu trừ một nửa

Library ieee;

use ieee.std_logic_1164.all;

entity half_sub is

port(a,c:in bit; d,b:out bit);

end half_sub;

architecture data of half_sub is

begin

d<= a xor c;

b<= (a and (not c));

end data;Dạng sóng

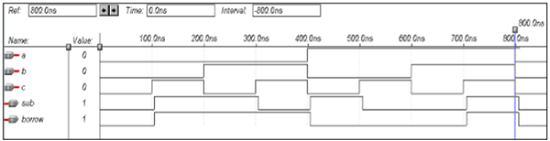

Mã VHDL cho Dấu trừ đầy đủ

Library ieee;

use ieee.std_logic_1164.all;

entity full_sub is

port(a,b,c:in bit; sub,borrow:out bit);

end full_sub;

architecture data of full_sub is

begin

sub<= a xor b xor c;

borrow <= ((b xor c) and (not a)) or (b and c);

end data;Dạng sóng

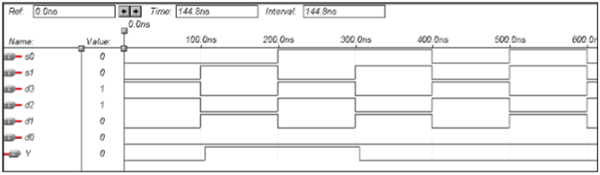

Mã VHDL cho Bộ ghép kênh

Library ieee;

use ieee.std_logic_1164.all;

entity mux is

port(S1,S0,D0,D1,D2,D3:in bit; Y:out bit);

end mux;

architecture data of mux is

begin

Y<= (not S0 and not S1 and D0) or

(S0 and not S1 and D1) or

(not S0 and S1 and D2) or

(S0 and S1 and D3);

end data;Dạng sóng

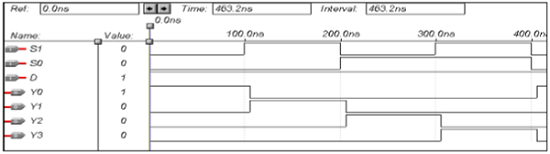

Mã VHDL cho Bộ phân kênh

Library ieee;

use ieee.std_logic_1164.all;

entity demux is

port(S1,S0,D:in bit; Y0,Y1,Y2,Y3:out bit);

end demux;

architecture data of demux is

begin

Y0<= ((Not S0) and (Not S1) and D);

Y1<= ((Not S0) and S1 and D);

Y2<= (S0 and (Not S1) and D);

Y3<= (S0 and S1 and D);

end data;Dạng sóng

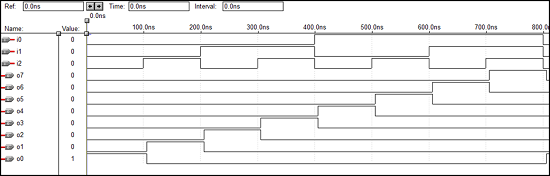

Mã VHDL cho bộ mã hóa 8 x 3

library ieee;

use ieee.std_logic_1164.all;

entity enc is

port(i0,i1,i2,i3,i4,i5,i6,i7:in bit; o0,o1,o2: out bit);

end enc;

architecture vcgandhi of enc is

begin

o0<=i4 or i5 or i6 or i7;

o1<=i2 or i3 or i6 or i7;

o2<=i1 or i3 or i5 or i7;

end vcgandhi;Dạng sóng

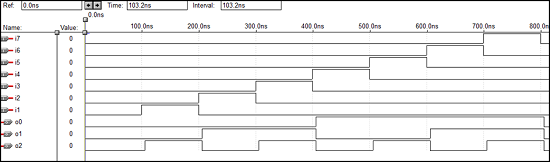

Mã VHDL cho Bộ giải mã 3 x 8

library ieee;

use ieee.std_logic_1164.all;

entity dec is

port(i0,i1,i2:in bit; o0,o1,o2,o3,o4,o5,o6,o7: out bit);

end dec;

architecture vcgandhi of dec is

begin

o0<=(not i0) and (not i1) and (not i2);

o1<=(not i0) and (not i1) and i2;

o2<=(not i0) and i1 and (not i2);

o3<=(not i0) and i1 and i2;

o4<=i0 and (not i1) and (not i2);

o5<=i0 and (not i1) and i2;

o6<=i0 and i1 and (not i2);

o7<=i0 and i1 and i2;

end vcgandhi;Dạng sóng

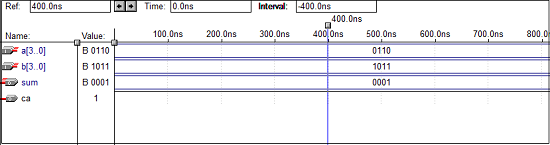

Mã VHDL - Bộ cộng song song 4 bit

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity pa is

port(a : in STD_LOGIC_VECTOR(3 downto 0);

b : in STD_LOGIC_VECTOR(3 downto 0);

ca : out STD_LOGIC;

sum : out STD_LOGIC_VECTOR(3 downto 0)

);

end pa;

architecture vcgandhi of pa is

Component fa is

port (a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

sum : out STD_LOGIC;

ca : out STD_LOGIC

);

end component;

signal s : std_logic_vector (2 downto 0);

signal temp: std_logic;

begin

temp<='0';

u0 : fa port map (a(0),b(0),temp,sum(0),s(0));

u1 : fa port map (a(1),b(1),s(0),sum(1),s(1));

u2 : fa port map (a(2),b(2),s(1),sum(2),s(2));

ue : fa port map (a(3),b(3),s(2),sum(3),ca);

end vcgandhi;Dạng sóng

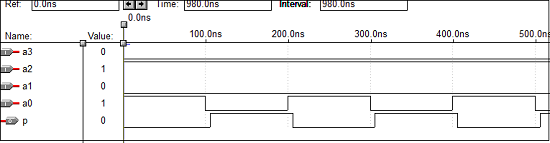

Mã VHDL - Bộ kiểm tra chẵn lẻ 4 bit

library ieee;

use ieee.std_logic_1164.all;

entity parity_checker is

port (a0,a1,a2,a3 : in std_logic;

p : out std_logic);

end parity_checker;

architecture vcgandhi of parity_checker is

begin

p <= (((a0 xor a1) xor a2) xor a3);

end vcgandhi;Dạng sóng

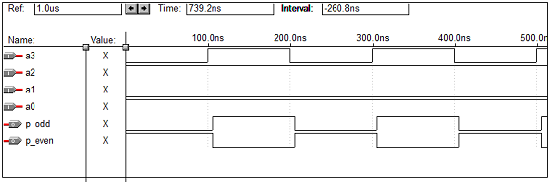

Mã VHDL - Bộ tạo chẵn lẻ 4 bit

library ieee;

use ieee.std_logic_1164.all;

entity paritygen is

port (a0, a1, a2, a3: in std_logic; p_odd, p_even: out std_logic);

end paritygen;

architecture vcgandhi of paritygen is

begin

process (a0, a1, a2, a3)

if (a0 ='0' and a1 ='0' and a2 ='0' and a3 =’0’)

then odd_out <= "0";

even_out <= "0";

else

p_odd <= (((a0 xor a1) xor a2) xor a3);

p_even <= not(((a0 xor a1) xor a2) xor a3);

end vcgandhiDạng sóng

Chương này giải thích cách lập trình VHDL cho Mạch tuần tự.

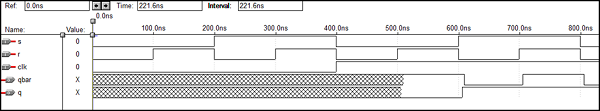

Mã VHDL cho SR Latch

library ieee;

use ieee.std_logic_1164.all;

entity srl is

port(r,s:in bit; q,qbar:buffer bit);

end srl;

architecture virat of srl is

signal s1,r1:bit;

begin

q<= s nand qbar;

qbar<= r nand q;

end virat;Dạng sóng

Mã VHDL cho một chốt D

library ieee;

use ieee.std_logic_1164.all;

entity Dl is

port(d:in bit; q,qbar:buffer bit);

end Dl;

architecture virat of Dl is

signal s1,r1:bit;

begin

q<= d nand qbar;

qbar<= d nand q;

end virat;Dạng sóng

Mã VHDL cho SR Flip Flop

library ieee;

use ieee.std_logic_1164.all;

entity srflip is

port(r,s,clk:in bit; q,qbar:buffer bit);

end srflip;

architecture virat of srflip is

signal s1,r1:bit;

begin

s1<=s nand clk;

r1<=r nand clk;

q<= s1 nand qbar;

qbar<= r1 nand q;

end virat;Dạng sóng

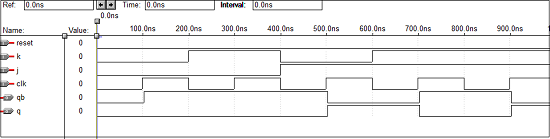

Mã VHDL cho JK Flip Flop

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity jk is

port(

j : in STD_LOGIC;

k : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

q : out STD_LOGIC;

qb : out STD_LOGIC

);

end jk;

architecture virat of jk is

begin

jkff : process (j,k,clk,reset) is

variable m : std_logic := '0';

begin

if (reset = '1') then

m : = '0';

elsif (rising_edge (clk)) then

if (j/ = k) then

m : = j;

elsif (j = '1' and k = '1') then

m : = not m;

end if;

end if;

q <= m;

qb <= not m;

end process jkff;

end virat;Dạng sóng

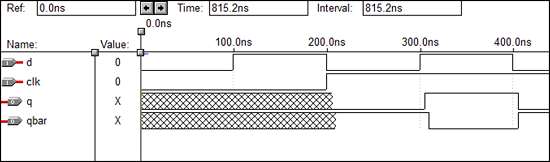

Mã VHDL cho D Flip Flop

Library ieee;

use ieee.std_logic_1164.all;

entity dflip is

port(d,clk:in bit; q,qbar:buffer bit);

end dflip;

architecture virat of dflip is

signal d1,d2:bit;

begin

d1<=d nand clk;

d2<=(not d) nand clk;

q<= d1 nand qbar;

qbar<= d2 nand q;

end virat;Dạng sóng

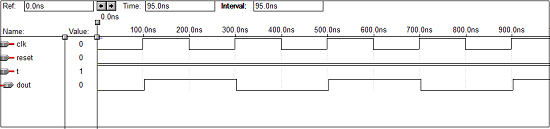

Mã VHDL cho T Flip Flop

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity Toggle_flip_flop is

port(

t : in STD_LOGIC;

clk : in STD_LOGIC;

reset : in STD_LOGIC;

dout : out STD_LOGIC

);

end Toggle_flip_flop;

architecture virat of Toggle_flip_flop is

begin

tff : process (t,clk,reset) is

variable m : std_logic : = '0';

begin

if (reset = '1') then

m : = '0';

elsif (rising_edge (clk)) then

if (t = '1') then

m : = not m;

end if;

end if;

dout < = m;

end process tff;

end virat;Dạng sóng

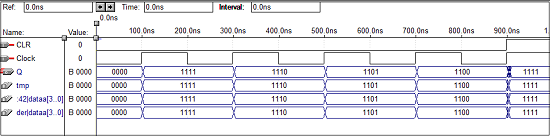

Mã VHDL cho bộ đếm lên 4 bit

library IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity counter is

port(Clock, CLR : in std_logic;

Q : out std_logic_vector(3 downto 0)

);

end counter;

architecture virat of counter is

signal tmp: std_logic_vector(3 downto 0);

begin

process (Clock, CLR)

begin

if (CLR = '1') then

tmp < = "0000";

elsif (Clock'event and Clock = '1') then

mp <= tmp + 1;

end if;

end process;

Q <= tmp;

end virat;Dạng sóng

Mã VHDL cho bộ đếm xuống 4 bit

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity dcounter is

port(Clock, CLR : in std_logic;

Q : out std_logic_vector(3 downto 0));

end dcounter;

architecture virat of dcounter is

signal tmp: std_logic_vector(3 downto 0);

begin

process (Clock, CLR)

begin

if (CLR = '1') then

tmp <= "1111";

elsif (Clock'event and Clock = '1') then

tmp <= tmp - 1;

end if;

end process;

Q <= tmp;

end virat;Dạng sóng

Verilog là một NGÔN NGỮ MÔ TẢ PHẦN CỨNG (HDL). Nó là một ngôn ngữ được sử dụng để mô tả một hệ thống kỹ thuật số như một bộ chuyển mạch mạng hoặc một bộ vi xử lý hoặc một bộ nhớ hoặc một flip-flop. Có nghĩa là, bằng cách sử dụng HDL, chúng ta có thể mô tả bất kỳ phần cứng kỹ thuật số nào ở bất kỳ cấp độ nào. Các thiết kế, được mô tả trong HDL độc lập với công nghệ, rất dễ thiết kế và gỡ lỗi, và thường hữu ích hơn so với sơ đồ, đặc biệt là đối với các mạch lớn.

Verilog hỗ trợ một thiết kế ở nhiều cấp độ trừu tượng. Ba yếu tố chính là -

- Mức độ hành vi

- Đăng ký-chuyển cấp

- Cấp cổng

Mức độ hành vi

Mức này mô tả một hệ thống bằng các thuật toán đồng thời (Behavioral). Mọi thuật toán đều tuần tự, có nghĩa là nó bao gồm một tập hợp các lệnh được thực hiện từng cái một. Chức năng, nhiệm vụ và khối là các yếu tố chính. Không liên quan đến hiện thực hóa cấu trúc của thiết kế.

Đăng ký-Mức chuyển

Các thiết kế sử dụng thanh ghi - Mức truyền xác định các đặc tính của mạch sử dụng các hoạt động và việc truyền dữ liệu giữa các thanh ghi. Định nghĩa hiện đại về mã RTL là "Bất kỳ mã nào có thể tổng hợp được gọi là mã RTL".

Mức cổng

Trong cấp độ logic, các đặc tính của hệ thống được mô tả bằng các liên kết logic và các thuộc tính thời gian của chúng. Tất cả các tín hiệu đều là tín hiệu rời rạc. Chúng chỉ có thể có các giá trị logic xác định (`` 0 ', `1',` X ', `Z`). Các hoạt động có thể sử dụng là các nguyên thủy logic được xác định trước (các cổng cơ bản). Mô hình hóa mức cổng có thể không phải là một ý tưởng đúng đắn cho thiết kế logic. Mã cấp cổng được tạo bằng các công cụ như công cụ tổng hợp và danh sách mạng của anh ấy được sử dụng để mô phỏng cấp cổng và cho phần phụ trợ.

Lexical Tokens

Các tệp văn bản nguồn ngôn ngữ Verilog là một dòng mã thông báo từ vựng. Mã thông báo bao gồm một hoặc nhiều ký tự và mỗi ký tự đơn lẻ nằm trong chính xác một mã thông báo.

Các mã thông báo từ vựng cơ bản được Verilog HDL sử dụng tương tự như các mã trong Ngôn ngữ lập trình C. Verilog phân biệt chữ hoa chữ thường. Tất cả các từ khóa đều ở dạng chữ thường.

Khoảng trắng

Khoảng trắng có thể chứa các ký tự cho khoảng trắng, tab, dòng mới và nguồn cấp dữ liệu biểu mẫu. Các ký tự này bị bỏ qua ngoại trừ khi chúng dùng để phân tách các mã thông báo.

Các ký tự khoảng trắng là Khoảng trắng, Tab, Trả hàng, Dòng mới và Nguồn cấp dữ liệu biểu mẫu.

Bình luận

Có hai hình thức để đại diện cho các nhận xét

- 1) Các chú thích một dòng bắt đầu bằng mã thông báo // và kết thúc bằng ký tự xuống dòng.

Ví dụ: // đây là cú pháp dòng đơn

- 2) Nhận xét nhiều dòng bắt đầu bằng mã thông báo / * và kết thúc bằng mã thông báo * /

Ví dụ: / * đây là Cú pháp đa dòng * /

Số

Bạn có thể chỉ định một số ở định dạng nhị phân, bát phân, thập phân hoặc thập lục phân. Số âm được thể hiện bằng số khen ngợi của 2. Verilog cho phép số nguyên, số thực và số có dấu & không dấu.

Cú pháp được đưa ra bởi - <size> <radix> <value>

Kích thước hoặc số không có kích thước có thể được xác định trong <Kích thước> và <radix> xác định xem nó là nhị phân, bát phân, thập lục phân hay thập phân.

Định danh

Định danh là tên được sử dụng để xác định đối tượng, chẳng hạn như một chức năng, mô-đun hoặc thanh ghi. Số nhận dạng phải bắt đầu bằng ký tự chữ cái hoặc ký tự gạch dưới. Ví dụ. A_Z, a_z, _

Số nhận dạng là sự kết hợp của các ký tự chữ cái, số, dấu gạch dưới và $. Chúng có thể dài tới 1024 ký tự.

Các nhà khai thác

Toán tử là các ký tự đặc biệt được sử dụng để đặt điều kiện hoặc vận hành các biến. Có một, hai và đôi khi ba ký tự được sử dụng để thực hiện các hoạt động trên các biến.

Ví dụ. >, +, ~, &! =.

Từ khóa Verilog

Các từ có ý nghĩa đặc biệt trong Verilog được gọi là từ khóa Verilog. Ví dụ: gán, trường hợp, trong khi, dây, reg và, hoặc, nand và mô-đun. Chúng không nên được sử dụng làm định danh. Các từ khóa Verilog cũng bao gồm các chỉ thị trình biên dịch, các nhiệm vụ và chức năng của hệ thống.

Mô hình hóa mức cổng

Verilog có các nguyên thủy tích hợp sẵn như cổng logic, cổng truyền và công tắc. Chúng hiếm khi được sử dụng cho công việc thiết kế nhưng chúng được sử dụng trong thế giới tổng hợp hậu để mô hình hóa các tế bào ASIC / FPGA.

Mô hình hóa mức cổng thể hiện hai thuộc tính:

Drive strength- Độ bền của các cổng ra được xác định bởi độ bền của ổ đĩa. Đầu ra mạnh nhất nếu có kết nối trực tiếp với nguồn. Cường độ giảm nếu kết nối qua bóng bán dẫn dẫn điện và ít nhất khi kết nối qua điện trở kéo lên / xuống. Cường độ ổ đĩa thường không được chỉ định, trong trường hợp này cường độ được mặc định là strong1 và strong0.

Delays- Nếu sự chậm trễ không được chỉ định, thì các cổng không có độ trễ lan truyền; nếu hai độ trễ được chỉ định, thì cái đầu tiên đại diện cho độ trễ tăng và cái thứ hai, độ trễ giảm; nếu chỉ có một độ trễ được chỉ định, thì cả hai, tăng và giảm đều bằng nhau. Sự chậm trễ có thể được bỏ qua trong quá trình tổng hợp.

Cổng nguyên thủy

Các cổng logic cơ bản sử dụng một đầu ra và nhiều đầu vào được sử dụng trong Verilog. GATE sử dụng một trong các từ khóa - và, nand hoặc, nor, xor, xnor để sử dụng trong Verilog cho N số đầu vào và 1 đầu ra.

Example:

Module gate()

Wire ot0;

Wire ot1;

Wire ot2;

Reg in0,in1,in2,in3;

Not U1(ot0,in0);

Xor U2(ot1,in1,in2,in3);

And U3(ot2, in2,in3,in0)Cổng truyền dẫn ban đầu

Cổng truyền động nguyên thủy bao gồm cả hai, bộ đệm và bộ biến tần. Chúng có đầu vào duy nhất và một hoặc nhiều đầu ra. Trong cú pháp khởi tạo cổng được hiển thị bên dưới, GATE là viết tắt của từ khóa buf hoặc cổng NOT.

Ví dụ: Not, buf, bufif0, bufif1, notif0, notif1

Biến tần không - n outout

Bộ đệm đầu ra Buf - n

Bufifo - bộ đệm tristate, kích hoạt hoạt động ở mức thấp

Bufif1 - bộ đệm tristate, kích hoạt cao hoạt động

Notifo - biến tần tristate, kích hoạt hoạt động ở mức thấp

Notif1 - biến tần tristate, kích hoạt cao hoạt động

Example:

Module gate()

Wire out0;

Wire out1;

Reg in0,in1;

Not U1(out0,in0);

Buf U2(out0,in0);Loại dữ liệu

Bộ giá trị

Verilog chủ yếu bao gồm bốn giá trị cơ bản. Tất cả các kiểu dữ liệu Verilog, được sử dụng trong Verilog đều lưu trữ các giá trị này -

0 (logic 0 hoặc điều kiện sai)

1 (logic một, hoặc điều kiện đúng)

x (giá trị logic không xác định)

z (trạng thái trở kháng cao)

việc sử dụng x và z rất hạn chế để tổng hợp.

Dây điện

Một dây được sử dụng để biểu thị một dây vật lý trong mạch và nó được sử dụng để kết nối các cổng hoặc mô-đun. Giá trị của một dây chỉ có thể được đọc và không được gán trong một hàm hoặc khối. Một dây không thể lưu trữ giá trị nhưng luôn được điều khiển bởi câu lệnh gán liên tục hoặc bằng cách kết nối dây với đầu ra của cổng / mô-đun. Các loại dây cụ thể khác là -

Wand (wired-AND) - ở đây giá trị của Wand phụ thuộc vào AND logic của tất cả các trình điều khiển thiết bị được kết nối với nó.

Wor (wired-OR) - ở đây giá trị của Wor phụ thuộc vào OR logic của tất cả các trình điều khiển thiết bị được kết nối với nó.

Tri (three-state) - ở đây tất cả các trình điều khiển được kết nối với một tri phải là z, ngoại trừ một (xác định giá trị của tri).

Example:

Wire [msb:lsb] wire_variable_list;

Wirec // simple wire

Wand d;

Assign d = a; // value of d is the logical AND of

Assign d = b; // a and b

Wire [9:0] A; // a cable (vector) of 10 wires.

Wand [msb:lsb] wand_variable_list;

Wor [msb:lsb] wor_variable_list;

Tri [msb:lsb] tri_variable_list;Đăng ký

Một reg (register) là một đối tượng dữ liệu, đang giữ giá trị từ lần gán thủ tục này sang lần gán thủ tục tiếp theo và chỉ được sử dụng trong các hàm và khối thủ tục khác nhau. Reg là một Verilog đơn giản, thanh ghi kiểu biến và không thể ngụ ý một thanh ghi vật lý. Trong thanh ghi nhiều bit, dữ liệu được lưu trữ dưới dạng số không dấu và phần mở rộng dấu không được sử dụng.

Ví dụ -

reg c; // biến thanh ghi 1 bit duy nhất

reg [5: 0] đá quý; // véc tơ 6 bit;

reg [6: 0] d, e; // hai biến 7 bit

Đầu vào, Đầu ra, Inout

Các từ khóa này được sử dụng để khai báo các cổng đầu vào, đầu ra và hai chiều của một tác vụ hoặc mô-đun. Ở đây các cổng đầu vào và cổng inout, thuộc loại dây và cổng đầu ra được cấu hình thành loại dây, reg, đũa, lo hoặc tri. Luôn luôn, mặc định là loại dây.

Example

Module sample(a, c, b, d);

Input c; // An input where wire is used.

Output a, b; // Two outputs where wire is used.

Output [2:0] d; /* A three-bit output. One must declare type in a separate statement. */

reg [1:0] a; // The above ‘a’ port is for declaration in reg.Số nguyên

Số nguyên được sử dụng trong các biến mục đích chung. Chúng được sử dụng chủ yếu trong các chỉ thị vòng lặp, hằng số và tham số. Chúng thuộc kiểu dữ liệu kiểu 'reg'. Chúng lưu trữ dữ liệu dưới dạng số có dấu trong khi các kiểu reg được khai báo rõ ràng lưu trữ chúng dưới dạng dữ liệu không dấu. Nếu số nguyên không được xác định tại thời điểm biên dịch, thì kích thước mặc định sẽ là 32 bit.

Nếu một số nguyên giữ một hằng số, bộ tổng hợp sẽ điều chỉnh chúng theo chiều rộng tối thiểu cần thiết tại thời điểm biên dịch.

Example

Integer c; // single 32-bit integer

Assign a = 63; // 63 defaults to a 7-bit variable.Cung 0, Cung 1

Supply0 xác định các dây gắn với logic 0 (nối đất) và cung cấp1 xác định các dây gắn với logic 1 (nguồn).

Example

supply0 logic_0_wires;

supply0 gnd1; // equivalent to a wire assigned as 0

supply1 logic_1_wires;

supply1 c, s;Thời gian

Thời gian là một đại lượng 64 bit có thể được sử dụng cùng với nhiệm vụ hệ thống $ time để giữ thời gian mô phỏng. Thời gian không được hỗ trợ để tổng hợp và do đó chỉ được sử dụng cho mục đích mô phỏng.

Example

time time_variable_list;

time c;

c = $time; //c = current simulation timeTham số

Một tham số xác định một hằng số có thể được đặt khi bạn sử dụng một mô-đun, cho phép tùy chỉnh mô-đun trong quá trình khởi tạo.

Example

Parameter add = 3’b010, sub = 2’b11;

Parameter n = 3;

Parameter [2:0] param2 = 3’b110;

reg [n-1:0] jam; /* A 3-bit register with length of n or above. */

always @(z)

y = {{(add - sub){z}};

if (z)

begin

state = param2[1];

else

state = param2[2];

endCác nhà khai thác

Toán tử số học

Các toán tử này đang thực hiện các phép toán số học. + Và −are được sử dụng như một toán tử đơn phân (x) hoặc nhị phân (z − y).

Các toán tử được bao gồm trong phép toán số học là:

+ (cộng), - (trừ), * (nhân), / (chia),% (môđun)

Example -

parameter v = 5;

reg[3:0] b, d, h, i, count;

h = b + d;

i = d - v;

cnt = (cnt +1)%16; //Can count 0 thru 15.Toán tử quan hệ

Các toán tử này so sánh hai toán hạng và trả về kết quả theo một bit, 1 hoặc 0.

Các biến wire và reg đều dương. Do đó (−3'd001) = = 3'd111 và (−3b001)> 3b110.

Các toán tử được bao gồm trong hoạt động quan hệ là:

- == (bằng)

- ! = (không bằng)

- > (lớn hơn)

- > = (lớn hơn hoặc bằng)

- <(nhỏ hơn)

- <= (nhỏ hơn hoặc bằng)

Example

if (z = = y) c = 1;

else c = 0; // Compare in 2’s compliment; d>b

reg [3:0] d,b;

if (d[3]= = b[3]) d[2:0] > b[2:0];

else b[3];

Equivalent Statement

e = (z == y);Các nhà điều hành khôn ngoan

Các toán tử khôn ngoan đang thực hiện so sánh từng bit giữa hai toán hạng.

Các toán tử được bao gồm trong hoạt động khôn ngoan của Bit là:

- & (bitwise AND)

- | (bitwiseOR)

- ~ (không theo bitwise)

- ^ (bitwise XOR)

- ~ ^ hoặc ^ ~ (bitwise XNOR)

Example

module and2 (d, b, c);

input [1:0] d, b;

output [1:0] c;

assign c = d & b;

end moduleToán tử logic

Các toán tử logic là các toán tử khôn ngoan và chỉ được sử dụng cho các toán hạng bit đơn. Chúng trả về một giá trị bit duy nhất, 0 hoặc 1. Chúng có thể hoạt động trên số nguyên hoặc nhóm bit, biểu thức và coi tất cả các giá trị khác 0 là 1. Các toán tử logic nói chung, được sử dụng trong các câu lệnh điều kiện vì chúng hoạt động với các biểu thức.

Các toán tử được bao gồm trong phép toán logic là:

- ! (logic KHÔNG)

- && (logic AND)

- || (logic HOẶC)

Example

wire[7:0] a, b, c; // a, b and c are multibit variables.

reg x;

if ((a == b) && (c)) x = 1; //x = 1 if a equals b, and c is nonzero.

else x = !a; // x =0 if a is anything but zero.Nhà điều hành Giảm

Toán tử giảm là dạng đơn nguyên của toán tử bit và hoạt động trên tất cả các bit của vectơ toán hạng. Chúng cũng trả về một giá trị bit đơn.

Các toán tử được bao gồm trong hoạt động Giảm là -

- & (giảm AND)

- | (giảm HOẶC)

- ~ & (giảm NAND)

- ~ | (giảm NOR)

- ^ (giảm XOR)

- ~ ^ hoặc ^ ~ (giảm XNOR)

Example

Module chk_zero (x, z);

Input [2:0] x;

Output z;

Assign z = & x; // Reduction AND

End moduleNgười điều hành ca

Toán tử Shift, đang dịch toán hạng đầu tiên theo số bit được chỉ định bởi toán hạng thứ hai trong cú pháp. Các vị trí trống được điền các số không cho cả hai chiều, dịch chuyển trái và phải (Không có phần mở rộng biển báo sử dụng).

Các toán tử được bao gồm trong hoạt động Shift là:

- << (dịch sang trái)

- >> (sang phải)

Example

Assign z = c << 3; /* z = c shifted left 3 bits;Các vị trí trống được điền bằng 0 * /

Điều hành nối

Toán tử nối kết hợp hai hoặc nhiều toán hạng để tạo thành một vectơ lớn hơn.

Toán tử được bao gồm trong phép toán Nối là - {} (nối)

Example

wire [1:0] a, h; wire [2:0] x; wire [3;0] y, Z;

assign x = {1’b0, a}; // x[2] = 0, x[1] = a[1], x[0] = a[0]

assign b = {a, h}; /* b[3] = a[1], b[2] = a[0], b[1] = h[1],

b[0] = h[0] */

assign {cout, b} = x + Z; // Concatenation of a resultNhà điều hành nhân rộng

Toán tử sao chép đang tạo nhiều bản sao của một mục.

Toán tử được sử dụng trong hoạt động sao chép là - {n {item}} (sao chép lần thứ n của một mục)

Example

Wire [1:0] a, f; wire [4:0] x;

Assign x = {2{1’f0}, a}; // Equivalent to x = {0,0,a }

Assign y = {2{a}, 3{f}}; //Equivalent to y = {a,a,f,f}

For synthesis, Synopsis did not like a zero replication.

For example:-

Parameter l = 5, k = 5;

Assign x = {(l-k){a}}Điều hành có điều kiện

Toán tử có điều kiện tổng hợp thành một bộ ghép kênh. Nó là loại tương tự như được sử dụng trong C / C ++ và đánh giá một trong hai biểu thức dựa trên điều kiện.

Toán tử được sử dụng trong hoạt động có điều kiện là -

(Tình trạng) ? (Kết quả nếu điều kiện đúng) -

(kết quả nếu điều kiện sai)

Example

Assign x = (g) ? a : b;

Assign x = (inc = = 2) ? x+1 : x-1;

/* if (inc), x = x+1, else x = x-1 */Toán hạng

Chữ viết

Literal là các toán hạng có giá trị không đổi được sử dụng trong biểu thức Verilog. Hai ký tự Verilog thường được sử dụng là:

String - Toán hạng theo nghĩa đen của chuỗi là một mảng một chiều các ký tự, được đặt trong dấu ngoặc kép ("").

Numeric - Một toán hạng số không đổi được chỉ định ở dạng Số nhị phân, bát phân, thập phân hoặc thập lục phân.

Example

n - số nguyên đại diện cho số bit

F - một trong bốn định dạng cơ sở có thể có -

b đối với hệ nhị phân, o đối với bát phân, d đối với thập phân, h đối với thập lục phân.

“time is” // string literal

267 // 32-bit decimal number

2’b01 // 2-bit binary

20’hB36F // 20-bit hexadecimal number

‘062 // 32-bit octal numberDây, Regs và Tham số

Wires, regs và tham số là các kiểu dữ liệu được sử dụng làm toán hạng trong biểu thức Verilog.

Lựa chọn bit “x [2]” và Lựa chọn từng phần “x [4: 2]”

Lựa chọn bit và chọn từng phần được sử dụng để chọn một bit và nhiều bit, tương ứng, từ một vectơ dây, reg hoặc tham số với việc sử dụng dấu ngoặc vuông “[]”. Các phép chọn bit và chọn một phần cũng được sử dụng như các toán hạng trong biểu thức giống như cách mà các đối tượng dữ liệu chính của chúng được sử dụng.

Example

reg [7:0] x, y;

reg [3:0] z;

reg a;

a = x[7] & y[7]; // bit-selects

z = x[7:4] + y[3:0]; // part-selectsGọi hàm

Trong các lệnh gọi Hàm, giá trị trả về của một hàm được sử dụng trực tiếp trong một biểu thức mà không cần gán nó vào một thanh ghi hoặc dây. Nó chỉ đặt lệnh gọi hàm như một trong những kiểu toán hạng. Nó cần thiết để đảm bảo rằng bạn biết độ rộng bit của giá trị trả về của lệnh gọi hàm.

Example

Assign x = y & z & chk_yz(z, y); // chk_yz is a function

. . ./* Definition of the function */

Function chk_yz; // function definition

Input z,y;

chk_yz = y^z;

End functionMô-đun

Khai báo mô-đun

Trong Verilog, một mô-đun là thực thể thiết kế chính. Điều này cho biết tên và danh sách cổng (đối số). Một vài dòng tiếp theo chỉ định kiểu đầu vào / đầu ra (đầu vào, đầu ra hoặc inout) và chiều rộng của mỗi cổng. Chiều rộng cổng mặc định chỉ là 1 bit. Các biến cổng phải được khai báo bằng wire, Wand,. . ., đăng ký. Biến cổng mặc định là wire. Thông thường, đầu vào là dây vì dữ liệu của chúng được chốt bên ngoài mô-đun. Đầu ra thuộc loại reg nếu tín hiệu của chúng được lưu trữ bên trong.

Example

module sub_add(add, in1, in2, out);

input add; // defaults to wire

input [7:0] in1, in2; wire in1, in2;

output [7:0] out; reg out;

... statements ...

End modulePhân công liên tục

Phép gán liên tục trong Mô-đun được sử dụng để gán giá trị cho một dây, đây là phép gán bình thường được sử dụng ở bên ngoài khối luôn hoặc khối ban đầu. Việc gán này được thực hiện với một câu lệnh gán rõ ràng hoặc gán một giá trị cho một dây trong khi khai báo nó. Phép gán liên tục được thực hiện liên tục tại thời điểm mô phỏng. Thứ tự của các câu lệnh gán không ảnh hưởng đến nó. Nếu bạn thực hiện bất kỳ thay đổi nào đối với bất kỳ tín hiệu đầu vào bên phải nào thì tín hiệu đó sẽ thay đổi tín hiệu đầu ra bên trái.

Example

Wire [1:0] x = 2’y01; // assigned on declaration

Assign y = c | d; // using assign statement

Assign d = a & b;

/* the order of the assign statements does not matter. */Thuyết minh mô-đun

Khai báo mô-đun là các mẫu để tạo các đối tượng thực tế. Các mô-đun được khởi tạo bên trong các mô-đun khác và mỗi phần khởi tạo đang tạo một đối tượng duy nhất từ mẫu đó. Ngoại lệ là mô-đun cấp cao nhất là phần khởi tạo riêng của nó. Các cổng của mô-đun phải phù hợp với những cổng được xác định trong mẫu. Nó được chỉ định -

By name, sử dụng dấu chấm “tên cổng .template (tên dây kết nối với cổng)”. Hoặc là

By position, đặt các cổng ở cùng một vị trí trong danh sách cổng của cả mẫu và phiên bản.

Example

MODULE DEFINITION

Module and4 (x, y, z);

Input [3:0] x, y;

Output [3:0] z;

Assign z = x | y;

End moduleCác mô hình hành vi trong Verilog chứa các câu lệnh thủ tục, điều khiển mô phỏng và thao tác các biến của kiểu dữ liệu. Tất cả các câu lệnh này được chứa trong các thủ tục. Mỗi thủ tục có một luồng hoạt động được liên kết với nó.

Trong quá trình mô phỏng mô hình hành vi, tất cả các luồng được xác định bởi câu lệnh 'always' và 'initial' bắt đầu cùng nhau tại thời điểm mô phỏng 'zero'. Các câu lệnh ban đầu được thực thi một lần và các câu lệnh always được thực thi lặp đi lặp lại. Trong mô hình này, các biến thanh ghi a và b được khởi tạo thành nhị phân 1 và 0 tương ứng tại thời điểm mô phỏng 'không'. Câu lệnh ban đầu sau đó được hoàn thành và không được thực thi lại trong quá trình chạy mô phỏng đó. Câu lệnh ban đầu này chứa một khối đầu cuối (còn gọi là khối tuần tự) các câu lệnh. Trong khối loại begin-end này, a được khởi tạo đầu tiên, sau đó là b.

Ví dụ về Mô hình Hành vi

module behave;

reg [1:0]a,b;

initial

begin

a = ’b1;

b = ’b0;

end

always

begin

#50 a = ~a;

end

always

begin

#100 b = ~b;

end

End moduleNhiệm vụ thủ tục

Các phép gán thủ tục là để cập nhật các biến reg, số nguyên, thời gian và bộ nhớ. Có sự khác biệt đáng kể giữa chuyển nhượng theo thủ tục và chuyển nhượng liên tục như được mô tả dưới đây:

Các phép gán liên tục thúc đẩy các biến ròng và được đánh giá và cập nhật bất cứ khi nào toán hạng đầu vào thay đổi giá trị.

Các phép gán thủ tục cập nhật giá trị của các biến thanh ghi dưới sự điều khiển của các cấu trúc luồng thủ tục bao quanh chúng.

Phía bên phải của phép gán thủ tục có thể là bất kỳ biểu thức nào đánh giá một giá trị. Tuy nhiên, phần chọn ở phía bên phải phải có chỉ số không đổi. Phía bên trái chỉ ra biến nhận nhiệm vụ từ phía bên phải. Phía bên trái của việc phân công thủ tục có thể có một trong các dạng sau:

biến đăng ký, số nguyên, thực hoặc thời gian - Một phép gán cho tham chiếu tên của một trong các kiểu dữ liệu này.

chọn bit của một thanh ghi, số nguyên, thực hoặc biến thời gian - Một phép gán cho một bit duy nhất để các bit khác không bị ảnh hưởng.

lựa chọn một phần của biến thanh ghi, số nguyên, thực hoặc thời gian - Lựa chọn một phần của hai hoặc nhiều bit liền kề để giữ nguyên phần còn lại của các bit. Đối với hình thức chọn từng phần, chỉ các biểu thức hằng là hợp pháp.

phần tử bộ nhớ - Một từ duy nhất của bộ nhớ. Lưu ý rằng lựa chọn bit và chọn phần là bất hợp pháp trên các tham chiếu phần tử bộ nhớ.

nối của bất kỳ dạng nào ở trên - Có thể chỉ định một phép nối của bất kỳ dạng nào trong bốn dạng trước đó, điều này có hiệu quả phân vùng kết quả của biểu thức bên phải và gán các phần phân vùng, theo thứ tự, cho các phần khác nhau của phép nối.

Sự chậm trễ trong việc phân công (không phải để tổng hợp)

Trong một phép gán bị trễ, đơn vị thời gian Δt trôi qua trước khi câu lệnh được thực hiện và việc gán trái được thực hiện. Với độ trễ trong quá trình gán, vế phải được đánh giá ngay lập tức nhưng có độ trễ là Δt trước khi kết quả được đặt vào nhiệm vụ bên trái. Nếu một quy trình khác thay đổi tín hiệu bên phải trong thời gian Δt, thì nó không ảnh hưởng đến đầu ra. Sự chậm trễ không được hỗ trợ bởi các công cụ tổng hợp.

Cú pháp

Procedural Assignmentbiến = biểu thức

Delayed assignment# Biến Δt = biểu thức;

Intra-assignment delaybiểu thức biến = # Δt;

Thí dụ

reg [6:0] sum; reg h, ziltch;

sum[7] = b[7] ^ c[7]; // execute now.

ziltch = #15 ckz&h; /* ckz&a evaluated now; ziltch changed

after 15 time units. */

#10 hat = b&c; /* 10 units after ziltch changes, b&c is

evaluated and hat changes. */Chặn nhiệm vụ

Một câu lệnh gán thủ tục chặn phải được thực hiện trước khi thực hiện các câu lệnh theo sau nó trong một khối tuần tự. Câu lệnh gán thủ tục chặn không ngăn cản việc thực hiện các câu lệnh theo sau nó trong một khối song song.

Cú pháp

Cú pháp để gán thủ tục chặn như sau:

<lvalue> = <timing_control> <expression>Trong đó, lvalue là kiểu dữ liệu hợp lệ cho một câu lệnh gán thủ tục, = là toán tử gán và điều khiển thời gian là độ trễ gán trong tùy chọn. Độ trễ điều khiển thời gian có thể là điều khiển độ trễ (ví dụ: # 6) hoặc điều khiển sự kiện (ví dụ: @ (posedge clk)). Biểu thức là giá trị bên phải mà trình mô phỏng chỉ định cho bên trái. Toán tử gán = được sử dụng bằng cách chặn các phép gán thủ tục cũng được sử dụng bởi phép gán liên tục thủ tục và phép gán liên tục.

Thí dụ

rega = 0;

rega[3] = 1; // a bit-select

rega[3:5] = 7; // a part-select

mema[address] = 8’hff; // assignment to a memory element

{carry, acc} = rega + regb; // a concatenationNhiệm vụ không chặn (RTL)

Việc phân công thủ tục không chặn cho phép bạn lên lịch phân công mà không chặn luồng thủ tục. Bạn có thể sử dụng câu lệnh thủ tục không chặn bất cứ khi nào bạn muốn thực hiện một số chỉ định đăng ký trong cùng một bước thời gian mà không cần quan tâm đến thứ tự hoặc sự phụ thuộc vào nhau.

Cú pháp

Cú pháp để gán thủ tục không chặn như sau: