Multiprozessoren und Multicomputer

In diesem Kapitel werden Multiprozessoren und Multicomputer behandelt.

Multiprozessorsystemverbindungen

Die parallele Verarbeitung erfordert die Verwendung effizienter Systemverbindungen für eine schnelle Kommunikation zwischen den Ein- / Ausgabe- und Peripheriegeräten, Multiprozessoren und dem gemeinsam genutzten Speicher.

Hierarchische Bussysteme

Ein hierarchisches Bussystem besteht aus einer Hierarchie von Bussen, die verschiedene Systeme und Subsysteme / Komponenten in einem Computer verbinden. Jeder Bus besteht aus mehreren Signal-, Steuer- und Stromleitungen. Verschiedene Busse wie lokale Busse, Rückwandbusse und E / A-Busse werden verwendet, um verschiedene Verbindungsfunktionen auszuführen.

Lokale Busse sind die auf den Leiterplatten implementierten Busse. Ein Backplane-Bus ist eine gedruckte Schaltung, an der viele Anschlüsse zum Einstecken von Funktionsplatinen verwendet werden. Busse, die Eingabe- / Ausgabegeräte mit einem Computersystem verbinden, werden als E / A-Busse bezeichnet.

Crossbar-Schalter und Multiport-Speicher

Switched Networks ermöglichen dynamische Verbindungen zwischen den Ein- und Ausgängen. Kleine oder mittlere Systeme verwenden meist Crossbar-Netzwerke. Mehrstufige Netzwerke können auf größere Systeme erweitert werden, wenn das Problem der erhöhten Latenz gelöst werden kann.

Sowohl die Crossbar-Switch- als auch die Multiport-Speicherorganisation sind ein einstufiges Netzwerk. Der Aufbau eines einstufigen Netzwerks ist zwar billiger, es können jedoch mehrere Durchgänge erforderlich sein, um bestimmte Verbindungen herzustellen. Ein mehrstufiges Netzwerk besteht aus mehr als einer Stufe von Schaltkästen. Diese Netzwerke sollten in der Lage sein, jeden Eingang mit jedem Ausgang zu verbinden.

Mehrstufige und kombinierte Netzwerke

Mehrstufige Netzwerke oder mehrstufige Verbindungsnetzwerke sind eine Klasse von Hochgeschwindigkeits-Computernetzwerken, die hauptsächlich aus Verarbeitungselementen an einem Ende des Netzwerks und Speicherelementen am anderen Ende bestehen, die durch Schaltelemente verbunden sind.

Diese Netzwerke werden angewendet, um größere Multiprozessorsysteme aufzubauen. Dazu gehören Omega Network, Butterfly Network und viele mehr.

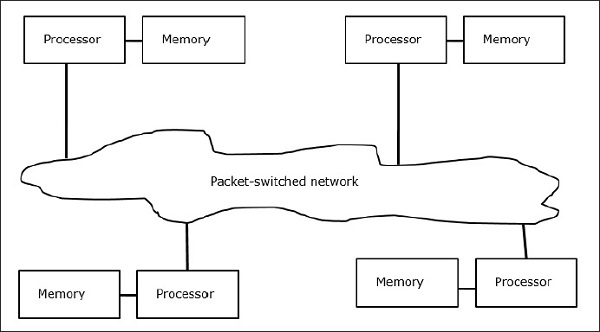

Multicomputer

Multicomputer sind verteilte Speicher-MIMD-Architekturen. Das folgende Diagramm zeigt ein konzeptionelles Modell eines Multicomputers -

Multicomputer sind Nachrichtenübermittlungsmaschinen, die eine Paketvermittlungsmethode anwenden, um Daten auszutauschen. Hier hat jeder Prozessor einen privaten Speicher, aber keinen globalen Adressraum, da ein Prozessor nur auf seinen eigenen lokalen Speicher zugreifen kann. Kommunikation ist also nicht transparent: Hier müssen Programmierer Kommunikationsprimitive explizit in ihren Code einfügen.

Kein global zugänglicher Speicher ist ein Nachteil von Multicomputern. Dies kann mithilfe der folgenden beiden Schemata gelöst werden:

- Virtueller gemeinsamer Speicher (VSM)

- Gemeinsamer virtueller Speicher (SVM)

In diesen Schemata nimmt der Anwendungsprogrammierer einen großen gemeinsam genutzten Speicher an, der global adressierbar ist. Bei Bedarf werden die von Anwendungen erstellten Speicherreferenzen in das Paradigma der Nachrichtenübermittlung übersetzt.

Virtueller gemeinsamer Speicher (VSM)

VSM ist eine Hardware-Implementierung. Das virtuelle Speichersystem des Betriebssystems wird also transparent auf VSM implementiert. Das Betriebssystem glaubt also, dass es auf einem Computer mit gemeinsam genutztem Speicher ausgeführt wird.

Gemeinsamer virtueller Speicher (SVM)

SVM ist eine Softwareimplementierung auf Betriebssystemebene mit Hardwareunterstützung durch die Memory Management Unit (MMU) des Prozessors. Hier ist die Einheit der Freigabe die Speicherseiten des Betriebssystems.

Wenn ein Prozessor einen bestimmten Speicherort adressiert, bestimmt die MMU, ob sich die dem Speicherzugriff zugeordnete Speicherseite im lokalen Speicher befindet oder nicht. Wenn sich die Seite nicht im Speicher befindet, wird sie in einem normalen Computersystem vom Betriebssystem von der Festplatte eingelagert. In SVM ruft das Betriebssystem die Seite jedoch vom Remote-Knoten ab, dem diese bestimmte Seite gehört.

Drei Generationen von Multicomputern

In diesem Abschnitt werden drei Generationen von Multicomputern behandelt.

Designentscheidungen in der Vergangenheit

Bei der Auswahl einer Prozessortechnologie wählt ein Multicomputer-Designer kostengünstige mittelkörnige Prozessoren als Bausteine. Die meisten parallelen Computer sind mit handelsüblichen Mikroprozessoren ausgestattet. Verteilter Speicher wurde für mehrere Computer gewählt, anstatt gemeinsam genutzten Speicher zu verwenden, was die Skalierbarkeit einschränken würde. Jeder Prozessor verfügt über eine eigene lokale Speichereinheit.

Für das Verbindungsschema haben Multicomputer eher direkte Punkt-zu-Punkt-Netzwerke für die Nachrichtenübermittlung als Adressvermittlungsnetzwerke. Für die Steuerungsstrategie wählt der Entwickler mehrerer Computer die asynchronen MIMD-, MPMD- und SMPD-Operationen aus. Der Cosmic Cube von Caltech (Seitz, 1983) ist der erste Multi-Computer der ersten Generation.

Gegenwärtige und zukünftige Entwicklung

Die Computer der nächsten Generation haben sich von mittelgroßen zu feinkörnigen Multicomputern entwickelt, die einen global gemeinsam genutzten virtuellen Speicher verwenden. Multi-Computer der zweiten Generation werden derzeit noch verwendet. Die Verwendung besserer Prozessoren wie i386, i860 usw., Computer der zweiten Generation, hat sich jedoch stark entwickelt.

Computer der dritten Generation sind Computer der nächsten Generation, auf denen von VLSI implementierte Knoten verwendet werden. Jeder Knoten kann einen 14-MIPS-Prozessor, 20-MByte / s-Routingkanäle und 16 KByte RAM auf einem einzelnen Chip haben.

Das Intel Paragon System

Zuvor wurden homogene Knoten verwendet, um Hypercube-Multicomputer herzustellen, da alle Funktionen dem Host zugewiesen wurden. Dies begrenzte also die E / A-Bandbreite. Um große Probleme effizient oder mit hohem Durchsatz zu lösen, konnten diese Computer nicht verwendet werden. Das Intel Paragon-System wurde entwickelt, um diese Schwierigkeit zu überwinden. Der Multicomputer wurde zu einem Anwendungsserver mit Mehrbenutzerzugriff in einer Netzwerkumgebung.

Nachrichtenübermittlungsmechanismen

Nachrichtenübermittlungsmechanismen in einem Multicomputer-Netzwerk erfordern spezielle Hardware- und Softwareunterstützung. In diesem Abschnitt werden wir einige Schemata diskutieren.

Nachrichtenrouting-Schemata

In Multicomputern mit Speicher- und Weiterleitungsroutingschema sind Pakete die kleinste Einheit der Informationsübertragung. In Wurmloch-gerouteten Netzwerken werden Pakete weiter in Flits unterteilt. Die Paketlänge wird durch das Routing-Schema und die Netzwerkimplementierung bestimmt, während die Flit-Länge von der Netzwerkgröße beeinflusst wird.

Im Store and forward routingPakete sind die Grundeinheit der Informationsübertragung. In diesem Fall verwendet jeder Knoten einen Paketpuffer. Ein Paket wird von einem Quellknoten zu einem Zielknoten über eine Folge von Zwischenknoten übertragen. Die Latenz ist direkt proportional zur Entfernung zwischen Quelle und Ziel.

Im wormhole routingDie Übertragung vom Quellknoten zum Zielknoten erfolgt über eine Folge von Routern. Alle Flits desselben Pakets werden in einer untrennbaren Reihenfolge in einer Pipeline-Weise übertragen. In diesem Fall weiß nur der Header-Flit, wohin das Paket geht.

Deadlock und virtuelle Kanäle

Ein virtueller Kanal ist eine logische Verbindung zwischen zwei Knoten. Es wird durch einen Flit-Puffer im Quell- und Empfängerknoten und einen physikalischen Kanal zwischen ihnen gebildet. Wenn einem Paar ein physischer Kanal zugewiesen wird, wird ein Quellpuffer mit einem Empfängerpuffer gepaart, um einen virtuellen Kanal zu bilden.

Wenn alle Kanäle von Nachrichten belegt sind und keiner der Kanäle im Zyklus freigegeben wird, tritt eine Deadlock-Situation auf. Um dies zu vermeiden, muss ein Deadlock-Vermeidungsschema befolgt werden.