ไมโครโปรเซสเซอร์ - การกำหนดค่าพิน 8086

8086 เป็นไมโครโปรเซสเซอร์ 16 บิตตัวแรกที่มีอยู่ในชิป DIP (Dual Inline Package) 40 พิน ตอนนี้ให้เราพูดถึงรายละเอียดการกำหนดค่าพินของไมโครโปรเซสเซอร์ 8086

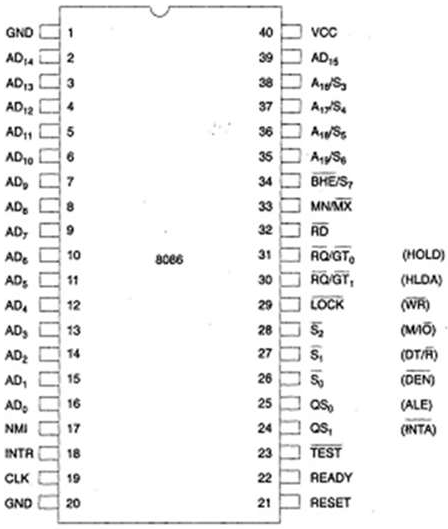

8086 พินไดอะแกรม

นี่คือพินไดอะแกรมของไมโครโปรเซสเซอร์ 8086 -

ให้เราหารือเกี่ยวกับสัญญาณโดยละเอียด -

Power supply and frequency signals

ใช้แหล่งจ่ายไฟ 5V DC ที่ขาV CC 40 และใช้กราวด์ที่ V SSพิน 1 และ 20 สำหรับการทำงาน

Clock signal

สัญญาณนาฬิกามีให้ผ่าน Pin-19 ให้เวลากับโปรเซสเซอร์สำหรับการดำเนินการ ความถี่จะแตกต่างกันไปตามเวอร์ชันต่างๆเช่น 5MHz, 8MHz และ 10MHz

Address/data bus

AD0-AD15. เหล่านี้คือ 16 แอดเดรส / บัสข้อมูล AD0-AD7 มีข้อมูลไบต์ลำดับต่ำและ AD8AD15 มีข้อมูลไบต์ลำดับที่สูงกว่า ในรอบนาฬิกาแรกจะมีที่อยู่ 16 บิตและหลังจากนั้นจะมีข้อมูล 16 บิต

Address/status bus

A16-A19 / S3-S6 นี่คือรถบัสที่อยู่ / สถานะ 4 รายการ ในรอบนาฬิกาแรกจะมีแอดเดรส 4 บิตและต่อมาจะมีสัญญาณสถานะ

S7/BHE

BHE ย่อมาจาก Bus High Enable มีอยู่ที่พิน 34 และใช้เพื่อระบุการถ่ายโอนข้อมูลโดยใช้บัสข้อมูล D8-D15 สัญญาณนี้จะต่ำในระหว่างรอบนาฬิกาแรกหลังจากนั้นจึงทำงาน

Read($\overline{RD}$)

มีอยู่ที่พิน 32 และใช้ในการอ่านสัญญาณสำหรับการอ่าน

Ready

มีอยู่ที่พิน 22 เป็นสัญญาณตอบรับจากอุปกรณ์ I / O ที่ถ่ายโอนข้อมูล มันเป็นสัญญาณสูงที่ใช้งานอยู่ เมื่ออยู่ในระดับสูงแสดงว่าอุปกรณ์พร้อมที่จะถ่ายโอนข้อมูล เมื่ออยู่ในระดับต่ำจะแสดงสถานะการรอ

RESET

มีอยู่ที่พิน 21 และใช้เพื่อเริ่มการทำงานใหม่ ทำให้โปรเซสเซอร์ยุติกิจกรรมปัจจุบันทันที สัญญาณนี้จะทำงานสูงเป็นเวลา 4 รอบนาฬิกาแรกเพื่อรีเซ็ตไมโครโปรเซสเซอร์

INTR

มีอยู่ที่พิน 18 เป็นสัญญาณคำร้องขอขัดจังหวะซึ่งจะสุ่มตัวอย่างระหว่างรอบสัญญาณนาฬิกาสุดท้ายของแต่ละคำสั่งเพื่อพิจารณาว่าโปรเซสเซอร์พิจารณาว่านี่เป็นการขัดจังหวะหรือไม่

NMI

ย่อมาจากอินเทอร์รัปต์แบบไม่ปิดบังและมีอยู่ที่พิน 17 เป็นอินพุตที่ถูกทริกเกอร์ขอบซึ่งทำให้เกิดการร้องขอการขัดจังหวะไปยังไมโครโปรเซสเซอร์

$ \ overline {TEST} $

สัญญาณนี้เหมือนกับสถานะการรอและพร้อมใช้งานที่พิน 23 เมื่อสัญญาณนี้สูงโปรเซสเซอร์จะต้องรอสถานะ IDLE มิฉะนั้นการดำเนินการจะดำเนินต่อไป

MN/$\overline{MX}$

ย่อมาจาก Minimum / Maximum และมีอยู่ที่พิน 33 ซึ่งระบุว่าโปรเซสเซอร์จะทำงานในโหมดใด เมื่ออยู่ในระดับสูงจะทำงานในโหมดต่ำสุดและในทางกลับกัน

INTA

เป็นสัญญาณตอบรับการขัดจังหวะและ id ที่มีอยู่ที่พิน 24 เมื่อไมโครโปรเซสเซอร์ได้รับสัญญาณนี้จะรับทราบการขัดจังหวะ

ALE

มันย่อมาจาก address enable latch และมีอยู่ที่พิน 25 พัลส์บวกจะถูกสร้างขึ้นทุกครั้งที่โปรเซสเซอร์เริ่มการทำงานใด ๆ สัญญาณนี้บ่งบอกถึงความพร้อมใช้งานของที่อยู่ที่ถูกต้องบนที่อยู่ / สายข้อมูล

DEN

ย่อมาจาก Data Enable และมีอยู่ที่ขา 26 ใช้เพื่อเปิดใช้งาน Transreceiver 8286 ตัวรับส่งสัญญาณเป็นอุปกรณ์ที่ใช้แยกข้อมูลจากแอดเดรส / บัสข้อมูล

DT/R

ย่อมาจาก Data Transmit / รับสัญญาณและมีอยู่ที่พิน 27 ซึ่งจะกำหนดทิศทางการไหลของข้อมูลผ่านตัวรับส่งสัญญาณ เมื่ออยู่ในระดับสูงข้อมูลจะถูกส่งออกไปในทางกลับกัน

M/IO

สัญญาณนี้ใช้เพื่อแยกความแตกต่างระหว่างการทำงานของหน่วยความจำและ I / O เมื่อค่าสูงแสดงว่ามีการทำงานของ I / O และเมื่อค่าต่ำแสดงถึงการทำงานของหน่วยความจำ มีจำหน่ายที่พิน 28

WR

ย่อมาจาก write signal และมีอยู่ที่ขา 29 ใช้ในการเขียนข้อมูลลงในหน่วยความจำหรืออุปกรณ์ส่งออกขึ้นอยู่กับสถานะของสัญญาณ M / IO

HLDA

ย่อมาจากสัญญาณ Hold Acknowledgment และมีอยู่ที่ขา 30 สัญญาณนี้รับทราบสัญญาณ HOLD

HOLD

สัญญาณนี้บ่งชี้ให้โปรเซสเซอร์ทราบว่าอุปกรณ์ภายนอกกำลังร้องขอเพื่อเข้าถึงแอดเดรส / บัสข้อมูล มีจำหน่ายที่พิน 31

QS1 and QS0

นี่คือสัญญาณสถานะคิวและมีอยู่ที่พิน 24 และ 25 สัญญาณเหล่านี้ระบุสถานะของคิวคำสั่ง เงื่อนไขของพวกเขาแสดงไว้ในตารางต่อไปนี้ -

| คำพูดคำจา0 | คำพูดคำจา1 | สถานะ |

|---|---|---|

| 0 | 0 | ไม่มีการดำเนินการ |

| 0 | 1 | ไบต์แรกของ opcode จากคิว |

| 1 | 0 | ล้างคิว |

| 1 | 1 | ไบต์ที่ตามมาจากคิว |

S0, S1, S2

นี่คือสัญญาณสถานะที่ระบุสถานะการทำงานซึ่ง Bus Controller 8288 ใช้เพื่อสร้างหน่วยความจำและสัญญาณควบคุม I / O มีอยู่ที่พิน 26, 27 และ 28 ต่อไปนี้เป็นตารางแสดงสถานะ -

| ส2 | ส1 | S 0 | สถานะ |

|---|---|---|---|

| 0 | 0 | 0 | รบกวนรับทราบ |

| 0 | 0 | 1 | อ่าน I / O |

| 0 | 1 | 0 | I / O เขียน |

| 0 | 1 | 1 | หยุด |

| 1 | 0 | 0 | การดึงข้อมูล Opcode |

| 1 | 0 | 1 | อ่านหน่วยความจำ |

| 1 | 1 | 0 | เขียนหน่วยความจำ |

| 1 | 1 | 1 | เรื่อย ๆ |

LOCK

เมื่อสัญญาณนี้ทำงานอยู่สัญญาณนี้จะบอกให้โปรเซสเซอร์อื่นไม่ขอให้ CPU ออกจากบัสระบบ เปิดใช้งานโดยใช้คำนำหน้า LOCK ในคำสั่งใด ๆ และมีอยู่ที่พิน 29

RQ/GT1 and RQ/GT0

นี่คือสัญญาณคำขอ / ให้สิทธิ์ที่โปรเซสเซอร์อื่นใช้เพื่อขอให้ CPU ปล่อยบัสระบบ เมื่อ CPU ได้รับสัญญาณก็จะส่งการตอบรับ RQ / GT 0มีลำดับความสำคัญสูงกว่า RQ / GT 1