ไมโครโปรเซสเซอร์ - คู่มือฉบับย่อ

ไมโครโปรเซสเซอร์เป็นหน่วยควบคุมของไมโครคอมพิวเตอร์ที่ประดิษฐ์ขึ้นบนชิปขนาดเล็กที่สามารถดำเนินการ ALU (Arithmetic Logical Unit) และสื่อสารกับอุปกรณ์อื่น ๆ ที่เชื่อมต่ออยู่

ไมโครโปรเซสเซอร์ประกอบด้วย ALU อาร์เรย์รีจิสเตอร์และชุดควบคุม ALU ดำเนินการทางคณิตศาสตร์และตรรกะกับข้อมูลที่ได้รับจากหน่วยความจำหรืออุปกรณ์อินพุต อาร์เรย์การลงทะเบียนประกอบด้วยการลงทะเบียนที่ระบุด้วยตัวอักษรเช่น B, C, D, E, H, L และตัวสะสม ชุดควบคุมควบคุมการไหลของข้อมูลและคำสั่งภายในคอมพิวเตอร์

แผนภาพบล็อกของไมโครคอมพิวเตอร์พื้นฐาน

ไมโครโปรเซสเซอร์ทำงานอย่างไร?

ไมโครโปรเซสเซอร์จะทำตามลำดับ: ดึงข้อมูลถอดรหัสแล้วดำเนินการ

ในขั้นต้นคำแนะนำจะถูกเก็บไว้ในหน่วยความจำตามลำดับ ไมโครโปรเซสเซอร์จะดึงคำสั่งเหล่านั้นจากหน่วยความจำจากนั้นถอดรหัสและดำเนินการคำสั่งเหล่านั้นจนกว่าจะถึงคำสั่ง STOP ต่อมาจะส่งผลลัพธ์ในรูปแบบไบนารีไปยังพอร์ตเอาต์พุต ระหว่างกระบวนการเหล่านี้รีจิสเตอร์จะจัดเก็บข้อมูลชั่วคราวและ ALU จะทำหน้าที่คำนวณ

รายการข้อกำหนดที่ใช้ในไมโครโปรเซสเซอร์

นี่คือรายการคำศัพท์ที่ใช้บ่อยในไมโครโปรเซสเซอร์ -

Instruction Set - เป็นชุดคำสั่งที่ไมโครโปรเซสเซอร์สามารถเข้าใจได้

Bandwidth - เป็นจำนวนบิตที่ประมวลผลในคำสั่งเดียว

Clock Speed- กำหนดจำนวนการดำเนินการต่อวินาทีที่โปรเซสเซอร์สามารถทำได้ แสดงเป็นเมกะเฮิรตซ์ (MHz) หรือกิกะเฮิรตซ์ (GHz) เรียกอีกอย่างว่าอัตรานาฬิกา

Word Length- ขึ้นอยู่กับความกว้างของบัสข้อมูลภายในรีจิสเตอร์ ALU ฯลฯ ไมโครโปรเซสเซอร์ 8 บิตสามารถประมวลผลข้อมูล 8 บิตได้ในแต่ละครั้ง ความยาวของคำมีตั้งแต่ 4 บิตถึง 64 บิตขึ้นอยู่กับประเภทของไมโครคอมพิวเตอร์

Data Types - ไมโครโปรเซสเซอร์มีรูปแบบข้อมูลหลายรูปแบบเช่นไบนารี BCD ASCII หมายเลขที่ลงชื่อและไม่ได้ลงชื่อ

คุณสมบัติของไมโครโปรเซสเซอร์

นี่คือรายการคุณสมบัติที่โดดเด่นที่สุดของไมโครโปรเซสเซอร์ใด ๆ -

Cost-effective - ชิปไมโครโปรเซสเซอร์มีจำหน่ายในราคาถูกและส่งผลให้ต้นทุนต่ำ

Size - ไมโครโปรเซสเซอร์เป็นชิปขนาดเล็กจึงพกพาได้

Low Power Consumption - ไมโครโปรเซสเซอร์ผลิตโดยใช้เทคโนโลยีโลหะออกไซด์เซมิคอนดักเตอร์ซึ่งใช้พลังงานต่ำ

Versatility - ไมโครโปรเซสเซอร์มีความหลากหลายเนื่องจากเราสามารถใช้ชิปตัวเดียวกันในแอพพลิเคชั่นต่างๆได้โดยการกำหนดค่าโปรแกรมซอฟต์แวร์

Reliability - อัตราความล้มเหลวของ IC ในไมโครโปรเซสเซอร์ต่ำมากจึงเชื่อถือได้

ไมโครโปรเซสเซอร์สามารถแบ่งออกเป็นสามประเภท -

โปรเซสเซอร์ RISC

RISC ย่อมาจาก Reduced Instruction Set Computer. ออกแบบมาเพื่อลดเวลาในการดำเนินการโดยทำให้ชุดคำสั่งของคอมพิวเตอร์ง่ายขึ้น การใช้ตัวประมวลผล RISC แต่ละคำสั่งต้องใช้รอบสัญญาณนาฬิกาเพียงรอบเดียวเพื่อให้ได้ผลลัพธ์ในเวลาดำเนินการที่สม่ำเสมอ สิ่งนี้จะลดประสิทธิภาพเนื่องจากมีโค้ดจำนวนมากขึ้นจึงจำเป็นต้องใช้ RAM มากขึ้นในการจัดเก็บคำแนะนำ คอมไพเลอร์ยังต้องทำงานมากขึ้นเพื่อแปลงคำสั่งภาษาระดับสูงเป็นรหัสเครื่อง

โปรเซสเซอร์ RISC บางตัว ได้แก่ -

- เพาเวอร์พีซี: 601, 604, 615, 620

- DEC Alpha: 210642, 211066, 21068, 21164

- MIPS: TS (R10000) โปรเซสเซอร์ RISC

- PA-RISC: HP 7100LC

สถาปัตยกรรมของ RISC

สถาปัตยกรรมไมโครโปรเซสเซอร์ RISC ใช้ชุดคำสั่งที่ปรับให้เหมาะสมที่สุด ใช้ในอุปกรณ์พกพาเช่น Apple iPod เนื่องจากประสิทธิภาพการใช้พลังงาน

ลักษณะของ RISC

ลักษณะสำคัญของโปรเซสเซอร์ RISC มีดังต่อไปนี้ -

ประกอบด้วยคำแนะนำง่ายๆ

รองรับรูปแบบข้อมูลประเภทต่างๆ

ใช้โหมดการกำหนดแอดเดรสอย่างง่ายและคำแนะนำความยาวคงที่สำหรับการวางท่อ

รองรับการลงทะเบียนเพื่อใช้ในบริบทใด ๆ

เวลาดำเนินการหนึ่งรอบ

คำแนะนำ“ LOAD” และ“ STORE” ใช้เพื่อเข้าถึงตำแหน่งหน่วยความจำ

ประกอบด้วยการลงทะเบียนจำนวนมากขึ้น

ประกอบด้วยทรานซิสเตอร์จำนวนน้อย

โปรเซสเซอร์ CISC

CISC ย่อมาจาก Complex Instruction Set Computer. ได้รับการออกแบบมาเพื่อลดจำนวนคำสั่งต่อโปรแกรมโดยไม่สนใจจำนวนรอบต่อคำสั่ง เน้นที่การสร้างคำสั่งที่ซับซ้อนลงในฮาร์ดแวร์โดยตรง

คอมไพเลอร์ต้องทำงานน้อยมากในการแปลภาษาระดับสูงเป็นภาษาระดับแอสเซมบลี / รหัสเครื่องเนื่องจากความยาวของโค้ดค่อนข้างสั้นจึงต้องใช้ RAM น้อยมากในการจัดเก็บคำสั่ง

โปรเซสเซอร์ CISC บางตัว ได้แก่ -

- ไอบีเอ็ม 370/168

- VAX 11/780

- Intel 80486

สถาปัตยกรรมของ CISC

สถาปัตยกรรมได้รับการออกแบบมาเพื่อลดต้นทุนหน่วยความจำเนื่องจากจำเป็นต้องใช้พื้นที่จัดเก็บข้อมูลมากขึ้นในโปรแกรมขนาดใหญ่ทำให้ต้นทุนหน่วยความจำสูงขึ้น ในการแก้ไขปัญหานี้จำนวนคำสั่งต่อโปรแกรมสามารถลดลงได้โดยการฝังจำนวนการดำเนินการไว้ในคำสั่งเดียว

ลักษณะของ CISC

- โหมดการกำหนดแอดเดรสที่หลากหลาย

- คำแนะนำจำนวนมากขึ้น

- รูปแบบคำสั่งที่มีความยาวผันแปรได้

- อาจต้องใช้หลายรอบเพื่อดำเนินการหนึ่งคำสั่ง

- ตรรกะการถอดรหัสคำสั่งมีความซับซ้อน

- ต้องใช้คำสั่งเดียวเพื่อรองรับโหมดการกำหนดแอดเดรสหลายโหมด

โปรเซสเซอร์พิเศษ

นี่คือโปรเซสเซอร์ที่ออกแบบมาเพื่อวัตถุประสงค์พิเศษบางประการ มีการพูดคุยสั้น ๆ เกี่ยวกับโปรเซสเซอร์พิเศษบางส่วน -

ตัวประมวลผลร่วม

โปรเซสเซอร์ร่วมคือไมโครโปรเซสเซอร์ที่ออกแบบมาเป็นพิเศษซึ่งสามารถจัดการกับฟังก์ชันเฉพาะของมันได้เร็วกว่าไมโครโปรเซสเซอร์ทั่วไปหลายเท่า

For example - ตัวประมวลผลร่วมคณิตศาสตร์

โปรเซสเซอร์ร่วมคณิตศาสตร์ของ Intel บางตัว ได้แก่ -

- 8087 ใช้กับ 8086

- 80287 - ใช้กับ 80286

- 80387 - ใช้กับ 80386

อินพุต / เอาท์พุตโปรเซสเซอร์

เป็นไมโครโปรเซสเซอร์ที่ออกแบบมาเป็นพิเศษโดยมีหน่วยความจำภายในเป็นของตัวเองซึ่งใช้เพื่อควบคุมอุปกรณ์ I / O ที่มีการเกี่ยวข้องกับ CPU น้อยที่สุด

For example -

- คอนโทรลเลอร์ DMA (เข้าถึงหน่วยความจำโดยตรง)

- ตัวควบคุมแป้นพิมพ์ / เมาส์

- ตัวควบคุมการแสดงผลกราฟิก

- ตัวควบคุมพอร์ต SCSI

Transputer (คอมพิวเตอร์ทรานซิสเตอร์)

Transputer เป็นไมโครโปรเซสเซอร์ที่ออกแบบมาเป็นพิเศษโดยมีหน่วยความจำภายในของตัวเองและมีลิงค์สำหรับเชื่อมต่อเครื่องส่งหนึ่งเครื่องกับเครื่องขนส่งอื่นสำหรับการสื่อสารระหว่างโปรเซสเซอร์ ได้รับการออกแบบครั้งแรกในปี 1980 โดย Inmos และมีเป้าหมายเพื่อการใช้ประโยชน์จากเทคโนโลยี VLSI

Transputer สามารถใช้เป็นระบบโปรเซสเซอร์เดียวหรือสามารถเชื่อมต่อกับลิงค์ภายนอกซึ่งจะช่วยลดต้นทุนการก่อสร้างและเพิ่มประสิทธิภาพ

For example - โปรเซสเซอร์ T212 16 บิต 32 บิต T425 จุดลอยตัว (T800, T805 & T9000)

DSP (ตัวประมวลผลสัญญาณดิจิตอล)

โปรเซสเซอร์นี้ได้รับการออกแบบมาเป็นพิเศษเพื่อประมวลผลสัญญาณอนาล็อกให้อยู่ในรูปแบบดิจิทัล ทำได้โดยการสุ่มตัวอย่างระดับแรงดันไฟฟ้าในช่วงเวลาปกติและแปลงแรงดันไฟฟ้าในทันทีนั้นให้อยู่ในรูปแบบดิจิทัล กระบวนการนี้ดำเนินการโดยวงจรที่เรียกว่าตัวแปลงอนาล็อกเป็นดิจิตอลตัวแปลง A ถึง D หรือ ADC

DSP ประกอบด้วยส่วนประกอบต่อไปนี้ -

Program Memory - จัดเก็บโปรแกรมที่ DSP จะใช้ในการประมวลผลข้อมูล

Data Memory - จัดเก็บข้อมูลที่จะดำเนินการ

Compute Engine - ดำเนินการประมวลผลทางคณิตศาสตร์การเข้าถึงโปรแกรมจากหน่วยความจำโปรแกรมและข้อมูลจากหน่วยความจำข้อมูล

Input/Output - เชื่อมต่อกับโลกภายนอก

การใช้งานคือ -

- การสังเคราะห์เสียงและดนตรี

- การบีบอัดเสียงและวิดีโอ

- การประมวลผลสัญญาณวิดีโอ

- การเร่งกราฟิก 2D และ 3D

For example - ซีรี่ส์ TMS 320 ของ Texas Instrument เช่น TMS 320C40, TMS320C50

8085 ออกเสียงว่าไมโครโปรเซสเซอร์ "แปดสิบแปดสิบห้า" เป็นไมโครโปรเซสเซอร์ 8 บิตที่ออกแบบโดย Intel ในปี 1977 โดยใช้เทคโนโลยี NMOS

มีการกำหนดค่าดังต่อไปนี้ -

- บัสข้อมูล 8 บิต

- บัสแอดเดรส 16 บิตซึ่งสามารถรองรับได้ไม่เกิน 64KB

- ตัวนับโปรแกรม 16 บิต

- ตัวชี้สแต็ก 16 บิต

- รีจิสเตอร์ 8 บิตหกตัวจัดเรียงเป็นคู่: BC, DE, HL

- ต้องใช้แหล่งจ่ายไฟ + 5V เพื่อทำงานที่นาฬิกาเฟสเดียว 3.2 MHZ

ใช้ในเครื่องซักผ้าเตาอบไมโครเวฟโทรศัพท์มือถือ ฯลฯ

ไมโครโปรเซสเซอร์ 8085 - หน่วยการทำงาน

8085 ประกอบด้วยหน่วยการทำงานดังต่อไปนี้ -

ตัวสะสม

เป็นการลงทะเบียน 8 บิตที่ใช้ในการดำเนินการทางคณิตศาสตร์ตรรกะ I / O & LOAD / STORE เชื่อมต่อกับบัสข้อมูลภายใน & ALU

หน่วยเลขคณิตและตรรกะ

ตามชื่อที่แนะนำมันดำเนินการทางคณิตศาสตร์และตรรกะเช่นการบวกการลบและหรืออื่น ๆ บนข้อมูล 8 บิต

ลงทะเบียนวัตถุประสงค์ทั่วไป

มีรีจิสเตอร์เอนกประสงค์ 6 ตัวในโปรเซสเซอร์ 8085 ได้แก่ B, C, D, E, H & L รีจิสเตอร์แต่ละตัวสามารถเก็บข้อมูล 8 บิตได้

การลงทะเบียนเหล่านี้สามารถทำงานเป็นคู่เพื่อเก็บข้อมูล 16 บิตและชุดค่าผสมการจับคู่จะเหมือนกับ BC, DE & HL

ตัวนับโปรแกรม

เป็นรีจิสเตอร์ 16 บิตที่ใช้ในการจัดเก็บตำแหน่งแอดเดรสหน่วยความจำของคำสั่งถัดไปที่จะดำเนินการ ไมโครโปรเซสเซอร์จะเพิ่มโปรแกรมเมื่อใดก็ตามที่มีการเรียกใช้คำสั่งเพื่อให้ตัวนับของโปรแกรมชี้ไปยังที่อยู่หน่วยความจำของคำสั่งถัดไปที่กำลังจะถูกเรียกใช้งาน

ตัวชี้สแต็ก

นอกจากนี้ยังเป็นรีจิสเตอร์ 16 บิตที่ทำงานเหมือนสแต็กซึ่งจะเพิ่ม / ลดด้วย 2 เสมอระหว่างการดำเนินการพุช & ป๊อป

ลงทะเบียนชั่วคราว

เป็นรีจิสเตอร์ 8 บิตซึ่งเก็บข้อมูลชั่วคราวของการดำเนินการทางคณิตศาสตร์และตรรกะ

ตั้งค่าสถานะลงทะเบียน

เป็นรีจิสเตอร์ 8 บิตที่มีฟลิปฟล็อป 1 บิต 5 ตัวซึ่งเก็บ 0 หรือ 1 ขึ้นอยู่กับผลลัพธ์ที่เก็บไว้ในแอคคูมูเลเตอร์

นี่คือชุดรองเท้าแตะ 5 แบบ -

- ลงชื่อ (S)

- ศูนย์ (Z)

- อุปกรณ์เสริม (AC)

- ความเท่าเทียมกัน (P)

- พกพา (C)

ตำแหน่งบิตแสดงในตารางต่อไปนี้ -

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| ส | Z | AC | ป | CY |

การลงทะเบียนคำสั่งและตัวถอดรหัส

เป็นการลงทะเบียน 8 บิต เมื่อคำสั่งถูกดึงมาจากหน่วยความจำคำสั่งนั้นจะถูกเก็บไว้ใน Instruction register ตัวถอดรหัสคำสั่งจะถอดรหัสข้อมูลที่มีอยู่ในทะเบียนคำสั่ง

ชุดจับเวลาและชุดควบคุม

ให้สัญญาณเวลาและสัญญาณควบคุมไปยังไมโครโปรเซสเซอร์เพื่อดำเนินการ ต่อไปนี้เป็นสัญญาณเวลาและสัญญาณควบคุมซึ่งควบคุมวงจรภายนอกและภายใน -

- สัญญาณควบคุม: READY, RD ', WR', ALE

- สัญญาณสถานะ: S0, S1, IO / M '

- สัญญาณ DMA: ถือ, HLDA

- รีเซ็ตสัญญาณ: รีเซ็ตใน, รีเซ็ตออก

การควบคุมขัดจังหวะ

ตามชื่อที่แนะนำจะควบคุมการขัดจังหวะระหว่างกระบวนการ เมื่อไมโครโปรเซสเซอร์กำลังเรียกใช้โปรแกรมหลักและเมื่อใดก็ตามที่เกิดการขัดจังหวะไมโครโปรเซสเซอร์จะเปลี่ยนการควบคุมจากโปรแกรมหลักเพื่อประมวลผลคำขอที่เข้ามา หลังจากการร้องขอเสร็จสิ้นการควบคุมจะกลับไปที่โปรแกรมหลัก

มีสัญญาณขัดจังหวะ 5 สัญญาณในไมโครโปรเซสเซอร์ 8085: INTR, RST 7.5, RST 6.5, RST 5.5, TRAP

การควบคุมอินพุต / เอาต์พุตแบบอนุกรม

ควบคุมการสื่อสารข้อมูลแบบอนุกรมโดยใช้คำแนะนำสองคำนี้: SID (Serial input data) และ SOD (Serial output data)

บัฟเฟอร์แอดเดรสและบัฟเฟอร์ข้อมูลแอดเดรส

เนื้อหาที่จัดเก็บในตัวชี้สแต็กและตัวนับโปรแกรมจะถูกโหลดลงในบัฟเฟอร์แอดเดรสและบัฟเฟอร์ข้อมูลแอดเดรสเพื่อสื่อสารกับ CPU หน่วยความจำและชิป I / O เชื่อมต่อกับบัสเหล่านี้ CPU สามารถแลกเปลี่ยนข้อมูลที่ต้องการกับหน่วยความจำและชิป I / O

แอดเดรสบัสและบัสข้อมูล

บัสข้อมูลทำหน้าที่จัดเก็บข้อมูล เป็นแบบสองทิศทางในขณะที่แอดเดรสบัสจะนำตำแหน่งไปยังที่ที่ควรจัดเก็บและเป็นแบบทิศทางเดียว ใช้ในการถ่ายโอนข้อมูลและอุปกรณ์ I / O ที่อยู่

8085 สถาปัตยกรรม

เราได้พยายามพรรณนาสถาปัตยกรรมของ 8085 ด้วยภาพต่อไปนี้ -

ภาพต่อไปนี้แสดงแผนภาพพินของไมโครโปรเซสเซอร์ 8085 -

หมุดของไมโครโปรเซสเซอร์ 8085 สามารถแบ่งออกเป็นเจ็ดกลุ่ม -

ที่อยู่บัส

A15-A8 มีหน่วยความจำ 8 บิต / ที่อยู่ IO ที่สำคัญที่สุด

บัสข้อมูล

AD7-AD0 มีแอดเดรสและบัสข้อมูล 8 บิตที่มีนัยสำคัญน้อยที่สุด

สัญญาณควบคุมและสถานะ

สัญญาณเหล่านี้ใช้เพื่อระบุลักษณะการทำงาน มี 3 สัญญาณควบคุมและ 3 สัญญาณสถานะ

สัญญาณควบคุมสามสัญญาณคือ RD, WR & ALE

RD - สัญญาณนี้บ่งชี้ว่าจะอ่าน IO หรืออุปกรณ์หน่วยความจำที่เลือกและพร้อมสำหรับการรับข้อมูลที่มีอยู่บนบัสข้อมูล

WR - สัญญาณนี้บ่งชี้ว่าข้อมูลบนบัสข้อมูลจะถูกเขียนลงในหน่วยความจำที่เลือกหรือตำแหน่ง IO

ALE- เป็นพัลส์ที่เป็นบวกที่สร้างขึ้นเมื่อการทำงานใหม่เริ่มต้นโดยไมโครโปรเซสเซอร์ เมื่อชีพจรสูงขึ้นแสดงว่าอยู่ เมื่อชีพจรลงจะแสดงข้อมูล

สัญญาณสถานะสามแบบคือ IO / M, S0 & S1

IO / M

สัญญาณนี้ใช้เพื่อแยกความแตกต่างระหว่างการทำงานของ IO และหน่วยความจำกล่าวคือเมื่อมีค่าสูงแสดงว่ามีการทำงานของ IO และเมื่อสัญญาณต่ำแสดงว่าการทำงานของหน่วยความจำ

S1 และ S0

สัญญาณเหล่านี้ใช้เพื่อระบุประเภทของการทำงานปัจจุบัน

แหล่งจ่ายไฟ

มี 2 สัญญาณแหล่งจ่ายไฟ - VCC และ VSS VCC ระบุแหล่งจ่ายไฟ + 5v และ VSS แสดงสัญญาณกราวด์

สัญญาณนาฬิกา

มีสัญญาณนาฬิกา 3 แบบคือ X1, X2, CLK OUT

X1, X2- คริสตัล (RC, LC N / W) เชื่อมต่อที่หมุดทั้งสองนี้และใช้เพื่อตั้งค่าความถี่ของเครื่องกำเนิดสัญญาณนาฬิกาภายใน ความถี่นี้หารภายในด้วย 2

CLK OUT - สัญญาณนี้ใช้เป็นนาฬิการะบบสำหรับอุปกรณ์ที่เชื่อมต่อกับไมโครโปรเซสเซอร์

สัญญาณขัดจังหวะและเริ่มต้นจากภายนอก

อินเทอร์รัปต์คือสัญญาณที่สร้างขึ้นโดยอุปกรณ์ภายนอกเพื่อขอให้ไมโครโปรเซสเซอร์ทำงาน มีสัญญาณขัดจังหวะ 5 สัญญาณ ได้แก่ TRAP, RST 7.5, RST 6.5, RST 5.5 และ INTR เราจะพูดถึงการขัดจังหวะโดยละเอียดในส่วนการขัดจังหวะ

INTA - เป็นสัญญาณตอบรับการขัดจังหวะ

RESET IN - สัญญาณนี้ใช้เพื่อรีเซ็ตไมโครโปรเซสเซอร์โดยตั้งค่าตัวนับโปรแกรมเป็นศูนย์

RESET OUT - สัญญาณนี้ใช้เพื่อรีเซ็ตอุปกรณ์ที่เชื่อมต่อทั้งหมดเมื่อไมโครโปรเซสเซอร์ถูกรีเซ็ต

READY- สัญญาณนี้บ่งชี้ว่าอุปกรณ์พร้อมที่จะส่งหรือรับข้อมูล หาก READY ต่ำแสดงว่า CPU ต้องรอให้ READY สูงขึ้น

HOLD - สัญญาณนี้บ่งชี้ว่านายคนอื่นกำลังขอใช้ที่อยู่และบัสข้อมูล

HLDA (HOLD Acknowledge)- แสดงว่า CPU ได้รับคำขอ HOLD และจะยกเลิกบัสในรอบนาฬิกาถัดไป HLDA ถูกตั้งค่าเป็นต่ำหลังจากที่สัญญาณ HOLD ถูกลบออก

สัญญาณ I / O แบบอนุกรม

มีสัญญาณอนุกรม 2 สัญญาณคือ SID และ SOD และสัญญาณเหล่านี้ใช้สำหรับการสื่อสารแบบอนุกรม

SOD (Serial output data line) - SOD เอาต์พุตถูกตั้งค่า / รีเซ็ตตามที่ระบุโดยคำสั่ง SIM

SID (สายข้อมูลอินพุตแบบอนุกรม) - ข้อมูลในบรรทัดนี้จะถูกโหลดลงในแอคคูมูเลเตอร์เมื่อใดก็ตามที่มีการดำเนินการคำสั่ง RIM

ตอนนี้ให้เราพูดคุยเกี่ยวกับโหมดการกำหนดแอดเดรสในไมโครโปรเซสเซอร์ 8085

โหมดที่อยู่ใน 8085

นี่คือคำแนะนำที่ใช้ในการถ่ายโอนข้อมูลจากรีจิสเตอร์หนึ่งไปยังรีจิสเตอร์อื่นจากหน่วยความจำไปยังรีจิสเตอร์และจากรีจิสเตอร์ไปยังหน่วยความจำโดยไม่มีการเปลี่ยนแปลงใด ๆ ในเนื้อหา โหมดการกำหนดแอดเดรสใน 8085 แบ่งออกเป็น 5 กลุ่ม -

โหมดกำหนดแอดเดรสทันที

ในโหมดนี้ข้อมูล 8/16 บิตถูกระบุในคำสั่งเป็นหนึ่งในตัวถูกดำเนินการ For example: MVI K, 20F: หมายถึง 20F ถูกคัดลอกไปยังรีจิสเตอร์ K

ลงทะเบียนโหมดการกำหนดที่อยู่

ในโหมดนี้ข้อมูลจะถูกคัดลอกจากทะเบียนหนึ่งไปยังอีกทะเบียนหนึ่ง For example: MOV K, B: หมายถึงข้อมูลในรีจิสเตอร์ B ถูกคัดลอกไปลงทะเบียน K

โหมดกำหนดแอดเดรสโดยตรง

ในโหมดนี้ข้อมูลจะถูกคัดลอกโดยตรงจากที่อยู่ที่ระบุไปยังรีจิสเตอร์ For example: LDB 5000K: หมายถึงข้อมูลที่อยู่ 5000K ถูกคัดลอกเพื่อลงทะเบียน B

โหมดที่อยู่ทางอ้อม

ในโหมดนี้ข้อมูลจะถูกถ่ายโอนจากรีจิสเตอร์หนึ่งไปยังอีกรีจิสเตอร์โดยใช้แอดเดรสที่ระบุโดยรีจิสเตอร์ For example: MOV K, B: หมายถึงข้อมูลถูกถ่ายโอนจากที่อยู่หน่วยความจำที่ระบุโดยรีจิสเตอร์ไปยังรีจิสเตอร์ K

โหมดการกำหนดแอดเดรสโดยนัย

โหมดนี้ไม่ต้องการตัวถูกดำเนินการใด ๆ ข้อมูลถูกระบุโดย opcode เองFor example: CMP.

ขัดจังหวะใน 8085

อินเทอร์รัปต์คือสัญญาณที่สร้างขึ้นโดยอุปกรณ์ภายนอกเพื่อขอให้ไมโครโปรเซสเซอร์ทำงาน มีสัญญาณขัดจังหวะ 5 สัญญาณ ได้แก่ TRAP, RST 7.5, RST 6.5, RST 5.5 และ INTR

การขัดจังหวะแบ่งออกเป็นกลุ่มต่อไปนี้ตามพารามิเตอร์ -

Vector interrupt - ในการขัดจังหวะประเภทนี้โพรเซสเซอร์จะทราบที่อยู่ของการขัดจังหวะ For example: RST7.5, RST6.5, RST5.5, TRAP

Non-Vector interrupt - ในการขัดจังหวะประเภทนี้โปรเซสเซอร์ไม่รู้จักที่อยู่ของการขัดจังหวะดังนั้นที่อยู่ของการขัดจังหวะจะต้องถูกส่งไปภายนอกโดยอุปกรณ์เพื่อดำเนินการขัดจังหวะ For example: INTR.

Maskable interrupt - ในการขัดจังหวะประเภทนี้เราสามารถปิดใช้งานการขัดจังหวะโดยเขียนคำสั่งบางอย่างลงในโปรแกรม For example: RST7.5, RST6.5, RST5.5

Non-Maskable interrupt - ในการขัดจังหวะประเภทนี้เราไม่สามารถปิดการใช้งานการขัดจังหวะโดยการเขียนคำสั่งบางอย่างลงในโปรแกรม For example: กับดัก

Software interrupt- ในการขัดจังหวะประเภทนี้โปรแกรมเมอร์จะต้องเพิ่มคำสั่งลงในโปรแกรมเพื่อดำเนินการขัดจังหวะ มีซอฟต์แวร์ขัดจังหวะ 8 ตัวใน 8085 ได้แก่ RST0, RST1, RST2, RST3, RST4, RST5, RST6 และ RST7

Hardware interrupt - มีพินอินเทอร์รัปต์ 5 พินใน 8085 ที่ใช้เป็นตัวขัดจังหวะฮาร์ดแวร์ ได้แก่ TRAP, RST7.5, RST6.5, RST5.5, INTA

Note- NTA ไม่ใช่การขัดจังหวะ แต่จะใช้โดยไมโครโปรเซสเซอร์เพื่อส่งการตอบรับ TRAP มีลำดับความสำคัญสูงสุดตามด้วย RST7.5 และอื่น ๆ

Interrupt Service Routine (ISR)

โปรแกรมขนาดเล็กหรือรูทีนที่เมื่อเรียกใช้งานจะให้บริการที่มาของการขัดจังหวะที่เกี่ยวข้องเรียกว่า ISR

กับดัก

เป็นการขัดจังหวะแบบไม่ปิดบังซึ่งมีลำดับความสำคัญสูงสุดในบรรดาอินเทอร์รัปต์ทั้งหมด Bydefault จะเปิดใช้งานจนกว่าจะได้รับการตอบรับ ในกรณีที่เกิดความล้มเหลวจะดำเนินการเป็น ISR และส่งข้อมูลไปยังหน่วยความจำสำรอง การขัดจังหวะนี้จะถ่ายโอนการควบคุมไปยังตำแหน่ง 0024H

RST7.5

เป็นการขัดจังหวะแบบสวมหน้ากากได้ซึ่งมีลำดับความสำคัญสูงสุดเป็นอันดับสองในบรรดาอินเทอร์รัปต์ทั้งหมด เมื่อการขัดจังหวะนี้ถูกดำเนินการโปรเซสเซอร์จะบันทึกเนื้อหาของการลงทะเบียนพีซีลงในสแต็กและแตกแขนงไปยังที่อยู่ 003CH

RST 6.5

เป็นการขัดจังหวะแบบสวมหน้ากากได้ซึ่งมีลำดับความสำคัญสูงสุดเป็นอันดับสามของการขัดจังหวะทั้งหมด เมื่อการขัดจังหวะนี้ถูกดำเนินการโปรเซสเซอร์จะบันทึกเนื้อหาของการลงทะเบียนพีซีลงในสแต็กและแตกแขนงไปยังที่อยู่ 0034H

RST 5.5

เป็นการขัดจังหวะแบบสวมหน้ากากได้ เมื่อการขัดจังหวะนี้ถูกเรียกใช้โปรเซสเซอร์จะบันทึกเนื้อหาของการลงทะเบียนพีซีลงในสแต็กและแตกแขนงไปยังที่อยู่ 002CH

INTR

เป็นการขัดจังหวะแบบสวมหน้ากากได้ซึ่งมีลำดับความสำคัญต่ำที่สุดในบรรดาอินเทอร์รัปต์ทั้งหมด สามารถปิดใช้งานได้โดยการรีเซ็ตไมโครโปรเซสเซอร์

เมื่อไหร่ INTR signal goes highเหตุการณ์ต่อไปนี้อาจเกิดขึ้นได้ -

ไมโครโปรเซสเซอร์จะตรวจสอบสถานะของสัญญาณ INTR ระหว่างการดำเนินการของแต่ละคำสั่ง

เมื่อสัญญาณ INTR สูงไมโครโปรเซสเซอร์จะดำเนินการตามคำสั่งปัจจุบันและส่งสัญญาณรับทราบการขัดจังหวะต่ำที่ใช้งานอยู่

เมื่อได้รับคำแนะนำไมโครโปรเซสเซอร์จะบันทึกที่อยู่ของคำสั่งถัดไปบนสแตกและดำเนินการตามคำสั่งที่ได้รับ

มาดูการเขียนโปรแกรมของไมโครโปรเซสเซอร์ 8085

ชุดคำสั่งคือรหัสคำสั่งในการทำงานบางอย่าง แบ่งออกเป็นห้าประเภท

| ส. | คำแนะนำและคำอธิบาย |

|---|---|

| 1 | คำแนะนำในการควบคุม ต่อไปนี้เป็นตารางแสดงรายการคำสั่ง Control พร้อมความหมาย |

| 2 | คำแนะนำเชิงตรรกะ ต่อไปนี้เป็นตารางแสดงรายการคำสั่งตรรกะพร้อมความหมาย |

| 3 | คำแนะนำในการแยกสาขา ต่อไปนี้เป็นตารางแสดงรายการคำสั่งการแตกแขนงพร้อมความหมาย |

| 4 | คำแนะนำทางคณิตศาสตร์ ต่อไปนี้เป็นตารางแสดงรายการคำสั่งเลขคณิตพร้อมความหมาย |

| 5 | คำแนะนำในการโอนข้อมูล ต่อไปนี้เป็นตารางแสดงรายการคำแนะนำการโอนข้อมูลพร้อมความหมาย |

8085 - โปรแกรมสาธิต

ตอนนี้ให้เราดูการสาธิตโปรแกรมโดยใช้คำแนะนำด้านบน -

การเพิ่มตัวเลข 8 บิตสองตัว

เขียนโปรแกรมเพื่อเพิ่มข้อมูลที่ตำแหน่งหน่วยความจำ 3005H & 3006H และจัดเก็บผลลัพธ์ที่ตำแหน่งหน่วยความจำ 3007H

Problem demo -

(3005H) = 14H

(3006H) = 89HResult -

14H + 89H = 9DH

โค้ดโปรแกรมสามารถเขียนได้ดังนี้ -

LXI H 3005H : "HL points 3005H"

MOV A, M : "Getting first operand"

INX H : "HL points 3006H"

ADD M : "Add second operand"

INX H : "HL points 3007H"

MOV M, A : "Store result at 3007H"

HLT : "Exit program"การแลกเปลี่ยนตำแหน่งหน่วยความจำ

เขียนโปรแกรมเพื่อแลกเปลี่ยนข้อมูลที่ตำแหน่งหน่วยความจำ 5000M และ 6000M

LDA 5000M : "Getting the contents at5000M location into accumulator"

MOV B, A : "Save the contents into B register"

LDA 6000M : "Getting the contents at 6000M location into accumulator"

STA 5000M : "Store the contents of accumulator at address 5000M"

MOV A, B : "Get the saved contents back into A register"

STA 6000M : "Store the contents of accumulator at address 6000M"จัดเรียงตัวเลขตามลำดับจากน้อยไปมาก

เขียนโปรแกรมเพื่อจัดเรียงตัวเลข 10 ตัวแรกจากที่อยู่หน่วยความจำ 3000H ตามลำดับจากน้อยไปมาก

MVI B, 09 :"Initialize counter"

START :"LXI H, 3000H: Initialize memory pointer"

MVI C, 09H :"Initialize counter 2"

BACK: MOV A, M :"Get the number"

INX H :"Increment memory pointer"

CMP M :"Compare number with next number"

JC SKIP :"If less, don’t interchange"

JZ SKIP :"If equal, don’t interchange"

MOV D, M

MOV M, A

DCX H

MOV M, D

INX H :"Interchange two numbers"

SKIP:DCR C :"Decrement counter 2"

JNZ BACK :"If not zero, repeat"

DCR B :"Decrement counter 1"

JNZ START

HLT :"Terminate program execution"8086 Microprocessor เป็นรุ่นปรับปรุงของ 8085Microprocessor ซึ่งออกแบบโดย Intel ในปี 1976 เป็นไมโครโปรเซสเซอร์ 16 บิตที่มีบรรทัดแอดเดรส 20 บรรทัดและสายข้อมูล 16 สายที่ให้พื้นที่เก็บข้อมูลสูงสุด 1MB ประกอบด้วยชุดคำสั่งที่มีประสิทธิภาพซึ่งให้การดำเนินการเช่นการคูณและการหารได้อย่างง่ายดาย

รองรับโหมดการทำงานสองโหมด ได้แก่ โหมดสูงสุดและโหมดต่ำสุด โหมดสูงสุดเหมาะสำหรับระบบที่มีโปรเซสเซอร์หลายตัวและโหมดต่ำสุดเหมาะสำหรับระบบที่มีโปรเซสเซอร์ตัวเดียว

คุณสมบัติของ 8086

คุณสมบัติที่โดดเด่นที่สุดของไมโครโปรเซสเซอร์ 8086 มีดังต่อไปนี้ -

มีคิวคำสั่งซึ่งสามารถจัดเก็บหกไบต์คำสั่งจากหน่วยความจำทำให้การประมวลผลเร็วขึ้น

เป็นโปรเซสเซอร์ 16 บิตตัวแรกที่มี ALU 16 บิตรีจิสเตอร์ 16 บิตบัสข้อมูลภายในและบัสข้อมูลภายนอก 16 บิตทำให้การประมวลผลเร็วขึ้น

มีให้เลือก 3 รุ่นตามความถี่ในการใช้งาน -

8086 → 5MHz

8086-2 → 8 เมกะเฮิร์ตซ์

(ค) 8086-1 → 10 MHz

ใช้สองขั้นตอนของการไปป์ไลน์คือ Fetch Stage และ Execute Stage ซึ่งช่วยเพิ่มประสิทธิภาพ

ขั้นตอนการดึงข้อมูลสามารถดึงคำสั่งล่วงหน้าได้ถึง 6 ไบต์และเก็บไว้ในคิว

Execute stage เรียกใช้คำสั่งเหล่านี้

มันมีการขัดจังหวะ 256 vectored

It consists of 29,000 transistors.

Comparison between 8085 & 8086 Microprocessor

Size − 8085 is 8-bit microprocessor, whereas 8086 is 16-bit microprocessor.

Address Bus − 8085 has 16-bit address bus while 8086 has 20-bit address bus.

Memory − 8085 can access up to 64Kb, whereas 8086 can access up to 1 Mb of memory.

Instruction − 8085 doesn’t have an instruction queue, whereas 8086 has an instruction queue.

Pipelining − 8085 doesn’t support a pipelined architecture while 8086 supports a pipelined architecture.

I/O − 8085 can address 2^8 = 256 I/O's, whereas 8086 can access 2^16 = 65,536 I/O's.

Cost − The cost of 8085 is low whereas that of 8086 is high.

Architecture of 8086

The following diagram depicts the architecture of a 8086 Microprocessor −

8086 Microprocessor is divided into two functional units, i.e., EU (Execution Unit) and BIU (Bus Interface Unit).

EU (Execution Unit)

Execution unit gives instructions to BIU stating from where to fetch the data and then decode and execute those instructions. Its function is to control operations on data using the instruction decoder & ALU. EU has no direct connection with system buses as shown in the above figure, it performs operations over data through BIU.

Let us now discuss the functional parts of 8086 microprocessors.

ALU

It handles all arithmetic and logical operations, like +, −, ×, /, OR, AND, NOT operations.

Flag Register

It is a 16-bit register that behaves like a flip-flop, i.e. it changes its status according to the result stored in the accumulator. It has 9 flags and they are divided into 2 groups − Conditional Flags and Control Flags.

Conditional Flags

It represents the result of the last arithmetic or logical instruction executed. Following is the list of conditional flags −

Carry flag − This flag indicates an overflow condition for arithmetic operations.

Auxiliary flag − When an operation is performed at ALU, it results in a carry/barrow from lower nibble (i.e. D0 – D3) to upper nibble (i.e. D4 – D7), then this flag is set, i.e. carry given by D3 bit to D4 is AF flag. The processor uses this flag to perform binary to BCD conversion.

Parity flag − This flag is used to indicate the parity of the result, i.e. when the lower order 8-bits of the result contains even number of 1’s, then the Parity Flag is set. For odd number of 1’s, the Parity Flag is reset.

Zero flag − This flag is set to 1 when the result of arithmetic or logical operation is zero else it is set to 0.

Sign flag − This flag holds the sign of the result, i.e. when the result of the operation is negative, then the sign flag is set to 1 else set to 0.

Overflow flag − This flag represents the result when the system capacity is exceeded.

Control Flags

Control flags controls the operations of the execution unit. Following is the list of control flags −

Trap flag − It is used for single step control and allows the user to execute one instruction at a time for debugging. If it is set, then the program can be run in a single step mode.

Interrupt flag − It is an interrupt enable/disable flag, i.e. used to allow/prohibit the interruption of a program. It is set to 1 for interrupt enabled condition and set to 0 for interrupt disabled condition.

Direction flag − It is used in string operation. As the name suggests when it is set then string bytes are accessed from the higher memory address to the lower memory address and vice-a-versa.

General purpose register

There are 8 general purpose registers, i.e., AH, AL, BH, BL, CH, CL, DH, and DL. These registers can be used individually to store 8-bit data and can be used in pairs to store 16bit data. The valid register pairs are AH and AL, BH and BL, CH and CL, and DH and DL. It is referred to the AX, BX, CX, and DX respectively.

AX register − It is also known as accumulator register. It is used to store operands for arithmetic operations.

BX register − It is used as a base register. It is used to store the starting base address of the memory area within the data segment.

CX register − It is referred to as counter. It is used in loop instruction to store the loop counter.

DX register − This register is used to hold I/O port address for I/O instruction.

Stack pointer register

It is a 16-bit register, which holds the address from the start of the segment to the memory location, where a word was most recently stored on the stack.

BIU (Bus Interface Unit)

BIU takes care of all data and addresses transfers on the buses for the EU like sending addresses, fetching instructions from the memory, reading data from the ports and the memory as well as writing data to the ports and the memory. EU has no direction connection with System Buses so this is possible with the BIU. EU and BIU are connected with the Internal Bus.

It has the following functional parts −

Instruction queue − BIU contains the instruction queue. BIU gets upto 6 bytes of next instructions and stores them in the instruction queue. When EU executes instructions and is ready for its next instruction, then it simply reads the instruction from this instruction queue resulting in increased execution speed.

Fetching the next instruction while the current instruction executes is called pipelining.

Segment register − BIU has 4 segment buses, i.e. CS, DS, SS& ES. It holds the addresses of instructions and data in memory, which are used by the processor to access memory locations. It also contains 1 pointer register IP, which holds the address of the next instruction to executed by the EU.

CS − It stands for Code Segment. It is used for addressing a memory location in the code segment of the memory, where the executable program is stored.

DS − It stands for Data Segment. It consists of data used by the program andis accessed in the data segment by an offset address or the content of other register that holds the offset address.

SS − It stands for Stack Segment. It handles memory to store data and addresses during execution.

ES − It stands for Extra Segment. ES is additional data segment, which is used by the string to hold the extra destination data.

Instruction pointer − It is a 16-bit register used to hold the address of the next instruction to be executed.

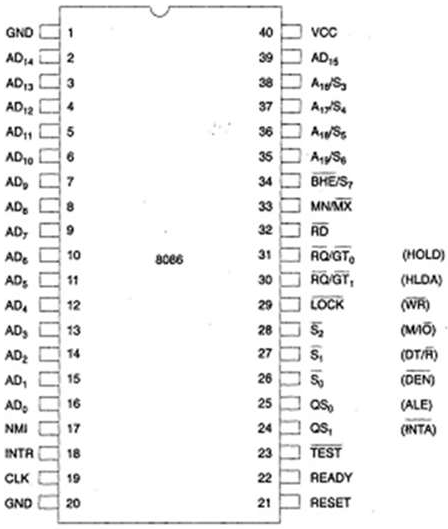

8086 was the first 16-bit microprocessor available in 40-pin DIP (Dual Inline Package) chip. Let us now discuss in detail the pin configuration of a 8086 Microprocessor.

8086 Pin Diagram

Here is the pin diagram of 8086 microprocessor −

Let us now discuss the signals in detail −

Power supply and frequency signals

It uses 5V DC supply at VCC pin 40, and uses ground at VSS pin 1 and 20 for its operation.

Clock signal

Clock signal is provided through Pin-19. It provides timing to the processor for operations. Its frequency is different for different versions, i.e. 5MHz, 8MHz and 10MHz.

Address/data bus

AD0-AD15. These are 16 address/data bus. AD0-AD7 carries low order byte data and AD8AD15 carries higher order byte data. During the first clock cycle, it carries 16-bit address and after that it carries 16-bit data.

Address/status bus

A16-A19/S3-S6. These are the 4 address/status buses. During the first clock cycle, it carries 4-bit address and later it carries status signals.

S7/BHE

BHE stands for Bus High Enable. It is available at pin 34 and used to indicate the transfer of data using data bus D8-D15. This signal is low during the first clock cycle, thereafter it is active.

Read($\overline{RD}$)

It is available at pin 32 and is used to read signal for Read operation.

Ready

It is available at pin 22. It is an acknowledgement signal from I/O devices that data is transferred. It is an active high signal. When it is high, it indicates that the device is ready to transfer data. When it is low, it indicates wait state.

RESET

It is available at pin 21 and is used to restart the execution. It causes the processor to immediately terminate its present activity. This signal is active high for the first 4 clock cycles to RESET the microprocessor.

INTR

It is available at pin 18. It is an interrupt request signal, which is sampled during the last clock cycle of each instruction to determine if the processor considered this as an interrupt or not.

NMI

It stands for non-maskable interrupt and is available at pin 17. It is an edge triggered input, which causes an interrupt request to the microprocessor.

$\overline{TEST}$

This signal is like wait state and is available at pin 23. When this signal is high, then the processor has to wait for IDLE state, else the execution continues.

MN/$\overline{MX}$

It stands for Minimum/Maximum and is available at pin 33. It indicates what mode the processor is to operate in; when it is high, it works in the minimum mode and vice-aversa.

INTA

It is an interrupt acknowledgement signal and id available at pin 24. When the microprocessor receives this signal, it acknowledges the interrupt.

ALE

It stands for address enable latch and is available at pin 25. A positive pulse is generated each time the processor begins any operation. This signal indicates the availability of a valid address on the address/data lines.

DEN

It stands for Data Enable and is available at pin 26. It is used to enable Transreceiver 8286. The transreceiver is a device used to separate data from the address/data bus.

DT/R

It stands for Data Transmit/Receive signal and is available at pin 27. It decides the direction of data flow through the transreceiver. When it is high, data is transmitted out and vice-a-versa.

M/IO

This signal is used to distinguish between memory and I/O operations. When it is high, it indicates I/O operation and when it is low indicates the memory operation. It is available at pin 28.

WR

It stands for write signal and is available at pin 29. It is used to write the data into the memory or the output device depending on the status of M/IO signal.

HLDA

It stands for Hold Acknowledgement signal and is available at pin 30. This signal acknowledges the HOLD signal.

HOLD

This signal indicates to the processor that external devices are requesting to access the address/data buses. It is available at pin 31.

QS1 and QS0

These are queue status signals and are available at pin 24 and 25. These signals provide the status of instruction queue. Their conditions are shown in the following table −

| QS0 | QS1 | Status |

|---|---|---|

| 0 | 0 | No operation |

| 0 | 1 | First byte of opcode from the queue |

| 1 | 0 | Empty the queue |

| 1 | 1 | Subsequent byte from the queue |

S0, S1, S2

These are the status signals that provide the status of operation, which is used by the Bus Controller 8288 to generate memory & I/O control signals. These are available at pin 26, 27, and 28. Following is the table showing their status −

| S2 | S1 | S0 | Status |

|---|---|---|---|

| 0 | 0 | 0 | Interrupt acknowledgement |

| 0 | 0 | 1 | I/O Read |

| 0 | 1 | 0 | I/O Write |

| 0 | 1 | 1 | Halt |

| 1 | 0 | 0 | Opcode fetch |

| 1 | 0 | 1 | Memory read |

| 1 | 1 | 0 | Memory write |

| 1 | 1 | 1 | Passive |

LOCK

When this signal is active, it indicates to the other processors not to ask the CPU to leave the system bus. It is activated using the LOCK prefix on any instruction and is available at pin 29.

RQ/GT1 and RQ/GT0

These are the Request/Grant signals used by the other processors requesting the CPU to release the system bus. When the signal is received by CPU, then it sends acknowledgment. RQ/GT0 has a higher priority than RQ/GT1.

The 8086 microprocessor supports 8 types of instructions −

- Data Transfer Instructions

- Arithmetic Instructions

- Bit Manipulation Instructions

- String Instructions

- Program Execution Transfer Instructions (Branch & Loop Instructions)

- Processor Control Instructions

- Iteration Control Instructions

- Interrupt Instructions

Let us now discuss these instruction sets in detail.

Data Transfer Instructions

These instructions are used to transfer the data from the source operand to the destination operand. Following are the list of instructions under this group −

Instruction to transfer a word

MOV − Used to copy the byte or word from the provided source to the provided destination.

PPUSH − Used to put a word at the top of the stack.

POP − Used to get a word from the top of the stack to the provided location.

PUSHA − Used to put all the registers into the stack.

POPA − Used to get words from the stack to all registers.

XCHG − Used to exchange the data from two locations.

XLAT − Used to translate a byte in AL using a table in the memory.

Instructions for input and output port transfer

IN − Used to read a byte or word from the provided port to the accumulator.

OUT − Used to send out a byte or word from the accumulator to the provided port.

Instructions to transfer the address

LEA − Used to load the address of operand into the provided register.

LDS − Used to load DS register and other provided register from the memory

LES − Used to load ES register and other provided register from the memory.

Instructions to transfer flag registers

LAHF − Used to load AH with the low byte of the flag register.

SAHF − Used to store AH register to low byte of the flag register.

PUSHF − Used to copy the flag register at the top of the stack.

POPF − Used to copy a word at the top of the stack to the flag register.

Arithmetic Instructions

These instructions are used to perform arithmetic operations like addition, subtraction, multiplication, division, etc.

Following is the list of instructions under this group −

Instructions to perform addition

ADD − Used to add the provided byte to byte/word to word.

ADC − Used to add with carry.

INC − Used to increment the provided byte/word by 1.

AAA − Used to adjust ASCII after addition.

DAA − Used to adjust the decimal after the addition/subtraction operation.

Instructions to perform subtraction

SUB − Used to subtract the byte from byte/word from word.

SBB − Used to perform subtraction with borrow.

DEC − Used to decrement the provided byte/word by 1.

NPG − Used to negate each bit of the provided byte/word and add 1/2’s complement.

CMP − Used to compare 2 provided byte/word.

AAS − Used to adjust ASCII codes after subtraction.

DAS − Used to adjust decimal after subtraction.

Instruction to perform multiplication

MUL − Used to multiply unsigned byte by byte/word by word.

IMUL − Used to multiply signed byte by byte/word by word.

AAM − Used to adjust ASCII codes after multiplication.

Instructions to perform division

DIV − Used to divide the unsigned word by byte or unsigned double word by word.

IDIV − Used to divide the signed word by byte or signed double word by word.

AAD − Used to adjust ASCII codes after division.

CBW − Used to fill the upper byte of the word with the copies of sign bit of the lower byte.

CWD − Used to fill the upper word of the double word with the sign bit of the lower word.

Bit Manipulation Instructions

These instructions are used to perform operations where data bits are involved, i.e. operations like logical, shift, etc.

Following is the list of instructions under this group −

Instructions to perform logical operation

NOT − Used to invert each bit of a byte or word.

AND − Used for adding each bit in a byte/word with the corresponding bit in another byte/word.

OR − Used to multiply each bit in a byte/word with the corresponding bit in another byte/word.

XOR − Used to perform Exclusive-OR operation over each bit in a byte/word with the corresponding bit in another byte/word.

TEST − Used to add operands to update flags, without affecting operands.

Instructions to perform shift operations

SHL/SAL − Used to shift bits of a byte/word towards left and put zero(S) in LSBs.

SHR − Used to shift bits of a byte/word towards the right and put zero(S) in MSBs.

SAR − Used to shift bits of a byte/word towards the right and copy the old MSB into the new MSB.

Instructions to perform rotate operations

ROL − Used to rotate bits of byte/word towards the left, i.e. MSB to LSB and to Carry Flag [CF].

ROR − Used to rotate bits of byte/word towards the right, i.e. LSB to MSB and to Carry Flag [CF].

RCR − Used to rotate bits of byte/word towards the right, i.e. LSB to CF and CF to MSB.

RCL − Used to rotate bits of byte/word towards the left, i.e. MSB to CF and CF to LSB.

String Instructions

String is a group of bytes/words and their memory is always allocated in a sequential order.

Following is the list of instructions under this group −

REP − Used to repeat the given instruction till CX ≠ 0.

REPE/REPZ − Used to repeat the given instruction until CX = 0 or zero flag ZF = 1.

REPNE/REPNZ − Used to repeat the given instruction until CX = 0 or zero flag ZF = 1.

MOVS/MOVSB/MOVSW − Used to move the byte/word from one string to another.

COMS/COMPSB/COMPSW − Used to compare two string bytes/words.

INS/INSB/INSW − Used as an input string/byte/word from the I/O port to the provided memory location.

OUTS/OUTSB/OUTSW − Used as an output string/byte/word from the provided memory location to the I/O port.

SCAS/SCASB/SCASW − Used to scan a string and compare its byte with a byte in AL or string word with a word in AX.

LODS/LODSB/LODSW − Used to store the string byte into AL or string word into AX.

คำแนะนำในการโอนย้ายโปรแกรม (คำแนะนำสาขาและวนซ้ำ)

คำแนะนำเหล่านี้ใช้เพื่อโอน / แยกคำสั่งระหว่างการดำเนินการ ประกอบด้วยคำแนะนำต่อไปนี้ -

คำแนะนำในการถ่ายโอนคำสั่งระหว่างการดำเนินการโดยไม่มีเงื่อนไขใด ๆ -

CALL - ใช้เพื่อเรียกโพรซีเดอร์และบันทึกที่อยู่ผู้ส่งลงในสแต็ก

RET - ใช้เพื่อกลับจากขั้นตอนไปยังโปรแกรมหลัก

JMP - ใช้เพื่อข้ามไปยังที่อยู่ที่ให้ไว้เพื่อดำเนินการตามคำแนะนำถัดไป

คำแนะนำในการถ่ายโอนคำสั่งระหว่างการดำเนินการโดยมีเงื่อนไขบางประการ -

JA/JNBE - ใช้เพื่อกระโดดหากคำสั่งสูงกว่า / ไม่ต่ำกว่า / เท่ากัน

JAE/JNB - ใช้เพื่อกระโดดหากตรงตามคำแนะนำด้านบน / ไม่ต่ำกว่า

JBE/JNA - ใช้เพื่อกระโดดหากตรงตามคำสั่งต่ำกว่า / เท่ากัน / ไม่สูงกว่า

JC - ใช้ในการกระโดดหากถือธง CF = 1

JE/JZ - ใช้เพื่อกระโดดถ้าธงเท่ากับ / ศูนย์ ZF = 1

JG/JNLE - ใช้เพื่อกระโดดหากคำสั่งมากกว่า / ไม่น้อยกว่า / เท่ากัน

JGE/JNL - ใช้เพื่อกระโดดถ้ามากกว่า / เท่ากับ / ไม่น้อยกว่าคำแนะนำ

JL/JNGE - ใช้เพื่อกระโดดหากคำสั่งน้อยกว่า / ไม่มากกว่า / เท่ากัน

JLE/JNG - ใช้ในการกระโดดถ้าน้อยกว่า / เท่ากับ / ถ้าไม่มากกว่าคำแนะนำที่เป็นไปตามข้อกำหนด

JNC - ใช้ในการกระโดดหากไม่มีธงนำ (CF = 0)

JNE/JNZ - ใช้เพื่อกระโดดหากไม่เท่ากัน / ธงศูนย์ ZF = 0

JNO - ใช้เพื่อกระโดดหากไม่มีแฟล็กล้นของ = 0

JNP/JPO - ใช้เพื่อกระโดดหากไม่ใช่พาริตี / พาริตีคี่ PF = 0

JNS - ใช้เพื่อกระโดดหากไม่ลงชื่อ SF = 0

JO - ใช้เพื่อกระโดดหากแฟล็กล้นของ = 1

JP/JPE - ใช้เพื่อกระโดดถ้า parity / parity แม้ PF = 1

JS - ใช้เพื่อกระโดดถ้า sign flag SF = 1

คำแนะนำในการควบคุมโปรเซสเซอร์

คำแนะนำเหล่านี้ใช้เพื่อควบคุมการดำเนินการของโปรเซสเซอร์โดยการตั้งค่า / รีเซ็ตค่าแฟล็ก

ต่อไปนี้เป็นคำแนะนำในกลุ่มนี้ -

STC - ใช้เพื่อตั้งค่าสถานะพกพา CF เป็น 1

CLC - ใช้เพื่อล้าง / รีเซ็ตค่าสถานะพกพา CF เป็น 0

CMC - ใช้เพื่อเติมเต็มในสถานะของการถือธง CF

STD - ใช้เพื่อตั้งค่าสถานะทิศทาง DF เป็น 1

CLD - ใช้เพื่อล้าง / รีเซ็ตค่าสถานะทิศทาง DF เป็น 0

STI - ใช้เพื่อตั้งค่าแฟล็กเปิดใช้งานการขัดจังหวะเป็น 1 เช่นเปิดใช้งานอินพุต INTR

CLI - ใช้เพื่อล้างการขัดจังหวะเปิดใช้งานแฟล็กเป็น 0 เช่นปิดการใช้งานอินพุต INTR

คำแนะนำในการควบคุมการทำซ้ำ

คำแนะนำเหล่านี้ใช้เพื่อดำเนินการตามคำแนะนำที่กำหนดเป็นจำนวนครั้ง ต่อไปนี้เป็นรายการคำแนะนำในกลุ่มนี้ -

LOOP - ใช้เพื่อวนซ้ำกลุ่มคำสั่งจนกว่าเงื่อนไขจะเป็นไปตามนั้นเช่น CX = 0

LOOPE/LOOPZ - ใช้เพื่อวนซ้ำกลุ่มคำสั่งจนกว่าจะเป็นไปตาม ZF = 1 & CX = 0

LOOPNE/LOOPNZ - ใช้เพื่อวนซ้ำกลุ่มคำสั่งจนกว่าจะเป็นไปตาม ZF = 0 & CX = 0

JCXZ - ใช้เพื่อข้ามไปยังที่อยู่ที่ให้ไว้หาก CX = 0

คำแนะนำในการขัดจังหวะ

คำแนะนำเหล่านี้ใช้เพื่อเรียกการขัดจังหวะระหว่างการทำงานของโปรแกรม

INT - ใช้เพื่อขัดจังหวะโปรแกรมระหว่างดำเนินการและเรียกใช้บริการที่ระบุ

INTO - ใช้เพื่อขัดจังหวะโปรแกรมระหว่างการดำเนินการถ้า OF = 1

IRET - ใช้เพื่อกลับจากบริการขัดจังหวะไปยังโปรแกรมหลัก

Interruptเป็นวิธีการสร้างการหยุดชั่วคราวระหว่างการทำงานของโปรแกรมและอนุญาตให้อุปกรณ์ต่อพ่วงเข้าถึงไมโครโปรเซสเซอร์ ไมโครโปรเซสเซอร์ตอบสนองต่อการขัดจังหวะนั้นด้วยไฟล์ISR (Interrupt Service Routine) ซึ่งเป็นโปรแกรมสั้น ๆ ในการสั่งไมโครโปรเซสเซอร์เกี่ยวกับวิธีจัดการกับการขัดจังหวะ

ภาพต่อไปนี้แสดงประเภทของการขัดจังหวะที่เรามีในไมโครโปรเซสเซอร์ 8086 -

ฮาร์ดแวร์ขัดจังหวะ

การขัดจังหวะของฮาร์ดแวร์เกิดจากอุปกรณ์ต่อพ่วงใด ๆ โดยการส่งสัญญาณผ่านพินที่ระบุไปยังไมโครโปรเซสเซอร์

8086 มีพินขัดจังหวะฮาร์ดแวร์สองตัวคือ NMI และ INTR NMI เป็นอินเทอร์รัปต์ที่ไม่สามารถปิดบังได้และ INTR คืออินเทอร์รัปต์ที่สามารถปกปิดได้ซึ่งมีลำดับความสำคัญต่ำ อีกหนึ่งพินอินเทอร์รัปต์ที่เกี่ยวข้องคือ INTA เรียกว่าอินเตอร์รัปต์รับทราบ

NMI

เป็นพินอินเทอร์รัปต์ (NMI) ที่ไม่สามารถปกปิดได้เพียงตัวเดียวที่มีลำดับความสำคัญสูงกว่าพินคำขอขัดจังหวะแบบมาสก์ (INTR) และเป็นอินเตอร์รัปต์ประเภท 2

เมื่อเปิดใช้งานการขัดจังหวะนี้การดำเนินการเหล่านี้จะเกิดขึ้น -

ดำเนินการตามคำสั่งปัจจุบันที่กำลังดำเนินการอยู่

พุชค่าแฟล็กรีจิสเตอร์บนสแต็ก

พุชค่า CS (ส่วนรหัส) และค่า IP (ตัวชี้คำสั่ง) ของที่อยู่ที่ส่งคืนไปยังสแต็ก

IP ถูกโหลดจากเนื้อหาของคำว่าตำแหน่ง 00008H

CS ถูกโหลดจากเนื้อหาของตำแหน่งคำถัดไป 0000AH

แฟล็กอินเตอร์รัปต์และแฟล็กกับดักถูกรีเซ็ตเป็น 0

INTR

INTR เป็นอินเทอร์รัปต์ที่สามารถปกปิดได้เนื่องจากไมโครโปรเซสเซอร์จะถูกขัดจังหวะก็ต่อเมื่อมีการเปิดใช้งานอินเทอร์รัปต์โดยใช้คำสั่ง set interrupt flag ไม่ควรเปิดใช้งานโดยใช้คำสั่ง clear interrupt Flag

INTR interrupt ถูกเปิดใช้งานโดยพอร์ต I / O หากเปิดใช้งานการขัดจังหวะและ NMI ถูกปิดใช้งานไมโครโปรเซสเซอร์จะทำการดำเนินการปัจจุบันให้เสร็จสมบูรณ์ก่อนและส่ง '0' บนขา INTA สองครั้ง '0' ตัวแรกหมายถึง INTA แจ้งให้อุปกรณ์ภายนอกเตรียมพร้อมและในระหว่าง '0' ที่สองไมโครโปรเซสเซอร์จะรับ 8 บิตพูดว่า X จากตัวควบคุมขัดจังหวะที่ตั้งโปรแกรมได้

ไมโครโปรเซสเซอร์ดำเนินการเหล่านี้ -

ขั้นแรกให้ทำตามคำสั่งปัจจุบัน

เปิดใช้งานเอาต์พุต INTA และรับประเภทการขัดจังหวะ X พูดว่า

ค่าแฟล็กรีจิสเตอร์ค่า CS ของที่อยู่ผู้ส่งคืนและค่า IP ของที่อยู่ผู้ส่งจะถูกพุชไปที่สแต็ก

ค่า IP ถูกโหลดจากเนื้อหาของตำแหน่งคำ X × 4

CS ถูกโหลดจากเนื้อหาของตำแหน่งคำถัดไป

อินเตอร์รัปต์แฟล็กและแฟล็กกับดักถูกรีเซ็ตเป็น 0

ซอฟต์แวร์ขัดจังหวะ

คำแนะนำบางอย่างจะถูกแทรกในตำแหน่งที่ต้องการลงในโปรแกรมเพื่อสร้างอินเทอร์รัปต์ คำแนะนำการขัดจังหวะเหล่านี้สามารถใช้เพื่อทดสอบการทำงานของตัวจัดการขัดจังหวะต่างๆ ประกอบด้วย -

INT- ขัดคำสั่งด้วยหมายเลขประเภท

เป็นคำสั่ง 2 ไบต์ ไบต์แรกให้รหัส op และไบต์ที่สองระบุหมายเลขประเภทการขัดจังหวะ มีการขัดจังหวะ 256 ประเภทภายใต้กลุ่มนี้

การดำเนินการรวมถึงขั้นตอนต่อไปนี้ -

ค่าแฟล็กรีจิสเตอร์จะถูกพุชไปที่สแต็ก

ค่า CS ของที่อยู่ผู้ส่งคืนและค่า IP ของที่อยู่ผู้ส่งจะถูกพุชไปที่สแต็ก

IP ถูกโหลดจากเนื้อหาของตำแหน่งคำว่า 'type number' × 4

CS ถูกโหลดจากเนื้อหาของตำแหน่งคำถัดไป

Interrupt Flag และ Trap Flag ถูกรีเซ็ตเป็น 0

ที่อยู่เริ่มต้นสำหรับอินเตอร์รัปต์ type0 คือ 000000H สำหรับอินเตอร์รัปต์ type1 คือ 00004H ในทำนองเดียวกันสำหรับ type2 คือ 00008H และ……เป็นต้น พอยน์เตอร์ห้าตัวแรกเป็นพอยน์เตอร์ขัดจังหวะโดยเฉพาะ กล่าวคือ -

TYPE 0 การขัดจังหวะแสดงถึงการแบ่งตามสถานการณ์เป็นศูนย์

TYPE 1 การขัดจังหวะหมายถึงการดำเนินการขั้นตอนเดียวในระหว่างการดีบักของโปรแกรม

TYPE 2 การขัดจังหวะหมายถึงการขัดจังหวะ NMI ที่ไม่สามารถปิดบังได้

TYPE 3 การขัดจังหวะหมายถึงการขัดจังหวะจุดพัก

TYPE 4 การขัดจังหวะหมายถึงการขัดจังหวะล้น

การขัดจังหวะจาก Type 5 ถึง Type 31 สงวนไว้สำหรับไมโครโปรเซสเซอร์ขั้นสูงอื่น ๆ และอินเตอร์รัปต์จาก 32 ถึง Type 255 พร้อมใช้งานสำหรับการขัดจังหวะฮาร์ดแวร์และซอฟต์แวร์

INT 3-Break Point Interrupt คำแนะนำ

เป็นคำสั่ง 1 ไบต์ที่มีรหัส op คือ CCH คำแนะนำเหล่านี้จะถูกแทรกลงในโปรแกรมเพื่อที่เมื่อโปรเซสเซอร์ไปถึงที่นั่นก็จะหยุดการทำงานปกติของโปรแกรมและทำตามขั้นตอนจุดพัก

การดำเนินการรวมถึงขั้นตอนต่อไปนี้ -

ค่าแฟล็กรีจิสเตอร์จะถูกพุชไปที่สแต็ก

ค่า CS ของที่อยู่ผู้ส่งคืนและค่า IP ของที่อยู่ผู้ส่งจะถูกพุชไปที่สแต็ก

IP ถูกโหลดจากเนื้อหาของตำแหน่งคำ 3 × 4 = 0000CH

CS ถูกโหลดจากเนื้อหาของตำแหน่งคำถัดไป

Interrupt Flag และ Trap Flag ถูกรีเซ็ตเป็น 0

INTO - ขัดจังหวะคำสั่งล้น

มันเป็นคำสั่ง 1 ไบต์และช่วยในการจำ INTO. op-code สำหรับคำสั่งนี้คือ CEH ตามที่ชื่อแนะนำว่าเป็นคำสั่งขัดจังหวะแบบมีเงื่อนไขกล่าวคือจะทำงานเฉพาะเมื่อตั้งค่าแฟล็กโอเวอร์โฟลว์เป็น 1 และแตกแขนงไปยังตัวจัดการขัดจังหวะที่มีหมายเลขประเภทการขัดจังหวะคือ 4 หากแฟล็กโอเวอร์โฟลว์ถูกรีเซ็ตการดำเนินการจะดำเนินต่อไป คำแนะนำต่อไป

การดำเนินการรวมถึงขั้นตอนต่อไปนี้ -

ค่าแฟล็กรีจิสเตอร์จะถูกพุชไปที่สแต็ก

ค่า CS ของที่อยู่ผู้ส่งคืนและค่า IP ของที่อยู่ผู้ส่งจะถูกพุชไปที่สแต็ก

IP ถูกโหลดจากเนื้อหาของตำแหน่งคำ 4 × 4 = 00010H

CS ถูกโหลดจากเนื้อหาของตำแหน่งคำถัดไป

อินเตอร์รัปต์แฟล็กและแฟล็กกับดักถูกรีเซ็ตเป็น 0

วิธีต่างๆที่ซอร์สถูกแสดงในคำสั่งเรียกว่า addressing modes. มี 8 โหมดการกำหนดแอดเดรสที่แตกต่างกันในการเขียนโปรแกรม 8086 -

โหมดกำหนดแอดเดรสทันที

โหมดการกำหนดแอดเดรสซึ่งตัวถูกดำเนินการข้อมูลเป็นส่วนหนึ่งของคำสั่งนั้นเรียกว่าโหมดกำหนดแอดเดรสทันที

ตัวอย่าง

MOV CX, 4929 H, ADD AX, 2387 H, MOV AL, FFHลงทะเบียนโหมดการกำหนดที่อยู่

หมายความว่ารีจิสเตอร์เป็นแหล่งที่มาของตัวถูกดำเนินการสำหรับคำสั่ง

ตัวอย่าง

MOV CX, AX ; copies the contents of the 16-bit AX register into

; the 16-bit CX register),

ADD BX, AXโหมดกำหนดแอดเดรสโดยตรง

โหมดการกำหนดแอดเดรสซึ่งที่อยู่ที่มีประสิทธิภาพของตำแหน่งหน่วยความจำถูกเขียนโดยตรงในคำสั่ง

ตัวอย่าง

MOV AX, [1592H], MOV AL, [0300H]ลงทะเบียนโหมดการกำหนดแอดเดรสทางอ้อม

โหมดกำหนดแอดเดรสนี้ช่วยให้สามารถส่งข้อมูลไปยังตำแหน่งหน่วยความจำใด ๆ ผ่านที่อยู่ออฟเซ็ตที่อยู่ในรีจิสเตอร์ต่อไปนี้: BP, BX, DI & SI

ตัวอย่าง

MOV AX, [BX] ; Suppose the register BX contains 4895H, then the contents

; 4895H are moved to AX

ADD CX, {BX}ตามโหมดการกำหนดที่อยู่

ในโหมดการกำหนดแอดเดรสนี้แอดเดรสออฟเซ็ตของตัวถูกดำเนินการจะได้รับจากผลรวมของเนื้อหาของรีจิสเตอร์ BX / BP และการกระจัด 8 บิต / 16 บิต

ตัวอย่าง

MOV DX, [BX+04], ADD CL, [BX+08]โหมดกำหนดแอดเดรสที่จัดทำดัชนี

ในโหมดการกำหนดแอดเดรสนี้จะพบแอดเดรสออฟเซ็ตของตัวถูกดำเนินการโดยการเพิ่มเนื้อหาของการลงทะเบียน SI หรือ DI และการกระจัด 8 บิต / 16 บิต

ตัวอย่าง

MOV BX, [SI+16], ADD AL, [DI+16]ตามดัชนีที่อยู่โหมด

ในโหมดการกำหนดแอดเดรสนี้แอดเดรสออฟเซ็ตของตัวถูกดำเนินการจะคำนวณโดยการรวมรีจิสเตอร์ฐานกับเนื้อหาของรีจิสเตอร์ดัชนี

ตัวอย่าง

ADD CX, [AX+SI], MOV AX, [AX+DI]ตามดัชนีด้วยโหมดการกระจัด

ในโหมดการกำหนดแอดเดรสนี้ออฟเซ็ตตัวถูกดำเนินการจะคำนวณโดยการเพิ่มเนื้อหารีจิสเตอร์ฐาน ดัชนีจะลงทะเบียนเนื้อหาและการกระจัด 8 หรือ 16 บิต

ตัวอย่าง

MOV AX, [BX+DI+08], ADD CX, [BX+SI+16]Multiprocessor หมายถึงชุดของโปรเซสเซอร์หลายชุดที่รันคำสั่งพร้อมกัน มีคอนฟิกูเรชันมัลติโปรเซสเซอร์พื้นฐานสามแบบ

- การกำหนดค่าตัวประมวลผลร่วม

- การกำหนดค่าควบคู่กันอย่างใกล้ชิด

- การกำหนดค่าควบคู่กันอย่างหลวม ๆ

การกำหนดค่าตัวประมวลผลร่วม

ตัวประมวลผลร่วมเป็นวงจรที่ออกแบบมาเป็นพิเศษบนชิปไมโครโปรเซสเซอร์ซึ่งสามารถทำงานเดียวกันได้อย่างรวดเร็วซึ่งไมโครโปรเซสเซอร์ทำงาน ช่วยลดภาระการทำงานของโปรเซสเซอร์หลัก ตัวประมวลผลร่วมใช้หน่วยความจำเดียวกันระบบ IO บัสตรรกะควบคุมและตัวสร้างสัญญาณนาฬิกา ตัวประมวลผลร่วมจะจัดการกับงานเฉพาะทางเช่นการคำนวณทางคณิตศาสตร์การแสดงผลแบบกราฟิกบนหน้าจอเป็นต้น

8086 และ 8088 สามารถดำเนินการได้เกือบทั้งหมด แต่ชุดคำสั่งไม่สามารถดำเนินการทางคณิตศาสตร์ที่ซับซ้อนได้ดังนั้นในกรณีเหล่านี้ไมโครโปรเซสเซอร์ต้องใช้ตัวประมวลผลร่วมทางคณิตศาสตร์เช่นโปรเซสเซอร์ร่วมคณิตศาสตร์ Intel 8087 ซึ่งสามารถดำเนินการเหล่านี้ได้อย่างรวดเร็ว

แผนภาพบล็อกของการกำหนดค่าตัวประมวลผลร่วม

ตัวประมวลผลร่วมและโปรเซสเซอร์เชื่อมต่อกันอย่างไร?

โปรเซสเซอร์ร่วมและประมวลผลที่มีการเชื่อมต่อผ่านการทดสอบ RQ- / GT- และ QS 0 & QS 1สัญญาณ

สัญญาณ TEST เชื่อมต่อกับพิน BUSY ของตัวประมวลผลร่วมและอีก 3 พินที่เหลือเชื่อมต่อกับ 3 พินของตัวประมวลผลร่วมที่มีชื่อเดียวกัน

สัญญาณทดสอบจะดูแลกิจกรรมของตัวประมวลผลร่วมกล่าวคือตัวประมวลผลร่วมไม่ว่างหรือไม่ได้ใช้งาน

RT- / GT- ใช้สำหรับอนุญาโตตุลาการรถบัส

ตัวประมวลผลร่วมใช้ QS 0 & QS 1เพื่อติดตามสถานะของคิวของตัวประมวลผลโฮสต์

การกำหนดค่าควบคู่อย่างใกล้ชิด

คอนฟิกูเรชันแบบใกล้ชิดจะคล้ายกับคอนฟิกูเรชันตัวประมวลผลร่วมกล่าวคือทั้งสองใช้หน่วยความจำเดียวกันบัสระบบ I / O ลอจิกควบคุมและตัวสร้างการควบคุมกับโปรเซสเซอร์โฮสต์ อย่างไรก็ตามตัวประมวลผลร่วมและตัวประมวลผลโฮสต์ดึงข้อมูลและดำเนินการตามคำสั่งของตนเอง บัสระบบถูกควบคุมโดยตัวประมวลผลร่วมและตัวประมวลผลโฮสต์แยกกัน

แผนภาพบล็อกของการกำหนดค่าควบคู่อย่างใกล้ชิด

โปรเซสเซอร์และโปรเซสเซอร์อิสระเชื่อมต่อกันอย่างไร?

การสื่อสารระหว่างโฮสต์และโปรเซสเซอร์อิสระจะกระทำผ่านพื้นที่หน่วยความจำ

ไม่มีคำแนะนำใด ๆ ที่ใช้ในการสื่อสารเช่น WAIT, ESC เป็นต้น

โปรเซสเซอร์โฮสต์จะจัดการหน่วยความจำและปลุกโปรเซสเซอร์อิสระโดยส่งคำสั่งไปยังพอร์ตใดพอร์ตหนึ่ง

จากนั้นโปรเซสเซอร์อิสระจะเข้าถึงหน่วยความจำเพื่อดำเนินงาน

หลังจากเสร็จสิ้นภารกิจจะส่งการตอบรับไปยังโฮสต์โปรเซสเซอร์โดยใช้สัญญาณสถานะหรือคำขอขัดจังหวะ

การกำหนดค่าควบคู่กันอย่างหลวม ๆ

การกำหนดค่าคู่แบบหลวม ๆ ประกอบด้วยจำนวนโมดูลของระบบที่ใช้ไมโครโปรเซสเซอร์ซึ่งเชื่อมต่อผ่านบัสระบบทั่วไป แต่ละโมดูลประกอบด้วยตัวสร้างนาฬิกาหน่วยความจำอุปกรณ์ I / O ของตัวเองและเชื่อมต่อผ่านบัสท้องถิ่น

แผนภาพบล็อกของการกำหนดค่าควบคู่หลวม ๆ

ข้อดี

การมีโปรเซสเซอร์มากกว่าหนึ่งตัวส่งผลให้ประสิทธิภาพเพิ่มขึ้น

โปรเซสเซอร์แต่ละตัวมีบัสท้องถิ่นของตัวเองเพื่อเข้าถึงอุปกรณ์หน่วยความจำ / I / O ในเครื่อง ทำให้ง่ายต่อการประมวลผลแบบขนาน

โครงสร้างระบบมีความยืดหยุ่นกล่าวคือความล้มเหลวของโมดูลหนึ่งจะไม่ส่งผลต่อความล้มเหลวทั้งระบบ โมดูลที่ผิดพลาดสามารถเปลี่ยนได้ในภายหลัง

8087 ตัวประมวลผลข้อมูลตัวเลขเป็นที่รู้จักกันในชื่อ Math co-processor, Numeric processor extension และ Floating point unit. นับเป็นโปรเซสเซอร์ร่วมทางคณิตศาสตร์ตัวแรกที่ออกแบบโดย Intel เพื่อจับคู่กับ 8086/8088 ทำให้การคำนวณง่ายขึ้นและเร็วขึ้น

เมื่อคำสั่งถูกระบุโดยโปรเซสเซอร์ 8086/8088 แล้วคำสั่งนั้นจะถูกกำหนดให้กับโปรเซสเซอร์ร่วม 8087 เพื่อดำเนินการต่อไป

ชนิดข้อมูลที่ 8087 รองรับ ได้แก่ -

- จำนวนเต็มไบนารี

- ตัวเลขทศนิยมที่บรรจุ

- ตัวเลขจริง

- รูปแบบจริงชั่วคราว

คุณสมบัติที่โดดเด่นที่สุดของตัวประมวลผลข้อมูลตัวเลข 8087 มีดังต่อไปนี้ -

รองรับข้อมูลประเภทจำนวนเต็มจำนวนลอยและประเภทจริงตั้งแต่ 2-10 ไบต์

ความเร็วในการประมวลผลสูงมากจนสามารถคำนวณการคูณของจำนวนจริง 64 บิตสองจำนวนใน ~ 27 µs และยังสามารถคำนวณสแควร์รูทได้ใน ~ 35 µs

เป็นไปตามมาตรฐานจุดลอยตัวของ IEEE

8087 สถาปัตยกรรม

8087 สถาปัตยกรรมแบ่งออกเป็นสองกลุ่มคือ Control Unit (CU) และ Numeric Extension Unit (NEU)

control unit จัดการการสื่อสารทั้งหมดระหว่างโปรเซสเซอร์และหน่วยความจำเช่นรับและถอดรหัสคำสั่งอ่านและเขียนตัวถูกดำเนินการหน่วยความจำรักษาคิวแบบขนาน ฯลฯ คำสั่งของตัวประมวลผลร่วมทั้งหมดเป็นคำสั่ง ESC กล่าวคือขึ้นต้นด้วย 'F' ตัวประมวลผลร่วมเท่านั้น ดำเนินการคำสั่ง ESC ในขณะที่คำสั่งอื่น ๆ ดำเนินการโดยไมโครโปรเซสเซอร์

numeric extension unitจัดการคำสั่งตัวประมวลผลตัวเลขทั้งหมดเช่นคำแนะนำทางคณิตศาสตร์ตรรกะยอดเยี่ยมและการถ่ายโอนข้อมูล มีสแต็กรีจิสเตอร์ 8 สแต็กซึ่งเก็บตัวถูกดำเนินการสำหรับคำแนะนำและผลลัพธ์

สถาปัตยกรรมของตัวประมวลผลร่วม 8087 มีดังต่อไปนี้ -

8087 คำอธิบายพิน

ก่อนอื่นให้เราดูที่แผนภาพพินของ 8087 -

รายการต่อไปนี้แสดงคำอธิบายพินของ 8087 -

AD0 – AD15 - นี่คือที่อยู่ / สายข้อมูลแบบมัลติเพล็กซ์ซึ่งมีที่อยู่ระหว่างรอบนาฬิกาแรกและข้อมูลจากรอบนาฬิกาที่สองเป็นต้นไป

A19 / S6 – A16/S- เส้นเหล่านี้คือเส้นเวลาที่อยู่ / สถานะแบบมัลติเพล็กซ์ มันทำงานในลักษณะเดียวกับหมุดที่สอดคล้องกันของ 8086 S 6 , S 4และ S3 สูงอย่างถาวรในขณะที่ S 5อยู่ในระดับต่ำอย่างถาวร

$\overline{BHE}$/S7 - ระหว่างรอบนาฬิกาแรก $\overline{BHE}$/ S 7จะใช้ในการเปิดใช้งานข้อมูลไปยังไบต์สูงของบัสข้อมูล 8086 และหลังจากนั้นผลงานที่เป็นบรรทัดสถานะ S 7

QS1, QS0 - นี่คือสัญญาณอินพุตสถานะคิวซึ่งให้สถานะของคิวคำสั่งเงื่อนไขดังแสดงในตารางต่อไปนี้ -

| คำพูดคำจา0 | คำพูดคำจา1 | สถานะ |

|---|---|---|

| 0 | 0 | ไม่มีการดำเนินการ |

| 0 | 1 | ไบต์แรกของ opcode จากคิว |

| 1 | 0 | ล้างคิว |

| 1 | 1 | ไบต์ที่ตามมาจากคิว |

INT - เป็นสัญญาณขัดจังหวะซึ่งจะเปลี่ยนเป็นระดับสูงเมื่อได้รับข้อยกเว้นที่ไม่ได้มาสก์ระหว่างการดำเนินการ

BUSY - เป็นสัญญาณเอาท์พุตเมื่ออยู่ในระดับสูงจะแสดงสถานะไม่ว่างต่อ CPU

READY - เป็นสัญญาณอินพุตที่ใช้เพื่อแจ้งให้โปรเซสเซอร์ร่วมทราบว่าบัสพร้อมที่จะรับข้อมูลหรือไม่

RESET - เป็นสัญญาณอินพุตที่ใช้เพื่อปฏิเสธกิจกรรมภายในของตัวประมวลผลร่วมและเตรียมสำหรับการดำเนินการเพิ่มเติมเมื่อใดก็ตามที่ CPU ต้องการ

CLK - อินพุต CLK มีการกำหนดเวลาพื้นฐานสำหรับการทำงานของโปรเซสเซอร์

VCC - เป็นสัญญาณแหล่งจ่ายไฟซึ่งต้องใช้แหล่งจ่ายไฟ + 5V สำหรับการทำงานของวงจร

S0, S1, S2- นี่คือสัญญาณสถานะที่ให้สถานะของการทำงานซึ่งใช้โดย Bus Controller 8087 เพื่อสร้างหน่วยความจำและสัญญาณควบคุม I / O สัญญาณเหล่านี้จะทำงานในรอบนาฬิกาที่สี่

| ส2 | ส1 | S 0 | สถานะคิว |

|---|---|---|---|

| 0 | X | X | ไม่ได้ใช้ |

| 1 | 0 | 0 | ไม่ได้ใช้ |

| 1 | 0 | 1 | อ่านหน่วยความจำ |

| 1 | 1 | 0 | เขียนหน่วยความจำ |

| 1 | 1 | 1 | เรื่อย ๆ |

RQ/GT1 & RQ/GT0 - นี่คือไฟล์ Request/Grant สัญญาณที่ใช้โดยโปรเซสเซอร์ 8087 เพื่อควบคุมบัสจากโฮสต์โปรเซสเซอร์ 8086/8088 สำหรับการถ่ายโอนตัวถูกดำเนินการ

ในบทนี้เราจะกล่าวถึงการเชื่อมต่อหน่วยความจำและการเชื่อมต่อ IO กับ 8085

Interfaceเป็นเส้นทางสำหรับการสื่อสารระหว่างสององค์ประกอบ การเชื่อมต่อมีสองประเภทคือการเชื่อมต่อหน่วยความจำและการเชื่อมต่อ I / O

การเชื่อมต่อหน่วยความจำ

เมื่อเราดำเนินการคำสั่งใด ๆ เราจำเป็นต้องใช้ไมโครโปรเซสเซอร์เพื่อเข้าถึงหน่วยความจำเพื่ออ่านรหัสคำสั่งและข้อมูลที่จัดเก็บไว้ในหน่วยความจำ สำหรับสิ่งนี้ทั้งหน่วยความจำและไมโครโปรเซสเซอร์ต้องใช้สัญญาณบางอย่างในการอ่านและเขียนลงทะเบียน

กระบวนการเชื่อมต่อประกอบด้วยปัจจัยสำคัญบางประการเพื่อให้ตรงกับข้อกำหนดหน่วยความจำและสัญญาณไมโครโปรเซสเซอร์ ดังนั้นวงจรเชื่อมต่อจึงควรได้รับการออกแบบให้ตรงกับความต้องการสัญญาณหน่วยความจำกับสัญญาณของไมโครโปรเซสเซอร์

การเชื่อมต่อ IO

มีอุปกรณ์สื่อสารต่างๆเช่นแป้นพิมพ์เมาส์เครื่องพิมพ์ ฯลฯ ดังนั้นเราจำเป็นต้องเชื่อมต่อแป้นพิมพ์และอุปกรณ์อื่น ๆ กับไมโครโปรเซสเซอร์โดยใช้สลักและบัฟเฟอร์ การเชื่อมต่อประเภทนี้เรียกว่าอินเทอร์เฟซ I / O

แผนภาพบล็อกของหน่วยความจำและการเชื่อมต่อ I / O

8085 หมุดเชื่อมต่อ

ต่อไปนี้เป็นรายการหมุด 8085 ที่ใช้สำหรับเชื่อมต่อกับอุปกรณ์อื่น ๆ -

- A 15 - A 8 (บัสที่อยู่สูงกว่า)

- ค.ศ. 7 - AD 0 (ที่อยู่ด้านล่าง / บัสข้อมูล)

- ALE

- RD

- WR

- READY

วิธีการสื่อสาร - ไมโครโปรเซสเซอร์กับโลกภายนอก?

มีสองวิธีในการสื่อสารที่ไมโครโปรเซสเซอร์สามารถเชื่อมต่อกับโลกภายนอกได้

- อินเตอร์เฟซการสื่อสารแบบอนุกรม

- อินเตอร์เฟซการสื่อสารแบบขนาน

Serial Communication Interface - ในการสื่อสารประเภทนี้อินเทอร์เฟซจะรับข้อมูลไบต์เดียวจากไมโครโปรเซสเซอร์และส่งทีละบิตไปยังระบบอื่น ๆ แบบอนุกรมและในทางกลับกัน

Parallel Communication Interface - ในการสื่อสารประเภทนี้อินเทอร์เฟซรับข้อมูลไบต์จากไมโครโปรเซสเซอร์และส่งทีละบิตไปยังระบบอื่น ๆ ในรูปแบบคู่ขนานพร้อมกัน (หรือ) และในทางกลับกัน

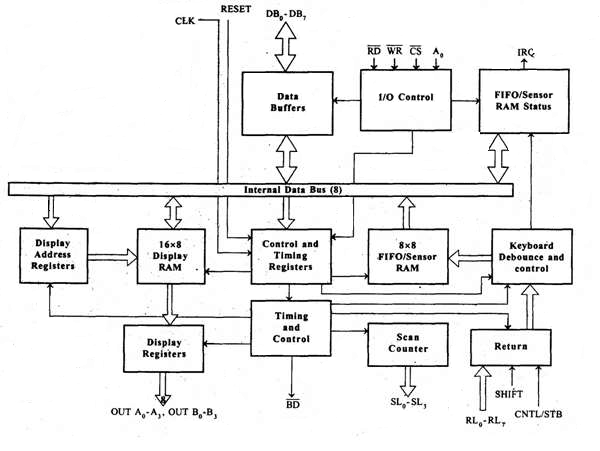

แป้นพิมพ์ / จอแสดงผลที่ตั้งโปรแกรมได้ 8279 ได้รับการออกแบบโดย Intel ที่เชื่อมต่อแป้นพิมพ์กับ CPU แป้นพิมพ์จะสแกนแป้นพิมพ์ก่อนและระบุว่ามีการกดแป้นใด จากนั้นจะส่งการตอบสนองสัมพัทธ์ของคีย์ที่กดไปยัง CPU และในทางกลับกัน

คีย์บอร์ดเชื่อมต่อกับ CPU ได้กี่วิธี?

แป้นพิมพ์สามารถเชื่อมต่อได้ทั้งในโหมดขัดจังหวะหรือโหมดโพล ในInterrupt modeโปรเซสเซอร์จะได้รับการร้องขอบริการก็ต่อเมื่อกดปุ่มใด ๆ มิฉะนั้น CPU จะทำงานหลักต่อไป

ใน Polled modeซีพียูจะอ่านแฟล็กภายในของ 8279 เป็นระยะเพื่อตรวจสอบว่ามีการกดปุ่มใด ๆ หรือไม่ด้วยการกดปุ่ม

แป้นพิมพ์ 8279 ทำงานอย่างไร

แป้นพิมพ์ประกอบด้วยปุ่มสูงสุด 64 ปุ่มซึ่งเชื่อมต่อกับ CPU โดยใช้คีย์ - รหัส คีย์ - โค้ดเหล่านี้จะถูกยกเลิกการเด้งและจัดเก็บไว้ใน FIFORAM 8 ไบต์ซึ่ง CPU สามารถเข้าถึงได้ หากป้อนมากกว่า 8 อักขระใน FIFO หมายความว่ามีการกดมากกว่าแปดปุ่มในแต่ละครั้ง นี่คือเมื่อมีการตั้งค่าสถานะโอเวอร์รัน

หาก FIFO มีรายการคีย์ที่ถูกต้อง CPU จะถูกขัดจังหวะในโหมดอินเตอร์รัปต์มิฉะนั้น CPU จะตรวจสอบสถานะในการสำรวจเพื่ออ่านรายการ เมื่อ CPU อ่านรายการคีย์แล้ว FIFO จะได้รับการอัปเดตและรายการคีย์จะถูกผลักออกจาก FIFO เพื่อสร้างพื้นที่สำหรับรายการใหม่

สถาปัตยกรรมและคำอธิบาย

การควบคุม I / O และบัฟเฟอร์ข้อมูล

หน่วยนี้ควบคุมการไหลของข้อมูลผ่านไมโครโปรเซสเซอร์ จะเปิดใช้งานเมื่อ D ต่ำเท่านั้น บัฟเฟอร์ข้อมูลเชื่อมต่อบัสภายนอกของระบบกับบัสภายในของไมโครโปรเซสเซอร์ พิน A0, RD และ WR ใช้สำหรับคำสั่งสถานะหรือการอ่าน / เขียนข้อมูล

การควบคุมและการลงทะเบียนเวลาและการควบคุมเวลา

หน่วยนี้ประกอบด้วยรีจิสเตอร์เพื่อจัดเก็บคีย์บอร์ดโหมดการแสดงผลและการทำงานอื่น ๆ ตามที่ CPU ตั้งโปรแกรมไว้ ชุดจับเวลาและชุดควบคุมจะจัดการกับการกำหนดเวลาสำหรับการทำงานของวงจร

สแกนเคาน์เตอร์

มีสองโหมดคือ Encoded modeและโหมดถอดรหัส ในโหมดเข้ารหัสตัวนับจะให้จำนวนไบนารีที่จะถอดรหัสจากภายนอกเพื่อจัดเตรียมเส้นสแกนสำหรับแป้นพิมพ์และการแสดงผล

ใน decoded scan modeเคาน์เตอร์ภายในถอดรหัสน้อยอย่างมีนัยสำคัญ 2 บิตและให้ถอดรหัส 1 ใน 4 สแกน SL 0 -sl 3

ส่งคืนบัฟเฟอร์การดีบักคีย์บอร์ดและการควบคุม

ขั้นแรกหน่วยนี้จะสแกนแถวปิดคีย์อย่างชาญฉลาดหากพบจากนั้นหน่วย debounce ของแป้นพิมพ์จะ deboun การป้อนคีย์ ในกรณีที่ตรวจพบคีย์เดียวกันรหัสของคีย์นั้นจะถูกโอนโดยตรงไปยัง RAM เซ็นเซอร์พร้อมกับสถานะคีย์ SHIFT & CONTROL

FIFO / Sensor RAM และ Status Logic

หน่วยนี้ทำหน้าที่เป็นแรม 8-byte first-in-first-out (FIFO) ซึ่งรหัสของคีย์ที่กดทุกปุ่มจะถูกป้อนลงใน RAM ตามลำดับ ตรรกะสถานะสร้างคำร้องขอขัดจังหวะหลังจากการดำเนินการอ่าน FIFO แต่ละครั้งจนกว่า FIFO จะว่างเปล่า

ในโหมดเมทริกซ์เซ็นเซอร์ที่สแกนหน่วยนี้จะทำหน้าที่เป็นแรมของเซ็นเซอร์โดยที่แต่ละแถวจะโหลดพร้อมกับสถานะของแถวเซ็นเซอร์ที่เกี่ยวข้องลงในเมทริกซ์ เมื่อเซ็นเซอร์เปลี่ยนสถานะสาย IRQ จะเปลี่ยนเป็นสูงและขัดจังหวะ CPU

แสดงที่อยู่รีจิสเตอร์และแสดง RAM

หน่วยนี้ประกอบด้วยรีจิสเตอร์ที่อยู่ที่แสดงซึ่งเก็บแอดเดรสของคำที่ CPU อ่าน / เขียนในปัจจุบันไปยัง / จากแรมที่แสดง

8279 - คำอธิบายพิน

รูปต่อไปนี้แสดงพินไดอะแกรมของ 8279 -

สายบัสข้อมูล DB 0 - DB 7

นี่คือสายบัสข้อมูลแบบสองทิศทาง 8 สายที่ใช้ในการถ่ายโอนข้อมูลไปยัง / จาก CPU

CLK

อินพุตนาฬิกาถูกใช้เพื่อสร้างการกำหนดเวลาภายในที่ต้องการโดยไมโครโปรเซสเซอร์

รีเซ็ต

ตามชื่อแสดงว่าพินนี้ใช้เพื่อรีเซ็ตไมโครโปรเซสเซอร์

CS Chip Select

เมื่อตั้งค่าพินนี้ไว้ต่ำจะทำให้สามารถอ่าน / เขียนได้ไม่เช่นนั้นควรตั้งค่าพินนี้เป็นสูง

ก0

พินนี้ระบุการถ่ายโอนข้อมูลคำสั่ง / สถานะ เมื่ออยู่ในระดับต่ำแสดงถึงการถ่ายโอนข้อมูล

RD, WR

พินอ่าน / เขียนนี้ช่วยให้บัฟเฟอร์ข้อมูลสามารถส่ง / รับข้อมูลผ่านบัสข้อมูล

IRQ

บรรทัดเอาต์พุตขัดจังหวะนี้จะสูงเมื่อมีข้อมูลในแรมเซ็นเซอร์ FIFO บรรทัดอินเทอร์รัปต์จะอยู่ในระดับต่ำเมื่อดำเนินการอ่าน FIFO RAM อย่างไรก็ตามหาก FIFO RAM มีรายการคีย์ - โค้ดที่จะอ่านโดย CPU เพิ่มเติมพินนี้จะสูงขึ้นอีกครั้งเพื่อสร้างอินเทอร์รัปต์ให้กับ CPU

V ss , V cc

นี่คือกราวด์และสายจ่ายไฟของไมโครโปรเซสเซอร์

SL 0 - SL 3

นี่คือเส้นสแกนที่ใช้ในการสแกนเมทริกซ์แป้นพิมพ์และแสดงตัวเลข บรรทัดเหล่านี้สามารถตั้งโปรแกรมเป็นเข้ารหัสหรือถอดรหัสโดยใช้รีจิสเตอร์ควบคุมโหมด

RL 0 - RL 7

นี่คือ Return Lines ซึ่งเชื่อมต่อกับเทอร์มินัลของคีย์หนึ่งในขณะที่เทอร์มินัลอื่น ๆ ของคีย์เชื่อมต่อกับเส้นสแกนที่ถอดรหัสแล้ว เส้นเหล่านี้ถูกตั้งค่าเป็น 0 เมื่อกดปุ่มใด ๆ

SHIFT

สถานะบรรทัดอินพุต Shift จะถูกจัดเก็บพร้อมกับรหัสคีย์ทั้งหมดใน FIFO ในโหมดแป้นพิมพ์ที่สแกน จนกว่ามันจะถูกดึงให้ต่ำด้วยการปิดกุญแจมันจะถูกดึงขึ้นภายในเพื่อให้สูง

CNTL / STB - โหมดควบคุม / STROBED I / P

ในโหมดแป้นพิมพ์บรรทัดนี้ใช้เป็นอินพุตควบคุมและเก็บไว้ใน FIFO เมื่อปิดคีย์ เส้นนี้เป็นเส้นแฟลชที่ป้อนข้อมูลลงใน FIFO RAM ในโหมดอินพุตแบบสโตรบ มีการดึงขึ้นภายใน สายถูกดึงลงโดยมีกุญแจปิด

BD

ย่อมาจากการแสดงผลว่างเปล่า ใช้เพื่อทำให้หน้าจอว่างเปล่าระหว่างการสลับตัวเลข

OUTA 0 - OUTA 3และ OUTB 0 - OUTB 3

นี่คือพอร์ตเอาต์พุตสำหรับรีจิสเตอร์การรีเฟรชจอแสดงผลภายใน 16x4 หรือ 16x8 หนึ่งพอร์ต ข้อมูลจากบรรทัดเหล่านี้จะซิงโครไนซ์กับเส้นสแกนเพื่อสแกนจอแสดงผลและแป้นพิมพ์

โหมดการทำงานของ 8279

มีสองโหมดการทำงานบน 8279 - Input Mode และ Output Mode.

โหมดอินพุต

โหมดนี้เกี่ยวข้องกับอินพุตที่กำหนดโดยแป้นพิมพ์และโหมดนี้แบ่งออกเป็น 3 โหมดเพิ่มเติม

Scanned Keyboard Mode- ในโหมดนี้เมทริกซ์หลักสามารถเชื่อมต่อได้โดยใช้การสแกนที่เข้ารหัสหรือถอดรหัส ในการสแกนที่เข้ารหัสแป้นพิมพ์ 8 × 8 หรือในการสแกนแบบถอดรหัสสามารถเชื่อมต่อแป้นพิมพ์ 4 × 8 ได้ รหัสของคีย์ที่กดพร้อมกับสถานะ SHIFT และ CONTROL จะถูกเก็บไว้ใน FIFO RAM

Scanned Sensor Matrix- ในโหมดนี้อาร์เรย์เซ็นเซอร์สามารถเชื่อมต่อกับโปรเซสเซอร์โดยใช้การสแกนตัวเข้ารหัสหรือตัวถอดรหัส ในการสแกนตัวเข้ารหัสสามารถเชื่อมต่อเมทริกซ์เซ็นเซอร์ 8 × 8 หรือด้วยเมทริกซ์เซ็นเซอร์สแกนตัวถอดรหัส 4 × 8 ได้

Strobed Input - ในโหมดนี้เมื่อตั้งค่าสายควบคุมเป็น 0 ข้อมูลในรายการส่งคืนจะถูกเก็บไว้ในไบต์ FIFO ไบต์

โหมดเอาต์พุต

โหมดนี้เกี่ยวข้องกับการดำเนินการที่เกี่ยวข้องกับการแสดงผล โหมดนี้แบ่งออกเป็นสองโหมดเอาต์พุต

Display Scan - โหมดนี้ช่วยให้สามารถจัดระเบียบจอแสดงผลมัลติเพล็กซ์แบบอักขระ 8/16 ตัวเป็นหน่วยแสดงผลคู่ 4 บิต / เดี่ยว 8 บิต

Display Entry - โหมดนี้ช่วยให้ป้อนข้อมูลเพื่อแสดงผลจากด้านขวา / ด้านซ้าย

DMA ย่อมาจาก Direct Memory Access ได้รับการออกแบบโดย Intel เพื่อถ่ายโอนข้อมูลในอัตราที่เร็วที่สุด ช่วยให้อุปกรณ์สามารถถ่ายโอนข้อมูลไปยัง / จากหน่วยความจำได้โดยตรงโดยไม่มีการรบกวนของ CPU

การใช้ตัวควบคุม DMA อุปกรณ์จะร้องขอให้ CPU เก็บข้อมูลที่อยู่และบัสควบคุมดังนั้นอุปกรณ์จึงมีอิสระในการถ่ายโอนข้อมูลไปยัง / จากหน่วยความจำโดยตรง การถ่ายโอนข้อมูล DMA จะเริ่มต้นหลังจากได้รับสัญญาณ HLDA จาก CPU เท่านั้น

DMA ดำเนินการอย่างไร?

ต่อไปนี้เป็นลำดับของการดำเนินการโดย DMA -

ในขั้นต้นเมื่ออุปกรณ์ใด ๆ ต้องส่งข้อมูลระหว่างอุปกรณ์และหน่วยความจำอุปกรณ์จะต้องส่งคำขอ DMA (DRQ) ไปยังตัวควบคุม DMA

ตัวควบคุม DMA ส่งคำขอ Hold (HRQ) ไปยัง CPU และรอให้ CPU ยืนยัน HLDA

จากนั้นไมโครโปรเซสเซอร์จะระบุสถานะบัสข้อมูลบัสแอดเดรสและบัสควบคุมทั้งหมด CPU ออกจากการควบคุมบัสและรับทราบคำขอ HOLD ผ่านสัญญาณ HLDA

ตอนนี้ CPU อยู่ในสถานะ HOLD และตัวควบคุม DMA ต้องจัดการการทำงานบนบัสระหว่าง CPU หน่วยความจำและอุปกรณ์ I / O

คุณสมบัติของ 8257

นี่คือรายการคุณสมบัติเด่นบางประการของ 8257 -

มีสี่ช่องสัญญาณซึ่งสามารถใช้กับอุปกรณ์ I / O สี่เครื่อง

แต่ละช่องมีที่อยู่ 16 บิตและตัวนับ 14 บิต

แต่ละช่องสามารถถ่ายโอนข้อมูลได้สูงสุด 64kb

แต่ละช่องสามารถตั้งโปรแกรมได้อย่างอิสระ

แต่ละช่องสามารถดำเนินการอ่านโอนเขียนโอนและตรวจสอบการดำเนินการโอน

สร้างสัญญาณ MARK ไปยังอุปกรณ์ต่อพ่วงที่มีการถ่ายโอน 128 ไบต์

ต้องใช้นาฬิกาเฟสเดียว

ความถี่มีตั้งแต่ 250Hz ถึง 3MHz

มันทำงานใน 2 โหมดกล่าวคือ Master mode และ Slave mode.

8257 สถาปัตยกรรม

ภาพต่อไปนี้แสดงสถาปัตยกรรมของ 8257 -

คำอธิบายพิน 8257

ภาพต่อไปนี้แสดงแผนภาพพินของคอนโทรลเลอร์ 8257 DMA -

DRQ 0 −DRQ3

เหล่านี้คืออินพุตคำขอ DMA สี่ช่องสัญญาณซึ่งอุปกรณ์ต่อพ่วงใช้สำหรับการใช้บริการ DMA เมื่อเลือกโหมดลำดับความสำคัญคงที่แล้ว DRQ 0จะมีลำดับความสำคัญสูงสุดและ DRQ 3มีลำดับความสำคัญต่ำที่สุด

DACK o - DACK 3

นี่คือบรรทัดรับทราบ DMA ที่ใช้งานต่ำซึ่งจะอัปเดตอุปกรณ์ต่อพ่วงที่ร้องขอเกี่ยวกับสถานะของคำขอโดย CPU เส้นเหล่านี้ยังสามารถทำหน้าที่เป็นเส้นแฟลชสำหรับอุปกรณ์ที่ร้องขอ

งo - ง7

สายข้อมูลเหล่านี้เป็นแบบสองทิศทางซึ่งใช้เพื่อเชื่อมต่อบัสระบบกับบัสข้อมูลภายในของคอนโทรลเลอร์ DMA ในโหมด Slave จะมีคำสั่งถึง 8257 และคำสถานะจาก 8257 ในโหมดหลักบรรทัดเหล่านี้จะใช้เพื่อส่งไบต์ที่สูงกว่าของแอดเดรสที่สร้างไปยังสลัก ที่อยู่นี้สลักเพิ่มเติมโดยใช้สัญญาณ ADSTB

IOR

เป็นสายอินพุตไตรสถานะแบบสองทิศทางที่ใช้งานอยู่ต่ำซึ่ง CPU ใช้เพื่ออ่านรีจิสเตอร์ภายในของ 8257 ในโหมด Slave ในโหมดหลักจะใช้เพื่ออ่านข้อมูลจากอุปกรณ์ต่อพ่วงระหว่างรอบการเขียนหน่วยความจำ

IOW

เป็นเส้นไตรสถานะสองทิศทางต่ำที่ใช้งานได้ซึ่งใช้ในการโหลดเนื้อหาของบัสข้อมูลไปยังการลงทะเบียนโหมด 8 บิตหรือไบต์บน / ล่างของการลงทะเบียนที่อยู่ DMA 16 บิตหรือการนับจำนวนเทอร์มินัล ในโหมดหลักจะใช้เพื่อโหลดข้อมูลไปยังอุปกรณ์ต่อพ่วงระหว่างรอบการอ่านหน่วยความจำ DMA

CLK

เป็นสัญญาณความถี่นาฬิกาที่จำเป็นสำหรับการทำงานภายในของ 8257

รีเซ็ต

สัญญาณนี้ใช้เพื่อรีเซ็ตคอนโทรลเลอร์ DMA โดยปิดใช้งานช่องสัญญาณ DMA ทั้งหมด

กo - ก3

นี่คือบรรทัดที่อยู่ที่มีนัยสำคัญน้อยที่สุดสี่บรรทัด ในโหมดทาสจะทำหน้าที่เป็นอินพุตซึ่งเลือกหนึ่งในรีจิสเตอร์ที่จะอ่านหรือเขียน ในโหมดหลักจะเป็นบรรทัดเอาต์พุตที่อยู่หน่วยความจำที่มีนัยสำคัญน้อยที่สุดสี่บรรทัดที่สร้างโดย 8257

CS

มันเป็นสายการเลือกชิปที่ใช้งานต่ำ ในโหมด Slave จะเปิดใช้งานการอ่าน / เขียนไปยัง / จาก 8257 ในโหมดหลักจะปิดใช้งานการอ่าน / เขียนไปยัง / จาก 8257

ก4 - ก7

นี่คือการตอดที่สูงขึ้นของที่อยู่ไบต์ที่ต่ำกว่าที่สร้างโดย DMA ในโหมดหลัก

พร้อม

เป็นสัญญาณอินพุตแบบอะซิงโครนัสที่มีการใช้งานสูงซึ่งทำให้ DMA พร้อมโดยการใส่สถานะรอ

HRQ

สัญญาณนี้ใช้เพื่อรับสัญญาณขอพักจากอุปกรณ์เอาท์พุต ในโหมดทาสจะเชื่อมต่อด้วยสายอินพุต DRQ 8257 ในโหมด Master จะเชื่อมต่อกับอินพุต HOLD ของ CPU

HLDA

เป็นสัญญาณตอบรับการระงับซึ่งระบุตัวควบคุม DMA ว่าซีพียูได้รับบัสไปยังอุปกรณ์ต่อพ่วงที่ร้องขอเมื่อตั้งค่าเป็น 1

MEMR

เป็นสัญญาณการอ่านหน่วยความจำต่ำซึ่งใช้ในการอ่านข้อมูลจากตำแหน่งหน่วยความจำที่กำหนดแอดเดรสระหว่างรอบการอ่าน DMA

MEMW

เป็นสัญญาณสถานะสามสถานะที่ใช้งานต่ำซึ่งใช้ในการเขียนข้อมูลไปยังตำแหน่งหน่วยความจำที่กำหนดแอดเดรสระหว่างการดำเนินการเขียน DMA

ADST

สัญญาณนี้ใช้เพื่อแปลงไบต์ที่สูงกว่าของที่อยู่หน่วยความจำที่สร้างโดยตัวควบคุม DMA ลงในสลัก

AEN

สัญญาณนี้ใช้เพื่อปิดใช้งานแอดเดรสบัส / บัสข้อมูล

TC

ย่อมาจาก 'Terminal Count' ซึ่งระบุวัฏจักร DMA ปัจจุบันไปยังอุปกรณ์ต่อพ่วงในปัจจุบัน

เครื่องหมาย

เครื่องหมายจะเปิดใช้งานหลังจากทุกๆ 128 รอบหรือทวีคูณอินทิกรัลตั้งแต่เริ่มต้น ระบุว่าวงจร DMA ปัจจุบันเป็นรอบที่ 128 นับตั้งแต่เอาต์พุต MARK ก่อนหน้านี้ไปยังอุปกรณ์ต่อพ่วงที่เลือก

V ซีซี

เป็นสัญญาณไฟที่จำเป็นสำหรับการทำงานของวงจร

ก microcontroller เป็นไมโครคอมพิวเตอร์ขนาดเล็กและราคาประหยัดซึ่งออกแบบมาเพื่อทำงานเฉพาะของระบบฝังตัวเช่นการแสดงข้อมูลไมโครเวฟรับสัญญาณระยะไกลเป็นต้น

ไมโครคอนโทรลเลอร์ทั่วไปประกอบด้วยโปรเซสเซอร์หน่วยความจำ (RAM, ROM, EPROM) พอร์ตอนุกรมอุปกรณ์ต่อพ่วง (ตัวจับเวลาตัวนับ) ฯลฯ

ความแตกต่างระหว่างไมโครโปรเซสเซอร์และไมโครคอนโทรลเลอร์

ตารางต่อไปนี้เน้นความแตกต่างระหว่างไมโครโปรเซสเซอร์และไมโครคอนโทรลเลอร์ -

| ไมโครคอนโทรลเลอร์ | ไมโครโปรเซสเซอร์ |

|---|---|

| ไมโครคอนโทรลเลอร์ใช้เพื่อดำเนินการงานเดียวภายในแอปพลิเคชัน | ไมโครโปรเซสเซอร์ใช้สำหรับงานขนาดใหญ่ |

| ต้นทุนการออกแบบและฮาร์ดแวร์ต่ำ | ต้นทุนการออกแบบและฮาร์ดแวร์สูง |

| ง่ายต่อการเปลี่ยน | ไม่ใช่เรื่องง่ายที่จะเปลี่ยน |

| สร้างด้วยเทคโนโลยี CMOS ซึ่งใช้พลังงานน้อยลงในการทำงาน | การใช้พลังงานสูงเนื่องจากต้องควบคุมระบบทั้งหมด |

| ประกอบด้วยพอร์ต CPU, RAM, ROM, I / O | ไม่ประกอบด้วยพอร์ต RAM, ROM, I / O ใช้พินเพื่อเชื่อมต่อกับอุปกรณ์ต่อพ่วง |

ประเภทของไมโครคอนโทรลเลอร์

ไมโครคอนโทรลเลอร์แบ่งออกเป็นประเภทต่างๆตามหน่วยความจำสถาปัตยกรรมบิตและชุดคำสั่ง ต่อไปนี้เป็นรายการประเภท -

นิดหน่อย

ตามการกำหนดค่าบิตไมโครคอนโทรลเลอร์แบ่งออกเป็นสามประเภท

8-bit microcontroller - ไมโครคอนโทรลเลอร์ประเภทนี้ใช้เพื่อดำเนินการทางคณิตศาสตร์และตรรกะเช่นการบวกการลบการหารการคูณเป็นต้นตัวอย่างเช่น Intel 8031 และ 8051 เป็นไมโครคอนโทรลเลอร์ 8 บิต

16-bit microcontroller- ไมโครคอนโทรลเลอร์ประเภทนี้ใช้เพื่อดำเนินการทางคณิตศาสตร์และตรรกะที่ต้องการความแม่นยำและประสิทธิภาพที่สูงขึ้น ตัวอย่างเช่น Intel 8096 เป็นไมโครคอนโทรลเลอร์ 16 บิต

32-bit microcontroller - ไมโครคอนโทรลเลอร์ประเภทนี้มักใช้ในเครื่องใช้ที่ควบคุมโดยอัตโนมัติเช่นเครื่องปฏิบัติงานอัตโนมัติเครื่องใช้ทางการแพทย์เป็นต้น

หน่วยความจำ

ตามการกำหนดค่าหน่วยความจำไมโครคอนโทรลเลอร์แบ่งออกเป็นสองประเภท

External memory microcontroller- ไมโครคอนโทรลเลอร์ประเภทนี้ได้รับการออกแบบในลักษณะที่ไม่มีหน่วยความจำโปรแกรมบนชิป ดังนั้นจึงมีชื่อว่าไมโครคอนโทรลเลอร์หน่วยความจำภายนอก ตัวอย่างเช่นไมโครคอนโทรลเลอร์ Intel 8031

Embedded memory microcontroller- ไมโครคอนโทรลเลอร์ประเภทนี้ได้รับการออกแบบในลักษณะที่ไมโครคอนโทรลเลอร์มีโปรแกรมและหน่วยความจำข้อมูลตัวนับและตัวจับเวลาอินเตอร์รัปต์พอร์ต I / O ถูกฝังอยู่บนชิป ตัวอย่างเช่นไมโครคอนโทรลเลอร์ Intel 8051

ชุดคำสั่ง

จากการกำหนดค่าชุดคำสั่งไมโครคอนโทรลเลอร์ยังแบ่งออกเป็นสองประเภท

CISC- CISC ย่อมาจากคอมพิวเตอร์ชุดคำสั่งที่ซับซ้อน ช่วยให้ผู้ใช้สามารถแทรกคำสั่งเดียวเป็นทางเลือกแทนคำสั่งง่ายๆ

RISC- RISC ย่อมาจาก Reduced Instruction Set Computers ช่วยลดเวลาในการทำงานโดยการลดรอบนาฬิกาต่อคำสั่ง

การใช้งานไมโครคอนโทรลเลอร์

ไมโครคอนโทรลเลอร์ใช้กันอย่างแพร่หลายในอุปกรณ์ต่างๆเช่น -

อุปกรณ์ตรวจจับและควบคุมแสงเช่น LED

อุปกรณ์ตรวจจับและควบคุมอุณหภูมิเช่นเตาไมโครเวฟปล่องไฟ

อุปกรณ์ตรวจจับอัคคีภัยและความปลอดภัยเช่นสัญญาณเตือนไฟไหม้

อุปกรณ์วัดเช่นโวลต์มิเตอร์

ไมโครคอนโทรลเลอร์ 8051 ได้รับการออกแบบโดย Intel ในปี 1981 เป็นไมโครคอนโทรลเลอร์ 8 บิต มันถูกสร้างขึ้นด้วย DIP 40 พิน (แพ็คเกจอินไลน์คู่), ที่เก็บ ROM 4kb และที่เก็บแรม 128 ไบต์, ตัวจับเวลา 16 บิต 2 ตัว ประกอบด้วยพอร์ต 8 บิตแบบขนานสี่พอร์ตซึ่งสามารถตั้งโปรแกรมและกำหนดแอดเดรสได้ตามความต้องการ ออสซิลเลเตอร์คริสตัลบนชิปรวมอยู่ในไมโครคอนโทรลเลอร์ที่มีความถี่คริสตัล 12 MHz

ตอนนี้ให้เราพูดถึงสถาปัตยกรรมของไมโครคอนโทรลเลอร์ 8051

ในแผนภาพต่อไปนี้บัสระบบจะเชื่อมต่ออุปกรณ์สนับสนุนทั้งหมดกับ CPU บัสระบบประกอบด้วยบัสข้อมูล 8 บิตบัสแอดเดรส 16 บิตและสัญญาณควบคุมบัส อุปกรณ์อื่น ๆ ทั้งหมดเช่นหน่วยความจำโปรแกรมพอร์ตหน่วยความจำข้อมูลอินเทอร์เฟซแบบอนุกรมการควบคุมการขัดจังหวะตัวจับเวลาและ CPU ทั้งหมดเชื่อมต่อกันผ่านบัสระบบ

แผนภาพพินของไมโครคอนโทรลเลอร์ 8051 มีลักษณะดังนี้ -

Pins 1 to 8- พินเหล่านี้เรียกว่าพอร์ต 1 พอร์ตนี้ไม่ทำหน้าที่อื่นใด มันถูกดึงขึ้นภายในพอร์ต I / O แบบสองทิศทาง

Pin 9 - เป็นพิน RESET ซึ่งใช้เพื่อรีเซ็ตไมโครคอนโทรลเลอร์เป็นค่าเริ่มต้น

Pins 10 to 17 - หมุดเหล่านี้เรียกว่าพอร์ต 3 พอร์ตนี้ทำหน้าที่บางอย่างเช่นอินเทอร์รัปต์อินพุตตัวจับเวลาสัญญาณควบคุมสัญญาณสื่อสารแบบอนุกรม RxD และ TxD เป็นต้น

Pins 18 & 19 - หมุดเหล่านี้ใช้สำหรับเชื่อมต่อกับคริสตัลภายนอกเพื่อรับนาฬิการะบบ

Pin 20 - พินนี้จ่ายไฟให้กับวงจร

Pins 21 to 28- หมุดเหล่านี้เรียกว่าพอร์ต 2 ทำหน้าที่เป็นพอร์ต I / O สัญญาณบัสที่อยู่คำสั่งซื้อที่สูงขึ้นจะถูกมัลติเพล็กซ์โดยใช้พอร์ตนี้

Pin 29- นี่คือพิน PSEN ซึ่งย่อมาจาก Program Store Enable ใช้เพื่ออ่านสัญญาณจากหน่วยความจำโปรแกรมภายนอก

Pin 30- นี่คือขา EA ซึ่งย่อมาจากอินพุตการเข้าถึงภายนอก ใช้เพื่อเปิด / ปิดการเชื่อมต่อหน่วยความจำภายนอก

Pin 31- นี่คือพิน ALE ซึ่งย่อมาจาก Address Latch Enable ใช้เพื่อแยกสัญญาณแอดเดรส - ข้อมูลของพอร์ต

Pins 32 to 39- หมุดเหล่านี้เรียกว่าพอร์ต 0 ทำหน้าที่เป็นพอร์ต I / O ที่อยู่ลำดับล่างและสัญญาณบัสข้อมูลจะถูกมัลติเพล็กซ์โดยใช้พอร์ตนี้

Pin 40 - พินนี้ใช้เพื่อจ่ายไฟให้กับวงจร

ไมโครคอนโทรลเลอร์ 8051 มีพอร์ต I / O 4 พอร์ตแต่ละพอร์ตเป็น 8 บิตซึ่งสามารถกำหนดค่าเป็นอินพุตหรือเอาต์พุตได้ ดังนั้นขาอินพุต / เอาต์พุตทั้งหมด 32 พินจึงอนุญาตให้ไมโครคอนโทรลเลอร์เชื่อมต่อกับอุปกรณ์ต่อพ่วง

Pin configurationกล่าวคือสามารถกำหนดค่าพินเป็น 1 สำหรับอินพุตและ 0 สำหรับเอาต์พุตตามสถานะลอจิก

Input/Output (I/O) pin - วงจรทั้งหมดภายในไมโครคอนโทรลเลอร์ต้องเชื่อมต่อกับพินตัวใดตัวหนึ่งยกเว้นพอร์ต P0 เนื่องจากไม่มีตัวต้านทานแบบดึงขึ้นในตัว

Input pin- Logic 1 ถูกนำไปใช้กับบิตของรีจิสเตอร์ ทรานซิสเตอร์เอาท์พุท FE ถูกปิดและพินอีกตัวยังคงเชื่อมต่อกับแรงดันไฟฟ้าของแหล่งจ่ายไฟเหนือตัวต้านทานแบบดึงขึ้นที่มีความต้านทานสูง

Port 0 - พอร์ต P0 (ศูนย์) มีสองฟังก์ชัน -

เมื่อใช้หน่วยความจำภายนอกจะใช้ไบต์แอดเดรสด้านล่าง (แอดเดรส A0A7) มิฉะนั้นบิตทั้งหมดของพอร์ตนี้จะถูกกำหนดค่าเป็นอินพุต / เอาต์พุต

เมื่อกำหนดค่าพอร์ต P0 เป็นเอาต์พุตพอร์ตอื่น ๆ ที่ประกอบด้วยพินที่มีตัวต้านทานแบบดึงขึ้นในตัวที่เชื่อมต่อโดยปลายถึงแหล่งจ่ายไฟ 5V พินของพอร์ตนี้จะมีตัวต้านทานนี้ทิ้งไว้

การกำหนดค่าอินพุต

หากพินใด ๆ ของพอร์ตนี้ถูกกำหนดค่าเป็นอินพุตมันจะทำหน้าที่ราวกับว่ามัน "ลอย" นั่นคืออินพุตมีความต้านทานอินพุตไม่ จำกัด และมีศักยภาพในการกำหนด

การกำหนดค่าเอาต์พุต

เมื่อกำหนดค่าพินเป็นเอาต์พุตแล้วจะทำหน้าที่เป็น "ท่อระบายน้ำเปิด" เมื่อใช้ลอจิก 0 กับพอร์ตบิตพินที่เหมาะสมจะเชื่อมต่อกับกราวด์ (0V) และใช้ลอจิก 1 เอาต์พุตภายนอกจะยังคง "ลอย"

ในการใช้ลอจิก 1 (5V) กับพินเอาต์พุตนี้จำเป็นต้องสร้างตัวต้านทานแบบพูลอัพภายนอก

พอร์ต 1

P1 เป็นพอร์ต I / O ที่แท้จริงเนื่องจากไม่มีฟังก์ชันอื่น ๆ เช่นเดียวกับใน P0 แต่พอร์ตนี้สามารถกำหนดค่าเป็น I / O ทั่วไปเท่านั้น มีตัวต้านทานแบบดึงขึ้นในตัวและเข้ากันได้กับวงจร TTL อย่างสมบูรณ์

พอร์ต 2

P2 คล้ายกับ P0 เมื่อใช้หน่วยความจำภายนอก พินของพอร์ตนี้ใช้แอดเดรสที่มีไว้สำหรับชิปหน่วยความจำภายนอก พอร์ตนี้สามารถใช้สำหรับไบต์แอดเดรสที่สูงขึ้นด้วยแอดเดรส A8-A15 เมื่อไม่มีการเพิ่มหน่วยความจำพอร์ตนี้สามารถใช้เป็นพอร์ตอินพุต / เอาต์พุตทั่วไปคล้ายกับพอร์ต 1

พอร์ต 3

ในพอร์ตนี้ฟังก์ชันจะคล้ายกับพอร์ตอื่น ๆ ยกเว้นว่าต้องใช้ตรรกะ 1 กับบิตของรีจิสเตอร์ P3 ที่เหมาะสม

พินข้อ จำกัด ปัจจุบัน

เมื่อพินถูกกำหนดค่าเป็นเอาต์พุต (เช่นลอจิก 0) พินพอร์ตเดียวจะสามารถรับกระแส 10mA ได้

เมื่อพินเหล่านี้ได้รับการกำหนดค่าเป็นอินพุต (เช่นลอจิก 1) ตัวต้านทานแบบดึงขึ้นในตัวจะให้กระแสไฟอ่อนมาก แต่สามารถเปิดใช้งานอินพุต TTL ได้สูงสุด 4 ชุดของ LS

หากพอร์ตทั้งหมด 8 บิตทำงานอยู่กระแสรวมต้อง จำกัด ไว้ที่ 15mA (พอร์ต P0: 26mA)

หากพอร์ตทั้งหมด (32 บิต) ทำงานอยู่กระแสไฟฟ้าสูงสุดทั้งหมดจะต้อง จำกัด ไว้ที่ 71mA

การขัดจังหวะคือเหตุการณ์ที่หยุดโปรแกรมหลักชั่วคราวส่งผ่านการควบคุมไปยังแหล่งภายนอกและดำเนินการตามภารกิจ จากนั้นจะส่งการควบคุมไปยังโปรแกรมหลักที่ค้างไว้

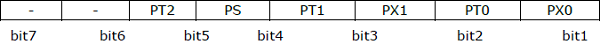

8051 มีสัญญาณขัดจังหวะ 5 รายการ ได้แก่ INT0, TFO, INT1, TF1, RI / TI การขัดจังหวะแต่ละครั้งสามารถเปิดหรือปิดใช้งานได้โดยการตั้งค่าบิตของรีจิสเตอร์ IE และระบบขัดจังหวะทั้งหมดสามารถปิดใช้งานได้โดยการล้างบิต EA ของรีจิสเตอร์เดียวกัน

IE (Interrupt Enable) ลงทะเบียน

รีจิสเตอร์นี้มีหน้าที่ในการเปิดใช้งานและปิดใช้งานการขัดจังหวะ การลงทะเบียน EA ถูกตั้งค่าเป็นหนึ่งสำหรับเปิดใช้งานการขัดจังหวะและตั้งค่าเป็น 0 เพื่อปิดใช้งานการขัดจังหวะ ลำดับบิตและความหมายแสดงในรูปต่อไปนี้

| EA | IE 7 | มันปิดการขัดจังหวะทั้งหมด เมื่อ EA = 0 ไม่มีการขัดจังหวะจะรับทราบและ EA = 1 เปิดใช้งานการขัดจังหวะทีละรายการ |

| - | IE 6 | สงวนไว้สำหรับใช้ในอนาคต |

| - | IE 5 | สงวนไว้สำหรับใช้ในอนาคต |

| ES | IE 4 | เปิด / ปิดการขัดจังหวะพอร์ตอนุกรม |

| ET1 | IE 3 | เปิด / ปิดการใช้งานการขัดจังหวะ Timer1 over |

| EX1 | IE 2 | เปิด / ปิดการขัดจังหวะภายนอก 1. |

| ET0 | IE1 | เปิด / ปิดการใช้งานการขัดจังหวะการโอเวอร์โฟลของ timer0 |

| EX0 | IE.0 | เปิด / ปิดการขัดจังหวะภายนอก 0 |

IP (Interrupt Priority) ลงทะเบียน

เราสามารถเปลี่ยนระดับความสำคัญของการขัดจังหวะได้โดยการเปลี่ยนบิตที่เกี่ยวข้องในการลงทะเบียน Interrupt Priority (IP) ดังแสดงในรูปต่อไปนี้

การขัดจังหวะที่มีลำดับความสำคัญต่ำสามารถถูกขัดจังหวะได้โดยการขัดจังหวะที่มีลำดับความสำคัญสูงเท่านั้น แต่จะไม่ถูกขัดจังหวะด้วยการขัดจังหวะที่มีลำดับความสำคัญต่ำอื่น

หากได้รับการขัดจังหวะสองระดับที่มีลำดับความสำคัญต่างกันพร้อมกันระบบจะให้บริการคำขอของระดับความสำคัญสูง

หากได้รับคำร้องขอที่มีระดับความสำคัญเดียวกันพร้อมกันลำดับการสำรวจภายในจะเป็นตัวกำหนดว่าจะให้บริการคำขอใด

| - | IP.6 | สงวนไว้สำหรับใช้ในอนาคต |

| - | IP 5 | สงวนไว้สำหรับใช้ในอนาคต |

| ปล | IP.4 | เป็นการกำหนดระดับความสำคัญของการขัดจังหวะพอร์ตอนุกรม |

| PT1 | IP.3 | เป็นการกำหนดการขัดจังหวะตัวจับเวลา 1 ลำดับความสำคัญ |

| PX1 | IP.2 | เป็นการกำหนดระดับความสำคัญของการขัดจังหวะภายนอก |

| PT0 | IP.1 | เป็นการกำหนดระดับลำดับความสำคัญของการขัดจังหวะ timer0 |

| PX0 | IP.0 | เป็นการกำหนดการขัดจังหวะภายนอกของระดับความสำคัญ 0 |

ลงทะเบียน TCON

TCON register ระบุประเภทของอินเทอร์รัปต์ภายนอกให้กับไมโครคอนโทรลเลอร์

8255A เป็นอุปกรณ์ I / O ที่ตั้งโปรแกรมได้โดยทั่วไปซึ่งออกแบบมาเพื่อถ่ายโอนข้อมูลจาก I / O เพื่อขัดจังหวะ I / O ภายใต้เงื่อนไขบางประการตามที่กำหนด สามารถใช้ได้กับไมโครโปรเซสเซอร์เกือบทุกชนิด

ประกอบด้วยพอร์ต I / O แบบสองทิศทาง 8 บิตสามพอร์ต (สาย 24I / O) ซึ่งสามารถกำหนดค่าได้ตามความต้องการ

พอร์ตของ 8255A

8255A มีพอร์ตสามพอร์ต ได้แก่ พอร์ต A พอร์ต B และพอร์ต C

Port A มีสลัก / บัฟเฟอร์เอาต์พุต 8 บิตหนึ่งชุดและบัฟเฟอร์อินพุต 8 บิตหนึ่งชุด

Port B คล้ายกับ PORT A

Port C สามารถแบ่งออกเป็นสองส่วน ได้แก่ PORT C lower (PC0-PC3) และ PORT C upper (PC7-PC4) โดยใช้คำควบคุม

พอร์ตทั้งสามนี้แบ่งออกเป็นสองกลุ่ม ได้แก่ กลุ่ม A ประกอบด้วยพอร์ต A และพอร์ตบนบนกลุ่ม B ได้แก่ พอร์ต B และพอร์ตซีที่ต่ำกว่าทั้งสองกลุ่มนี้สามารถตั้งโปรแกรมได้ในโหมดที่แตกต่างกันสามโหมดกล่าวคือโหมดแรกตั้งชื่อเป็นโหมด 0 โหมดที่สองถูกตั้งชื่อเป็นโหมด 1 และโหมดที่สามถูกตั้งชื่อเป็นโหมด 2

โหมดการทำงาน

8255A มีโหมดการทำงานที่แตกต่างกันสามโหมด -

Mode 0- ในโหมดนี้พอร์ต A และ B ใช้เป็นพอร์ต 8 บิตสองพอร์ตและพอร์ต C เป็นพอร์ต 4 บิตสองพอร์ต แต่ละพอร์ตสามารถตั้งโปรแกรมได้ทั้งในโหมดอินพุตหรือโหมดเอาต์พุตโดยที่เอาต์พุตถูกล็อคและอินพุตไม่ได้ล็อก พอร์ตไม่มีความสามารถในการขัดจังหวะ

Mode 1- ในโหมดนี้พอร์ต A และ B จะใช้เป็นพอร์ต I / O 8 บิต สามารถกำหนดค่าเป็นพอร์ตอินพุตหรือเอาต์พุตได้ แต่ละพอร์ตใช้สามเส้นจากพอร์ต C เป็นสัญญาณจับมือ อินพุตและเอาต์พุตถูกสลัก

Mode 2- ในโหมดนี้สามารถกำหนดค่าพอร์ต A เป็นพอร์ตสองทิศทางและพอร์ต B ได้ทั้งในโหมด 0 หรือโหมด 1 พอร์ต A ใช้สัญญาณห้าสัญญาณจากพอร์ต C เป็นสัญญาณจับมือสำหรับการถ่ายโอนข้อมูล สัญญาณสามสัญญาณที่เหลือจากพอร์ต C สามารถใช้เป็น I / O แบบธรรมดาหรือแบบแฮนด์เชคสำหรับพอร์ต B

คุณสมบัติของ 8255A

คุณสมบัติเด่นของ 8255A มีดังต่อไปนี้ -

ประกอบด้วยพอร์ต IO 8 บิต 3 พอร์ต ได้แก่ PA, PB และ PC

แอดเดรส / บัสข้อมูลต้อง demux จากภายนอก

เข้ากันได้กับ TTL

มีการปรับปรุงความสามารถในการขับ DC

8255 สถาปัตยกรรม

รูปต่อไปนี้แสดงสถาปัตยกรรมของ 8255A -

ก่อนอื่นเรามาดูพินไดอะแกรมของ Intel 8255A -

ตอนนี้ให้เราพูดถึงคำอธิบายการทำงานของหมุดใน 8255A

บัฟเฟอร์บัสข้อมูล

เป็นบัฟเฟอร์ 8 บิตแบบไตรสถานะซึ่งใช้เพื่อเชื่อมต่อไมโครโปรเซสเซอร์กับบัสข้อมูลระบบ ข้อมูลถูกส่งหรือรับโดยบัฟเฟอร์ตามคำแนะนำของ CPU คำควบคุมและข้อมูลสถานะจะถูกโอนโดยใช้บัสนี้ด้วย

อ่าน / เขียนลอจิกการควบคุม

บล็อกนี้มีหน้าที่ควบคุมการถ่ายโอนข้อมูล / คำควบคุม / สถานะภายใน / ภายนอก รับอินพุตจากที่อยู่ CPU และบัสควบคุมและในทางกลับกันปัญหาคำสั่งไปยังทั้งสองกลุ่มควบคุม

CS

ย่อมาจาก Chip Select อินพุตนี้ต่ำจะเลือกชิปและเปิดใช้งานการสื่อสารระหว่าง 8255A และ CPU เชื่อมต่อกับแอดเดรสที่ถอดรหัสและ A 0 & A 1เชื่อมต่อกับบรรทัดแอดเดรสของไมโครโปรเซสเซอร์

ผลลัพธ์ขึ้นอยู่กับเงื่อนไขต่อไปนี้ -

| CS | ก1 | ก0 | ผลลัพธ์ |

|---|---|---|---|

| 0 | 0 | 0 | พอร์ต A |

| 0 | 0 | 1 | พอร์ตข |