Mạch tuần tự

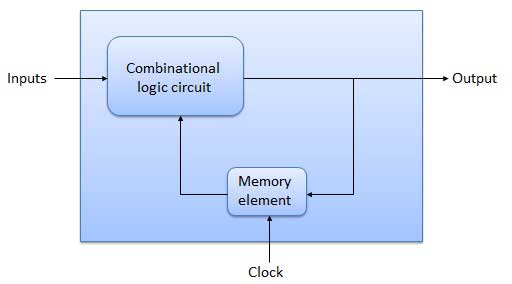

Mạch tổ hợp không sử dụng bộ nhớ nào. Do đó trạng thái trước đó của đầu vào không có bất kỳ ảnh hưởng nào đến trạng thái hiện tại của mạch. Nhưng mạch tuần tự có bộ nhớ nên đầu ra có thể thay đổi tùy theo đầu vào. Loại mạch này sử dụng đầu vào, đầu ra, đồng hồ trước đó và một phần tử bộ nhớ.

Sơ đồ khối

Dep Lê

Flip flop là một mạch tuần tự thường lấy mẫu đầu vào của nó và thay đổi đầu ra của nó chỉ ở những thời điểm cụ thể và không liên tục. Flip flop được cho là nhạy cảm với cạnh hoặc cạnh được kích hoạt hơn là được kích hoạt ở mức như chốt.

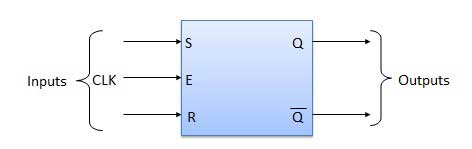

SR Flip Flop

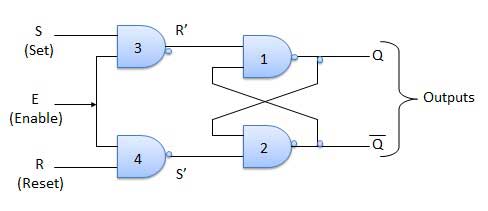

Về cơ bản nó là chốt SR sử dụng cổng NAND với một enableđầu vào. Nó còn được gọi là SR-FF được kích hoạt mức. Đối với điều này, mạch ở đầu ra sẽ diễn ra nếu và chỉ khi đầu vào cho phép (E) được kích hoạt. Trong ngắn hạn mạch này sẽ hoạt động như một chốt SR nếu E = 1 nhưng không có sự thay đổi ở đầu ra nếu E = 0.

Sơ đồ khối

Sơ đồ mạch

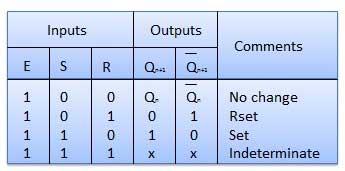

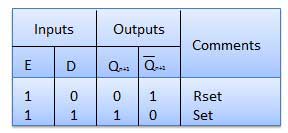

Bảng sự thật

Hoạt động

| SN | Tình trạng | Hoạt động |

|---|---|---|

| 1 | S = R = 0 : No change |

Nếu S = R = 0 thì đầu ra của cổng NAND 3 và 4 buộc phải trở thành 1. Do đó cả hai R 'và S' sẽ bằng 1. Vì S 'và R' là đầu vào của chốt SR cơ bản sử dụng cổng NAND nên sẽ không có sự thay đổi về trạng thái của đầu ra. |

| 2 | S = 0, R = 1, E = 1 |

Vì S = 0, đầu ra của NAND-3 tức là R '= 1 và E = 1, đầu ra của NAND-4 tức là S' = 0. Do đó Q n + 1 = 0 và Q n + 1 bar = 1. Đây là điều kiện đặt lại. |

| 3 | S = 1, R = 0, E = 1 |

Đầu ra của NAND-3 tức là R '= 0 và đầu ra của NAND-4 tức là S' = 1. Do đó đầu ra của chốt SR NAND là Q n + 1 = 1 và Q n + 1 bar = 0. Đây là điều kiện đặt lại. |

| 4 | S = 1, R = 1, E = 1 |

Vì S = 1, R = 1 và E = 1, đầu ra của cổng NAND 3 và 4 đều bằng 0 tức là S '= R' = 0. Vì thế Race điều kiện sẽ xảy ra trong chốt NAND cơ bản. |

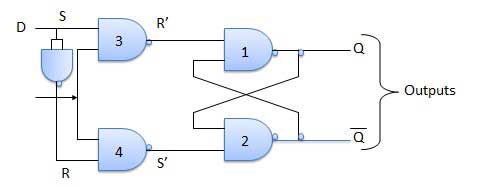

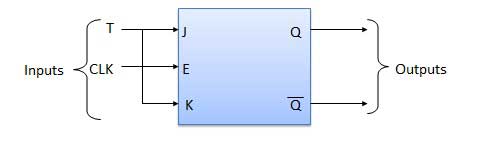

Master Slave JK Flip Flop

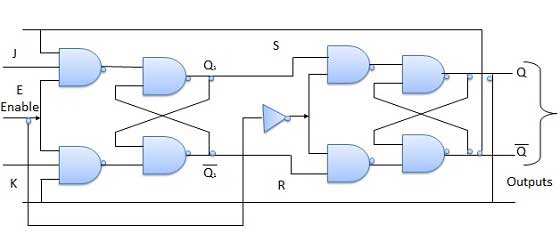

Master slave JK FF là một tầng gồm hai SR FF với phản hồi từ đầu ra của thứ hai đến đầu vào của thứ nhất. Master là một mức tích cực được kích hoạt. Nhưng do sự hiện diện của bộ nghịch lưu trong dòng xung nhịp, bộ phận phụ sẽ đáp ứng ở mức âm. Do đó khi xung nhịp = 1 (mức tích cực) thì master hoạt động và slave không hoạt động. Trong khi đó khi clock = 0 (mức thấp) thì slave hoạt động và master không hoạt động.

Sơ đồ mạch

Bảng sự thật

Hoạt động

| SN | Tình trạng | Hoạt động |

|---|---|---|

| 1 | J = K = 0 (No change) |

Khi đồng hồ = 0, phụ sẽ hoạt động và chủ không hoạt động. Nhưng vì các đầu vào S và R không thay đổi, nên các đầu ra phụ cũng sẽ không thay đổi. Do đó đầu ra sẽ không thay đổi nếu J = K = 0. |

| 2 | J = 0 and K = 1 (Reset) |

Đồng hồ = 1 - Chính hoạt động, phụ không hoạt động. Do đó đầu ra của tổng trở thành Q 1 = 0 và Q 1 bar = 1. Điều đó có nghĩa là S = 0 và R = 1. Đồng hồ = 0 - Nô lệ hoạt động, chủ không hoạt động. Do đó đầu ra của phụ trở thành Q = 0 và Q bar = 1. Một lần nữa clock = 1 - Master hoạt động, slave không hoạt động. Do đó, ngay cả khi các đầu ra thay đổi Q = 0 và Q bar = 1 được đưa trở lại master, đầu ra của nó sẽ là Q1 = 0 và Q1 bar = 1. Điều đó có nghĩa là S = 0 và R = 1. Do đó với clock = 0 và slave trở nên hoạt động, các đầu ra của slave sẽ vẫn là Q = 0 và Q bar = 1. Do đó, chúng ta nhận được một đầu ra ổn định từ Master slave. |

| 3 | J = 1 and K = 0 (Set) |

Đồng hồ = 1 - Chính hoạt động, phụ không hoạt động. Do đó đầu ra của tổng trở thành Q 1 = 1 và Q 1 bar = 0. Điều đó có nghĩa là S = 1 và R = 0. Đồng hồ = 0 - Nô lệ hoạt động, chủ không hoạt động. Do đó đầu ra của phụ trở thành Q = 1 và thanh Q = 0. Một lần nữa clock = 1 - sau đó có thể chỉ ra rằng các đầu ra của phụ được ổn định thành Q = 1 và Q bar = 0. |

| 4 | J = K = 1 (Toggle) |

Đồng hồ = 1 - Chính hoạt động, phụ không hoạt động. Đầu ra của tổng thể sẽ chuyển đổi. Vì vậy, S và R cũng sẽ đảo ngược. Đồng hồ = 0 - Nô lệ hoạt động, chủ không hoạt động. Đầu ra của nô lệ sẽ chuyển đổi. Các đầu ra đã thay đổi này được trả lại cho các đầu vào chính. Nhưng vì clock = 0, master vẫn không hoạt động. Vì vậy, nó không phản hồi với những đầu ra thay đổi này. Điều này tránh việc chuyển đổi nhiều lần dẫn đến tình trạng chạy đua xung quanh. Cú lật ngược của nô lệ chủ sẽ tránh được tình trạng chạy đua xung quanh. |

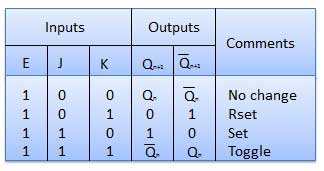

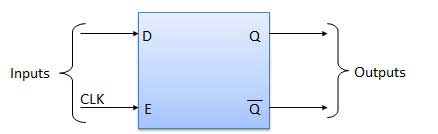

Delay Flip Flop / D Flip Flop

Delay Flip Flop hay D Flip Flop là chốt SR đơn giản với bộ biến tần NAND được kết nối giữa đầu vào S và R. Nó chỉ có một đầu vào. Dữ liệu đầu vào sẽ xuất hiện ở đầu ra sau một thời gian. Do độ trễ dữ liệu này giữa i / p và o / p, nó được gọi là flip flop trễ. S và R sẽ bổ sung cho nhau do biến tần NAND. Do đó S = R = 0 hoặc S = R = 1, các điều kiện đầu vào này sẽ không bao giờ xuất hiện. Vấn đề này được tránh bằng điều kiện SR = 00 và SR = 1.

Sơ đồ khối

Sơ đồ mạch

Bảng sự thật

Hoạt động

| SN | Tình trạng | Hoạt động |

|---|---|---|

| 1 | E = 0 |

Chốt bị tắt. Do đó không có thay đổi về sản lượng. |

| 2 | E = 1 and D = 0 |

Nếu E = 1 và D = 0 thì S = 0 và R = 1. Do đó bất kể trạng thái hiện tại, trạng thái tiếp theo là Q n + 1 = 0 và Q n + 1 bar = 1. Đây là điều kiện đặt lại. |

| 3 | E = 1 and D = 1 |

Nếu E = 1 và D = 1, thì S = 1 và R = 0. Điều này sẽ đặt chốt và Q n + 1 = 1 và Q n + 1 bar = 0 bất kể trạng thái hiện tại. |

Chuyển đổi Flip Flop / T Flip Flop

Toggle flip flop về cơ bản là một flip flop JK với các thiết bị đầu cuối J và K được kết nối vĩnh viễn với nhau. Nó chỉ có đầu vào được biểu thị bằngTnhư được hiển thị trong Sơ đồ ký hiệu. Biểu tượng cho flip flop được kích hoạt cạnh tích cực T được hiển thị trong Sơ đồ khối.

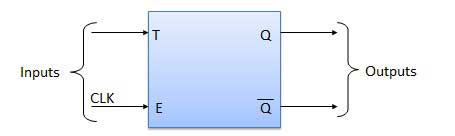

Sơ đồ ký hiệu

Sơ đồ khối

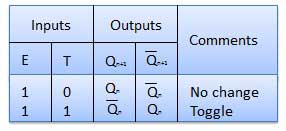

Bảng sự thật

Hoạt động

| SN | Tình trạng | Hoạt động |

|---|---|---|

| 1 | T = 0, J = K = 0 | Đầu ra Q và thanh Q sẽ không thay đổi |

| 2 | T = 1, J = K = 1 | Đầu ra sẽ chuyển đổi tương ứng với mọi cạnh hàng đầu của tín hiệu đồng hồ. |