ADCs vom direkten Typ

Ein Analog-Digital-Wandler (ADC)wandelt ein analoges Signal in ein digitales Signal um. Das digitale Signal wird mit einem Binärcode dargestellt, der eine Kombination der Bits 0 und 1 ist.

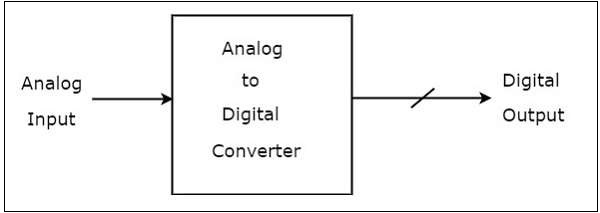

Das block diagram eines ADC ist in der folgenden Abbildung dargestellt -

Beachten Sie, dass in der Abbildung oben ein Analog-Digital-Wandler dargestellt ist (ADC)besteht aus einem einzelnen Analogeingang und vielen Binärausgängen. Im Allgemeinen beträgt die Anzahl der Binärausgänge des ADC eine Zweierpotenz.

Es gibt two typesvon ADCs: ADCs vom direkten Typ und ADC vom indirekten Typ. In diesem Kapitel werden die ADCs vom Typ Direct ausführlich beschrieben.

Wenn der ADC die Analog-Digital-Wandlung direkt durch Verwendung des intern erzeugten äquivalenten digitalen (Binär-) Codes zum Vergleich mit dem analogen Eingang durchführt, wird dies als bezeichnet Direct type ADC.

Das Folgende sind die examples von ADCs vom direkten Typ -

- Zählertyp ADC

- ADC mit sukzessiver Approximation

- Flash-Typ ADC

In diesem Abschnitt werden diese ADCs vom Typ Direct ausführlich beschrieben.

Zählertyp ADC

EIN counter type ADC erzeugt einen digitalen Ausgang, der ungefähr dem analogen Eingang entspricht, indem der Zählerbetrieb intern verwendet wird.

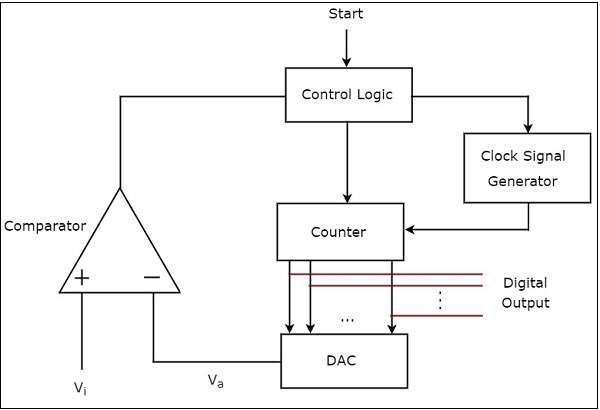

Das block diagram eines Zählertyps ADC ist in der folgenden Abbildung dargestellt -

Der Zählertyp ADC besteht hauptsächlich aus 5 Blöcken: Taktsignalgenerator, Zähler, DAC, Komparator und Steuerlogik.

Das working eines Zählertyp-ADC ist wie folgt -

Das control logic setzt den Zähler zurück und aktiviert den Taktsignalgenerator, um die Taktimpulse an den Zähler zu senden, wenn er das Startbefehlssignal empfangen hat.

Das counterwird für jeden Takt um eins erhöht und sein Wert wird im binären (digitalen) Format vorliegen. Dieser Ausgang des Zählers wird als Eingang des DAC angelegt.

DACwandelt den empfangenen binären (digitalen) Eingang, der der Ausgang des Zählers ist, in einen analogen Ausgang um. Der Komparator vergleicht diesen analogen Wert $ V_ {a} $ mit dem externen analogen Eingangswert $ V_ {i} $.

Das output of comparator wird sein ‘1’solange größer ist als. Die in den beiden obigen Schritten erwähnten Operationen werden fortgesetzt, solange die Steuerlogik '1' vom Ausgang des Komparators empfängt.

Das output of comparator wird sein ‘0’wenn $ V_ {i} $ kleiner oder gleich $ V_ {a} $ ist. Die Steuerlogik empfängt also '0' vom Ausgang des Komparators. Dann deaktiviert die Steuerlogik den Taktsignalgenerator, so dass er keinen Taktimpuls an den Zähler sendet.

In diesem Moment wird die Ausgabe des Zählers als angezeigt digital output. Es entspricht fast dem entsprechenden externen Analogeingangswert $ V_ {i} $.

ADC mit sukzessiver Approximation

EIN successive approximation type ADC erzeugt einen digitalen Ausgang, der ungefähr gleich dem analogen Eingang ist, indem intern eine sukzessive Approximationstechnik verwendet wird.

Das block diagram Ein ADC mit sukzessiver Approximation ist in der folgenden Abbildung dargestellt

Der ADC mit sukzessiver Approximation besteht hauptsächlich aus 5 Blöcken - Taktsignalgenerator, SAR (Successive Approximation Register), DAC, Komparator und Steuerlogik.

Das working einer sukzessiven Approximation ADC ist wie folgt -

Das control logic Setzt alle Bits von SAR zurück und aktiviert den Taktsignalgenerator, um die Taktimpulse an SAR zu senden, wenn er das Startbefehlssignal empfangen hat.

Die binären (digitalen) Daten in SARwird für jeden Taktimpuls basierend auf dem Ausgang des Komparators aktualisiert. Die Ausgabe von SAR wird als Eingabe von DAC angewendet.

DAC wandelt den empfangenen digitalen Eingang, der der Ausgang von SAR ist, in einen analogen Ausgang um. Der Komparator vergleicht diesen Analogwert $ V_ {a} $ mit dem externen Analogeingangswert $ V_ {i} $.

Das output of a comparatorwird '1' sein, solange $ V_ {i} $ größer als $ V_ {a} $ ist. In ähnlicher Weise ist die Ausgabe des Komparators '0', wenn $ V_ {i} $ kleiner oder gleich $ V_ {a} $ ist.

Die in den obigen Schritten genannten Vorgänge werden fortgesetzt, bis der digitale Ausgang gültig ist.

Der digitale Ausgang ist gültig, wenn er fast dem entsprechenden externen analogen Eingangswert $ V_ {i} $ entspricht.

Flash-Typ ADC

EIN flash type ADCerzeugt in kürzester Zeit einen äquivalenten digitalen Ausgang für einen entsprechenden analogen Eingang. Daher ist der Flash-ADC der schnellste ADC.

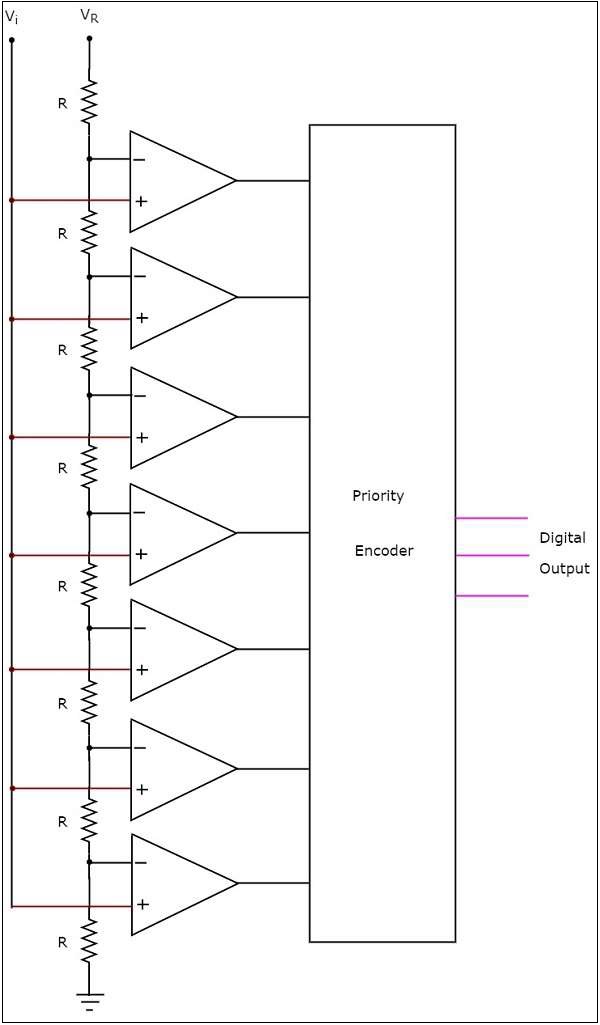

Das circuit diagram eines 3-Bit-Flash-ADC ist in der folgenden Abbildung dargestellt:

Der 3-Bit-Flash-ADC besteht aus einem Spannungsteilernetzwerk, 7 Komparatoren und einem Prioritätscodierer.

Das working eines 3-Bit-Flash-ADC ist wie folgt.

Das voltage divider networkenthält 8 gleiche Widerstände. Eine Referenzspannung $ V_ {R} $ wird über das gesamte Netzwerk in Bezug auf die Erde angelegt. Der Spannungsabfall an jedem Widerstand von unten nach oben in Bezug auf Masse ist das ganzzahlige Vielfache (von 1 bis 8) von $ \ frac {V_ {R}} {8} $.

Das Äußere input voltage$ V_ {i} $ wird auf das nicht invertierende Terminal aller Komparatoren angewendet. Der Spannungsabfall an jedem Widerstand von unten nach oben in Bezug auf Masse wird von unten nach oben an den invertierenden Anschluss der Komparatoren angelegt.

Alle Komparatoren vergleichen jeweils die externe Eingangsspannung mit den Spannungsabfällen am jeweiligen anderen Eingangsanschluss. Das heißt, die Vergleichsoperationen finden von jedem Komparator stattparallelly.

Das output of the comparatorwird '1' sein, solange $ V_ {i} $ größer ist als der am jeweiligen anderen Eingangsanschluss anliegende Spannungsabfall. In ähnlicher Weise ist der Ausgang des Komparators '0', wenn $ V_ {i} $ kleiner oder gleich dem Spannungsabfall ist, der an dem jeweiligen anderen Eingangsanschluss vorhanden ist.

Alle Ausgänge der Komparatoren sind als Eingänge von verbunden priority encoderDieser Prioritätscodierer erzeugt einen Binärcode (digitaler Ausgang), der dem Eingang mit hoher Priorität entspricht, der '1' hat.

Daher ist der Ausgang des Prioritätscodierers nichts anderes als das binäre Äquivalent (digital output) der externen analogen Eingangsspannung $ V_ {i} $.

Der Flash-ADC wird in Anwendungen verwendet, in denen die Umwandlungsgeschwindigkeit des analogen Eingangs in digitale Daten sehr hoch sein sollte.