Phasenregelkreis-IC

Phasenregelkreis (PLL)ist einer der wichtigsten Blöcke in linearen Systemen. Es ist nützlich in Kommunikationssystemen wie Radar, Satelliten, FMs usw.

In diesem Kapitel wird das Blockdiagramm von PLL und IC 565 ausführlich erläutert.

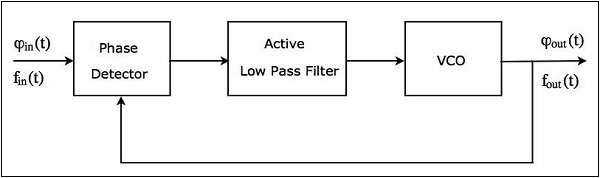

Blockdiagramm der PLL

Ein Phase Locked Loop (PLL) besteht hauptsächlich aus Folgendem three blocks - -

- Phasendetektor

- Aktiver Tiefpassfilter

- Spannungsgesteuerter Oszillator (VCO)

Das block diagram von PLL ist in der folgenden Abbildung dargestellt -

Der Ausgang eines Phasendetektors wird als Eingang eines aktiven Tiefpassfilters angelegt. In ähnlicher Weise wird der Ausgang des aktiven Tiefpassfilters als Eingang des VCO angelegt.

Das working einer PLL ist wie folgt -

Phase detector erzeugt eine Gleichspannung, die proportional zur Phasendifferenz zwischen dem Eingangssignal mit einer Frequenz von $ f_ {in} $ und dem Rückkopplungssignal (Ausgangssignal) mit einer Frequenz von $ f_ {out} $ ist.

EIN Phase detector ist ein Multiplikator und erzeugt an seinem Ausgang zwei Frequenzkomponenten - die Summe der Frequenzen $ f_ {in} $ und $ f_ {out} $ und die Differenz der Frequenzen $ f_ {in} $ & $ f_ {out} $.

Ein active low pass filtererzeugt an seinem Ausgang eine Gleichspannung, nachdem die im Ausgang des Phasendetektors vorhandene Hochfrequenzkomponente beseitigt wurde. Es verstärkt auch das Signal.

EIN VCOerzeugt ein Signal mit einer bestimmten Frequenz, wenn kein Eingang angelegt wird. Diese Frequenz kann durch Anlegen einer Gleichspannung an beide Seiten verschoben werden. Daher ist die Frequenzabweichung direkt proportional zur Gleichspannung, die am Ausgang eines Tiefpassfilters anliegt.

Die obigen Operationen finden statt, bis die VCO-Frequenz gleich der Eingangssignalfrequenz ist. Abhängig von der Art der Anwendung können wir entweder den Ausgang eines aktiven Tiefpassfilters oder den Ausgang eines VCO verwenden. PLLs werden in vielen verwendetapplications wie FM-Demodulator, Taktgenerator usw.

PLL arbeitet in einem der following three modes - -

- Freilaufmodus

- Aufnahmemodus

- Verriegelter Zustand

Zunächst arbeitet PLL in free running modewenn keine Eingabe darauf angewendet wird. Wenn ein Eingangssignal mit einer bestimmten Frequenz an PLL angelegt wird, beginnt sich die Ausgangssignalfrequenz von VCO zu ändern. Zu diesem Zeitpunkt soll die PLL in dercapture mode. Die Ausgangssignalfrequenz von VCO ändert sich kontinuierlich, bis sie der Eingangssignalfrequenz entspricht. Jetzt soll es PLL sein, das in derlock mode.

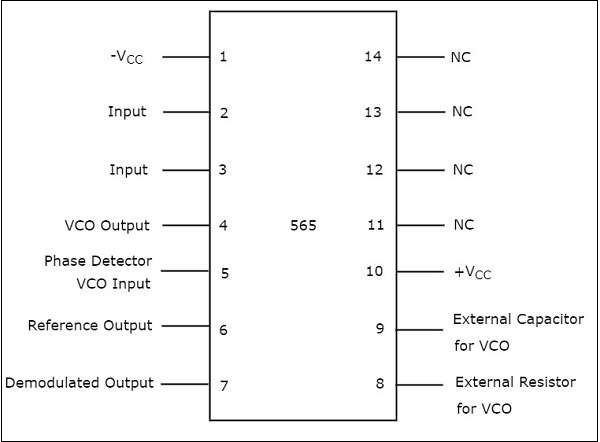

IC 565

Der IC 565 ist der am häufigsten verwendete IC mit Phasenregelkreis. Es handelt sich um ein 14-poliges Dual-Inline-Paket (DIP). Daspin diagram des IC 565 ist in der folgenden Abbildung dargestellt -

Der Zweck jedes Pins ist aus dem obigen Diagramm selbsterklärend. Von 14 Pins werden nur 10 Pins (Pin Nr. 1 bis 10) für den Betrieb von PLL verwendet. Die verbleibenden 4 Pins (Pin Nr. 11 bis 14) sind also mit NC (No Connection) gekennzeichnet.

Das VCOerzeugt einen Ausgang an Pin Nummer 4 des IC 565, wenn die Pin-Nummern 2 und 3 geerdet sind. Mathematisch können wir die Ausgangsfrequenz $ f_ {out} $ des VCO als schreiben.

$$ f_ {out} = \ frac {0.25} {R_VC_V} $$

wo,

$ R_ {V} $ ist der externe Widerstand, der an Pin 8 angeschlossen ist

$ C_ {V} $ ist der externe Kondensator, der an Pin 9 angeschlossen ist

Durch Auswahl der richtigen Werte für $ R_ {V} $ und $ C_ {V} $ können wir die Ausgangsfrequenz $ f_ {out} $ von VCO festlegen (bestimmen).

Pin numbers 4 and 5sind mit einem externen Draht kurzzuschließen, damit der Ausgang von VCO als einer der Eingänge des Phasendetektors angelegt werden kann.

IC 565 hat einen Innenwiderstand von $ 3,6K \ Omega $. Ein Kondensator C muss zwischen Pin Nr. 7 und 10 geschaltet werden, um a herzustellenlow pass filter mit diesem Innenwiderstand.

Beachten Sie, dass wir die Pins des IC 565 gemäß den Anforderungen ordnungsgemäß konfigurieren müssen.