VLSI Design - Digitales System

Bei der Integration in sehr großem Maßstab (VLSI) wird ein Prozess erstellt integrated circuit (IC) durch Kombination von Tausenden von transistorsin einen einzigen Chip. VLSI begann in den 1970er Jahren als komplexsemiconductor und communicationTechnologien wurden entwickelt. Dasmicroprocessor ist ein VLSI-Gerät.

Vor der Einführung der VLSI-Technologie verfügten die meisten ICs nur über begrenzte Funktionen. Einelectronic circuit könnte aus a bestehen CPU, ROM, RAM und andere glue logic. Mit VLSI können IC-Designer all dies in einem Chip hinzufügen.

Die Elektronikindustrie hat in den letzten Jahrzehnten ein phänomenales Wachstum erzielt, hauptsächlich aufgrund der raschen Fortschritte bei Integrationstechnologien in großem Maßstab und Systemdesignanwendungen. Mit dem Aufkommen von VLSI-Designs (Very Large Scale Integration) hat die Anzahl der Anwendungen von integrierten Schaltkreisen (ICs) in den Bereichen Hochleistungsrechnen, Steuerungen, Telekommunikation, Bild- und Videoverarbeitung sowie Unterhaltungselektronik sehr schnell zugenommen.

Die aktuellen Spitzentechnologien wie Video- und Mobilfunkkommunikation mit hoher Auflösung und niedriger Bitrate bieten den Endbenutzern eine erstaunliche Menge an Anwendungen, Rechenleistung und Portabilität. Dieser Trend wird voraussichtlich schnell zunehmen und sehr wichtige Auswirkungen auf das VLSI-Design und das Systemdesign haben.

VLSI Design Flow

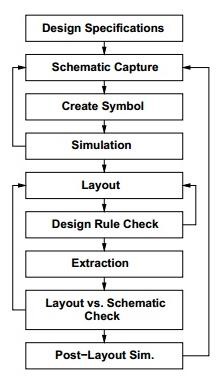

Der Entwurfsablauf für VLSI-IC-Schaltungen ist in der folgenden Abbildung dargestellt. Die verschiedenen Entwurfsebenen sind nummeriert und die Blöcke zeigen Prozesse im Entwurfsablauf.

Die Spezifikationen stehen an erster Stelle. Sie beschreiben abstrakt die Funktionalität, die Schnittstelle und die Architektur der zu entwerfenden digitalen IC-Schaltung.

Anschließend wird eine Verhaltensbeschreibung erstellt, um das Design hinsichtlich Funktionalität, Leistung, Einhaltung vorgegebener Standards und anderer Spezifikationen zu analysieren.

Die RTL-Beschreibung erfolgt mit HDLs. Diese RTL-Beschreibung wird simuliert, um die Funktionalität zu testen. Ab hier brauchen wir die Hilfe von EDA-Tools.

Die RTL-Beschreibung wird dann unter Verwendung von Logiksynthesewerkzeugen in eine Netzliste auf Gate-Ebene konvertiert. Eine Gatelevel-Netzliste ist eine Beschreibung der Schaltung in Bezug auf Gates und Verbindungen zwischen ihnen, die so hergestellt sind, dass sie den Zeit-, Leistungs- und Flächenspezifikationen entsprechen.

Schließlich wird ein physisches Layout erstellt, das überprüft und dann an die Fertigung gesendet wird.

Y-Diagramm

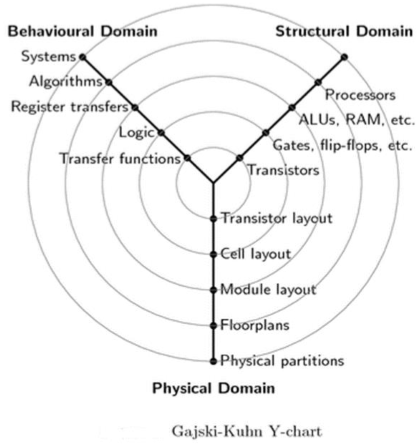

Das Gajski-Kuhn-Y-Diagramm ist ein Modell, das die Überlegungen beim Entwurf von Halbleiterbauelementen erfasst.

Die drei Domänen des Gajski-Kuhn-Y-Diagramms liegen auf Radialachsen. Jede der Domänen kann mithilfe konzentrischer Ringe in Abstraktionsebenen unterteilt werden.

Auf der obersten Ebene (äußerer Ring) betrachten wir die Architektur des Chips; Auf den unteren Ebenen (Innenringe) verfeinern wir das Design sukzessive zu einer detaillierteren Implementierung -

Das Erstellen einer Strukturbeschreibung aus einer Verhaltensbeschreibung wird durch die Prozesse der Synthese auf hoher Ebene oder der logischen Synthese erreicht.

Das Erstellen einer physikalischen Beschreibung aus einer strukturellen wird durch Layoutsynthese erreicht.

Design Hierarchie-Struktur

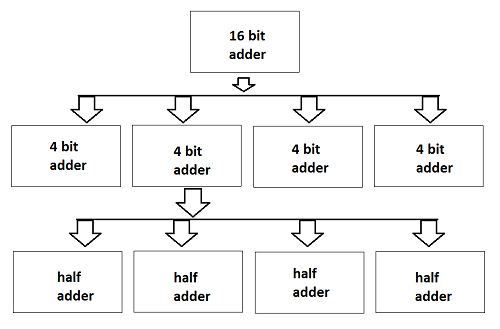

Die Designhierarchie beinhaltet das Prinzip "Teilen und Erobern". Es ist nichts anderes, als die Aufgabe in kleinere Aufgaben zu unterteilen, bis sie ihre einfachste Ebene erreicht hat. Dieses Verfahren ist am besten geeignet, da die letzte Entwicklung des Designs so einfach geworden ist, dass seine Herstellung einfacher wird.

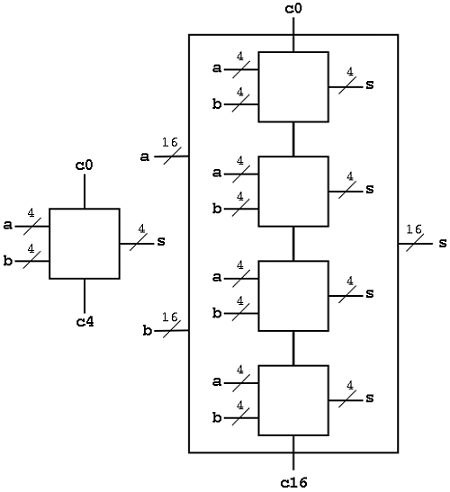

Wir können die gegebene Aufgabe in die Domäne des Entwurfsablaufprozesses (Verhalten, Struktur und Geometrie) entwerfen. Um dies zu verstehen, nehmen wir ein Beispiel für das Entwerfen eines 16-Bit-Addierers, wie in der folgenden Abbildung gezeigt.

Hier ist der gesamte Chip des 16-Bit-Addierers in vier Module von 4-Bit-Addierern unterteilt. Weiteres Teilen des 4-Bit-Addierers in 1-Bit-Addierer oder Halbaddierer. 1-Bit-Addition ist der einfachste Entwurfsprozess und seine interne Schaltung ist auch leicht auf dem Chip herzustellen. Wenn wir nun alle letzten vier Addierer verbinden, können wir einen 4-Bit-Addierer entwerfen und dann können wir einen 16-Bit-Addierer entwerfen.