VLSI Design - VHDL Einführung

VHDL steht für eine sehr schnelle Hardwarebeschreibungssprache für integrierte Schaltkreise. Es ist eine Programmiersprache, mit der ein digitales System anhand von Datenfluss, Verhalten und strukturellem Modellierungsstil modelliert wird. Diese Sprache wurde erstmals 1981 für das Verteidigungsministerium (DoD) im Rahmen des VHSIC-Programms eingeführt.

Ein Design beschreiben

In VHDL wird eine Entität verwendet, um ein Hardwaremodul zu beschreiben. Eine Entität kann beschrieben werden mit:

- Entitätserklärung

- Architecture

- Configuration

- Paketdeklaration

- Paketkörper

Mal sehen, was das sind?

Entitätserklärung

Es definiert die Namen, Eingangs- und Ausgangssignale und Modi eines Hardwaremoduls.

Syntax - -

entity entity_name is

Port declaration;

end entity_name;Eine Entitätsdeklaration sollte mit 'entity' beginnen und mit 'end' Schlüsselwörtern enden. Die Richtung wird eingegeben, ausgegeben oder eingegeben.

| Im | Port kann gelesen werden |

| aus | Port kann geschrieben werden |

| Inout | Port kann gelesen und geschrieben werden |

| Puffer | Port kann gelesen und geschrieben werden, es kann nur eine Quelle haben. |

Architecture - -

Architektur kann mit Struktur, Datenfluss, Verhalten oder gemischtem Stil beschrieben werden.

Syntax - -

architecture architecture_name of entity_name

architecture_declarative_part;

begin

Statements;

end architecture_name;Hier sollten wir den Entitätsnamen angeben, für den wir den Architekturkörper schreiben. Die Architekturanweisungen sollten sich innerhalb der Schlüsselwörter 'begin' und 'énd' befinden. Der deklarative Architekturteil kann Variablen, Konstanten oder Komponentendeklarationen enthalten.

Datenflussmodellierung

In diesem Modellierungsstil wird der Datenfluss durch die Entität unter Verwendung eines gleichzeitigen (parallelen) Signals ausgedrückt. Die gleichzeitigen Anweisungen in VHDL lauten WHEN und GENERATE.

Außerdem können Zuweisungen, die nur Operatoren (AND, NOT, +, *, sll usw.) verwenden, auch zum Erstellen von Code verwendet werden.

Schließlich kann auch eine spezielle Art von Zuweisung, BLOCK genannt, in dieser Art von Code verwendet werden.

Im gleichzeitigen Code kann Folgendes verwendet werden:

- Operators

- Die WHEN-Anweisung (WHEN / ELSE oder WITH / SELECT / WHEN);

- Die GENERATE-Anweisung;

- Die BLOCK-Anweisung

Verhaltensmodellierung

In diesem Modellierungsstil wird das Verhalten einer Entität als Satz von Anweisungen nacheinander in der angegebenen Reihenfolge ausgeführt. Nur Anweisungen, die in einem PROCESS, FUNCTION oder PROCEDURE platziert sind, sind sequentiell.

PROCESSES, FUNCTIONS und PROCEDURES sind die einzigen Codeabschnitte, die nacheinander ausgeführt werden.

Insgesamt stimmt jedoch jeder dieser Blöcke mit anderen außerhalb des Blocks platzierten Anweisungen überein.

Ein wichtiger Aspekt des Verhaltenscodes ist, dass er nicht auf sequentielle Logik beschränkt ist. In der Tat können wir damit sowohl sequentielle als auch kombinatorische Schaltungen bauen.

Die Verhaltensanweisungen lauten IF, WAIT, CASE und LOOP. VARIABLEN sind ebenfalls eingeschränkt und dürfen nur im sequentiellen Code verwendet werden. VARIABLE kann niemals global sein, daher kann sein Wert nicht direkt weitergegeben werden.

Strukturmodellierung

In dieser Modellierung wird eine Entität als eine Reihe miteinander verbundener Komponenten beschrieben. Eine Komponenteninstanziierungsanweisung ist eine gleichzeitige Anweisung. Daher ist die Reihenfolge dieser Aussagen nicht wichtig. Der strukturelle Modellierungsstil beschreibt nur eine Verbindung von Komponenten (als Black Boxes betrachtet), ohne dass dies ein Verhalten der Komponenten selbst oder der Entität impliziert, die sie gemeinsam darstellen.

In der Strukturmodellierung besteht der Architekturkörper aus zwei Teilen - dem deklarativen Teil (vor dem Beginn des Schlüsselworts) und dem Anweisungsteil (nach dem Beginn des Schlüsselworts).

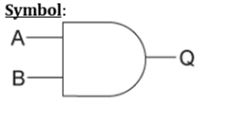

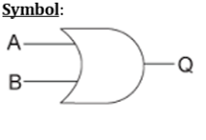

Logikbetrieb - UND TOR

| X. | Y. | Z. |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity and1 is

port(x,y:in bit ; z:out bit);

end and1;

architecture virat of and1 is

begin

z<=x and y;

end virat;Wellenformen

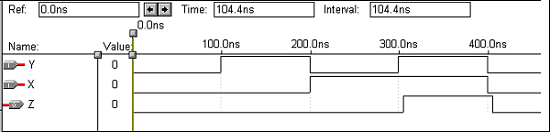

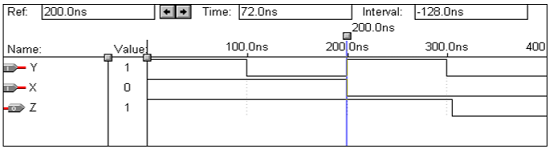

Logikbetrieb - ODER-Gatter

| X. | Y. | Z. |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity or1 is

port(x,y:in bit ; z:out bit);

end or1;

architecture virat of or1 is

begin

z<=x or y;

end virat;Wellenformen

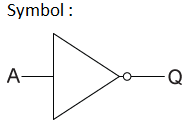

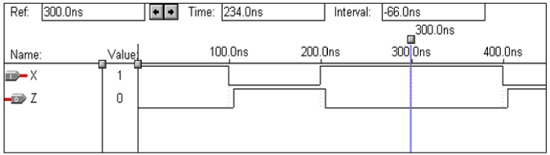

Logikbetrieb - NICHT Tor

| X. | Y. |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity not1 is

port(x:in bit ; y:out bit);

end not1;

architecture virat of not1 is

begin

y<=not x;

end virat;Wellenformen

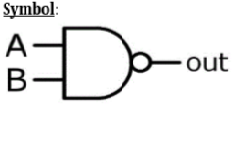

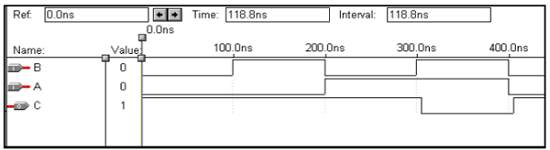

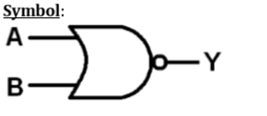

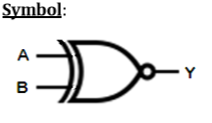

Logikbetrieb - NAND-Gatter

| X. | Y. | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nand1 is

port(a,b:in bit ; c:out bit);

end nand1;

architecture virat of nand1 is

begin

c<=a nand b;

end virat;Wellenformen

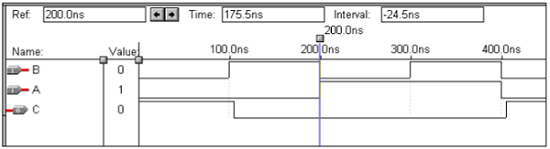

Logikbetrieb - NOR-Gatter

| X. | Y. | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nor1 is

port(a,b:in bit ; c:out bit);

end nor1;

architecture virat of nor1 is

begin

c<=a nor b;

end virat;Wellenformen

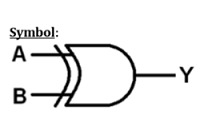

Logikbetrieb - XOR-Gatter

| X. | Y. | Z. |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xor1 is

port(a,b:in bit ; c:out bit);

end xor1;

architecture virat of xor1 is

begin

c<=a xor b;

end virat;Wellenformen

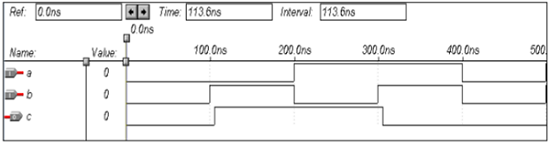

Logikbetrieb - X-NOR-Gatter

| X. | Y. | Z. |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xnor1 is

port(a,b:in bit ; c:out bit);

end xnor1;

architecture virat of xnor1 is

begin

c<=not(a xor b);

end virat;Wellenformen