VLSI Design - Sequentielle MOS-Logikschaltungen

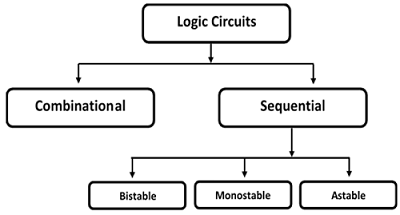

Logikschaltungen werden in zwei Kategorien unterteilt - (a) kombinatorische Schaltungen und (b) sequentielle Schaltungen.

In kombinatorischen Schaltungen hängt die Ausgabe nur vom Zustand der neuesten Eingaben ab.

In sequentiellen Schaltungen hängt der Ausgang nicht nur von den neuesten Eingängen ab, sondern auch vom Zustand früherer Eingänge. Sequenzielle Schaltungen enthalten Speicherelemente.

Es gibt drei Arten von sequentiellen Schaltungen:

Bistable- Bistabile Schaltkreise haben zwei stabile Betriebspunkte und befinden sich in einem der beiden Zustände. Beispiel - Speicherzellen, Latches, Flip-Flops und Register.

Monostable- Monostabile Schaltkreise haben nur einen stabilen Betriebspunkt, und selbst wenn sie vorübergehend in den entgegengesetzten Zustand versetzt werden, kehren sie rechtzeitig zu ihrem stabilen Betriebspunkt zurück. Beispiel: Timer, Impulsgeneratoren.

Astable- Stromkreise haben keinen stabilen Betriebspunkt und schwingen zwischen mehreren Zuständen. Beispiel - Ringoszillator.

CMOS-Logikschaltungen

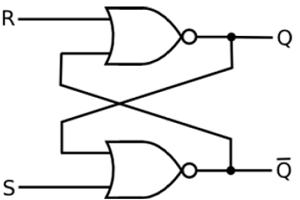

SR Latch basierend auf NOR Gate

Wenn der eingestellte Eingang (S) gleich logisch ist "1" und der Rücksetzeingang ist gleich logisch "0." dann wird der Ausgang Q zur Logik gezwungen "1". Während $ \ overline {Q} $ zur Logik gezwungen wird"0". Dies bedeutet, dass der SR-Latch unabhängig von seinem vorherigen Zustand gesetzt wird.

In ähnlicher Weise, wenn S gleich "0" ist und R gleich ist "1" dann wird der Ausgang Q dazu gezwungen "0" während $ \ overline {Q} $ dazu gezwungen wird "1". Dies bedeutet, dass der Latch unabhängig von seinem zuvor gehaltenen Zustand zurückgesetzt wird. Schließlich, wenn beide Eingänge S und R gleich Logik sind"1" dann werden beide Ausgänge zur Logik gezwungen "0" Dies steht im Widerspruch zur Komplementarität von Q und $ \ overline {Q} $.

Daher ist diese Eingangskombination im normalen Betrieb nicht zulässig. Die Wahrheitstabelle des NOR-basierten SR-Latch ist in der Tabelle angegeben.

| S. | R. | Q. | $ \ overline {Q} $ | Betrieb |

|---|---|---|---|---|

| 0 | 0 | Q. | $ \ overline {Q} $ | Halt |

| 1 | 0 | 1 | 0 | einstellen |

| 0 | 1 | 0 | 1 | Zurücksetzen |

| 1 | 1 | 0 | 0 | Nicht erlaubt |

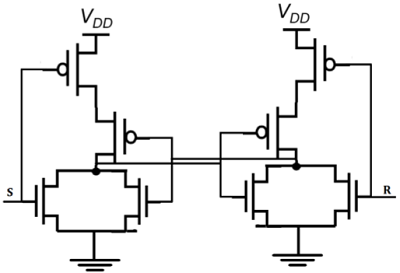

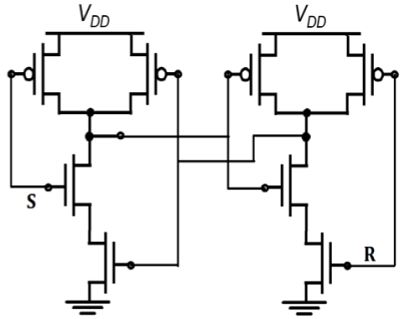

Der auf dem NOR-Gatter basierende CMOS-SR-Latch ist in der folgenden Abbildung dargestellt.

Wenn S gleich V OH und R gleich V OL ist , sind beide parallel geschalteten Transistoren M1 und M2 eingeschaltet. Die Spannung am Knoten $ \ overline {Q} $ nimmt einen logisch niedrigen Pegel von V OL = 0 an.

Gleichzeitig werden sowohl M3 als auch M4 ausgeschaltet, was zu einer logisch hohen Spannung V OH am Knoten Q führt. Wenn R gleich V OH und S gleich V OL ist , werden M1 und M2 ausgeschaltet und M3 und M4 eingeschaltet.

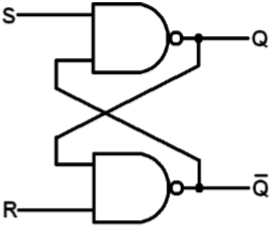

SR Latch basierend auf NAND Gate

Das Blockschaltbild und das Gate-Level-Schema des NAND-basierten SR-Latch sind in der Abbildung dargestellt. Die kleinen Kreise an den Eingangsanschlüssen S und R zeigen an, dass die Schaltung auf aktive niedrige Eingangssignale reagiert. Die Wahrheitstabelle des NAND-basierten SR-Latch ist in der Tabelle angegeben

| S. | R. | Q. | Q ' | |

| 0 | 0 | NC | NC | Keine Änderung. Latch blieb im gegenwärtigen Zustand. |

| 1 | 0 | 1 | 0 | Latch SET. |

| 0 | 1 | 0 | 1 | Latch RESET. |

| 1 | 1 | 0 | 0 | Ungültiger Zustand. |

Wenn S auf 0 geht (während R = 1), geht Q hoch, zieht $ \ overline {Q} $ niedrig und der Latch wechselt in den Set-Zustand

S = 0 dann ist Q = 1 (wenn R = 1)

Wenn R auf 0 geht (während S = 1), geht Q hoch, zieht $ \ overline {Q} $ niedrig und der Latch wird zurückgesetzt

R = 0 dann ist Q = 1 (wenn S = 1)

Der Haltezustand erfordert, dass sowohl S als auch R hoch sind. Wenn S = R = 0, ist die Ausgabe nicht zulässig, da dies zu einem unbestimmten Zustand führen würde. Der auf dem NAND-Gatter basierende CMOS-SR-Latch ist in der Abbildung dargestellt.

Der auf dem NAND-Gatter basierende nMOS SR-Latch mit Verarmungslast ist in der Abbildung dargestellt. Die Operation ähnelt der des CMOS NAND SR-Latch. Die CMOS-Schaltungsimplementierung weist eine geringe statische Verlustleistung und einen hohen Rauschabstand auf.

CMOS-Logikschaltungen

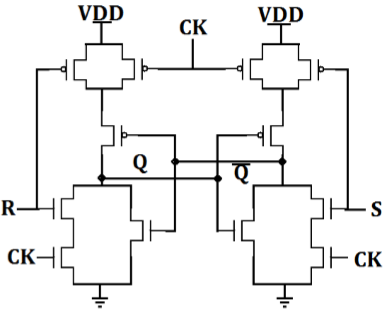

Getaktete SR-Verriegelung

Die Abbildung zeigt einen NOR-basierten SR-Latch mit einem hinzugefügten Takt. Der Latch reagiert nur dann auf die Eingänge S und R, wenn CLK hoch ist.

Wenn CLK niedrig ist, behält der Latch seinen aktuellen Zustand bei. Beachten Sie, dass Q den Zustand ändert -

- Wenn S während des positiven CLK hoch geht.

- An der führenden CLK-Flanke nach Änderungen in S & R während der niedrigen CLK-Zeit.

- Ein positiver Fehler in S, während CLK hoch ist

- Wenn R während des positiven CLK hoch geht.

Die CMOS-AOI-Implementierung eines getakteten NOR-basierten SR-Latch ist in der Abbildung dargestellt. Beachten Sie, dass nur 12 Transistoren erforderlich sind.

Wenn CLK niedrig ist, sind zwei Reihenanschlüsse in N Baum N offen und zwei parallele Transistoren in Baum P sind EIN, wodurch der Zustand in der Speicherzelle beibehalten wird.

Wenn der Takt hoch ist, wird die Schaltung einfach zu einem NOR-basierten CMOS-Latch, der auf die Eingänge S und R reagiert.

Clocked SR Latch based on NAND Gate

Die Schaltung ist mit vier NAND-Gattern implementiert. Wenn diese Schaltung mit CMOS implementiert ist, benötigt sie 16 Transistoren.

- Der Latch reagiert nur dann auf S oder R, wenn CLK hoch ist.

- Wenn sowohl die Eingangssignale als auch die CLK-Signale aktiv hoch sind: dh der Latch-Ausgang Q wird gesetzt, wenn CLK = "1" S = "1" und R = "0"

- In ähnlicher Weise wird der Latch zurückgesetzt, wenn CLK = "1", S = "0" und

Wenn CLK niedrig ist, behält der Latch seinen aktuellen Zustand bei.

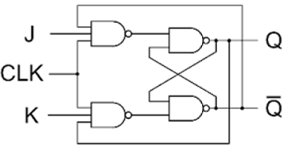

Getaktete JK-Verriegelung

Die obige Abbildung zeigt einen getakteten JK-Latch, der auf NAND-Gattern basiert. Der Nachteil eines SR-Latches besteht darin, dass sein Ausgangszustand unbestimmt wird, wenn sowohl S als auch R hoch sind. Der JK-Latch beseitigt dieses Problem, indem er eine Rückkopplung von Ausgabe zu Eingabe verwendet, so dass alle Eingangszustände der Wahrheitstabelle zulässig sind. Wenn J = K = 0 ist, behält der Latch seinen aktuellen Zustand bei.

Wenn J = 1 und K = 0 ist, wird der Latch bei der nächsten positiv verlaufenden Taktflanke gesetzt, dh Q = 1, $ \ overline {Q} $ = 0

Wenn J = 0 und K = 1 ist, wird der Latch bei der nächsten positiv verlaufenden Taktflanke zurückgesetzt, dh Q = 1 und $ \ overline {Q} $ = 0.

Wenn J = K = 1 ist, schaltet der Latch bei der nächsten positiv verlaufenden Taktflanke um

Die Funktionsweise des getakteten JK-Latch ist in der in der Tabelle angegebenen Wahrheitstabelle zusammengefasst.

J |

K |

Q |

$ \ overline {Q} $ | S |

R |

Q |

$ \ overline {Q} $ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | Halt |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | Zurücksetzen |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | einstellen |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | Umschalten |

| 1 | 0 | 1 | 0 | 0 | 1 |

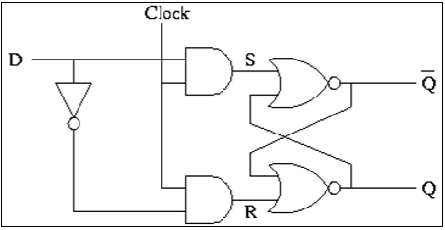

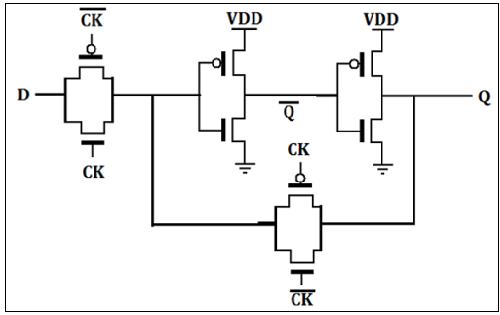

CMOS D Latch-Implementierung

Der D-Latch wird normalerweise mit TG-Schaltern (Transmission Gate) implementiert, wie in der Abbildung gezeigt. Der Eingang TG wird mit CLK aktiviert, während die Latch-Rückkopplungsschleife TG mit CLK aktiviert wird. Eingang D wird akzeptiert, wenn CLK hoch ist. Wenn CLK auf Low geht, ist der Eingang offen und der Latch wird mit den vorherigen Daten D gesetzt.