VLSI Design - FPGA-Technologie

FPGA - Einführung

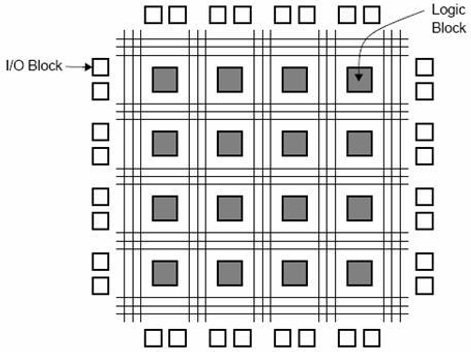

Die vollständige Form von FPGA ist “Field Programmable Gate Array”. Es enthält zehntausend bis mehr als eine Million Logikgatter mit programmierbarer Verbindung. Programmierbare Verbindungen stehen Benutzern oder Designern zur Verfügung, um bestimmte Funktionen einfach auszuführen. Ein typisches Modell eines FPGA-Chips ist in der angegebenen Abbildung dargestellt. Es gibt E / A-Blöcke, die entsprechend der Funktion entworfen und nummeriert sind. Für jedes Modul der Logikpegelzusammensetzung gibt esCLB’s (Configurable Logic Blocks).

CLB führt die dem Modul gegebene Logikoperation aus. Die Verbindung zwischen CLB- und E / A-Blöcken erfolgt mit Hilfe von horizontalen Routing-Kanälen, vertikalen Routing-Kanälen und PSM (Programmable Multiplexers).

Die Anzahl der darin enthaltenen CLBs entscheidet nur über die Komplexität des FPGA. Die Funktionen von CLBs und PSMs werden von VHDL oder einer anderen Hardware-Beschreibungssprache entwickelt. Nach der Programmierung werden CLB und PSM auf dem Chip platziert und über Routing-Kanäle miteinander verbunden.

Vorteile

- Es erfordert sehr wenig Zeit; vom Entwurfsprozess bis zum funktionalen Chip.

- Es sind keine physischen Herstellungsschritte erforderlich.

- Der einzige Nachteil ist, dass es teurer ist als andere Stile.

Gate Array Design

Das gate array (GA)belegt nach dem FPGA den zweiten Platz in Bezug auf die Fähigkeit zum schnellen Prototyping. Während die Benutzerprogrammierung für die Designimplementierung des FPGA-Chips wichtig ist, wird für GA das Design und die Verarbeitung von Metallmasken verwendet. Die Implementierung eines Gate-Arrays erfordert einen zweistufigen Herstellungsprozess.

Die erste Phase führt zu einer Anordnung von nicht festgeschriebenen Transistoren auf jedem GA-Chip. Diese nicht festgeschriebenen Chips können zur späteren Anpassung gespeichert werden. Dies wird durch Definieren der Metallverbindungen zwischen den Transistoren des Arrays abgeschlossen. Die Strukturierung der metallischen Verbindungen erfolgt am Ende des Chipherstellungsprozesses, so dass die Durchlaufzeit noch einige Tage bis einige Wochen betragen kann. Die folgende Abbildung zeigt die grundlegenden Verarbeitungsschritte für die Implementierung des Gate-Arrays.

Typische Gate-Array-Plattformen verwenden dedizierte Bereiche, die als Kanäle bezeichnet werden, für das Routing zwischen Zellen zwischen Zeilen oder Spalten von MOS-Transistoren. Sie vereinfachen die Verbindungen. Verbindungsmuster, die grundlegende Logikgatter ausführen, werden in einer Bibliothek gespeichert, die dann verwendet werden kann, um Zeilen von nicht festgeschriebenen Transistoren gemäß der Netzliste anzupassen.

In den meisten modernen GAs werden mehrere Metallschichten für das Kanalrouting verwendet. Durch die Verwendung mehrerer miteinander verbundener Schichten kann das Routing über die aktiven Zellenbereiche erreicht werden; Damit können die Routing-Kanäle wie bei SOG-Chips (Sea-of-Gates) entfernt werden. Hier ist die gesamte Chipoberfläche mit nicht festgeschriebenen nMOS- und pMOS-Transistoren bedeckt. Die benachbarten Transistoren können unter Verwendung einer Metallmaske angepasst werden, um grundlegende Logikgatter zu bilden.

Für das Routing zwischen Zellen müssen einige der nicht festgeschriebenen Transistoren geopfert werden. Dieser Entwurfsstil führt zu mehr Flexibilität für Verbindungen und normalerweise zu einer höheren Dichte. Der GA-Chipnutzungsfaktor wird durch die verwendete Chipfläche geteilt durch die gesamte Chipfläche gemessen. Es ist höher als das des FPGA und ebenso die Chipgeschwindigkeit.

Standardzellbasiertes Design

Ein standardmäßiges zellbasiertes Design erfordert die Entwicklung eines vollständigen benutzerdefinierten Maskensatzes. Die Standardzelle ist auch als Polyzelle bekannt. Bei diesem Ansatz werden alle üblicherweise verwendeten Logikzellen entwickelt, charakterisiert und in einer Standardzellbibliothek gespeichert.

Eine Bibliothek kann einige hundert Zellen enthalten, einschließlich Inverter, NAND-Gatter, NOR-Gatter, komplexe AOI-, OAI-Gatter, D-Latches und Flip-Flops. Jeder Gate-Typ kann in mehreren Versionen implementiert werden, um eine angemessene Fahrfähigkeit für verschiedene Fan-Outs bereitzustellen. Das Inverter-Gate kann eine Standardgröße, eine doppelte Größe und eine vierfache Größe haben, so dass der Chipdesigner die richtige Größe auswählen kann, um eine hohe Schaltungsgeschwindigkeit und Layoutdichte zu erhalten.

Jede Zelle wird nach verschiedenen Charakterisierungskategorien charakterisiert, wie z.

- Verzögerungszeit gegenüber Lastkapazität

- Schaltungssimulationsmodell

- Timing-Simulationsmodell

- Fehlersimulationsmodell

- Zellendaten für Ort und Route

- Maskendaten

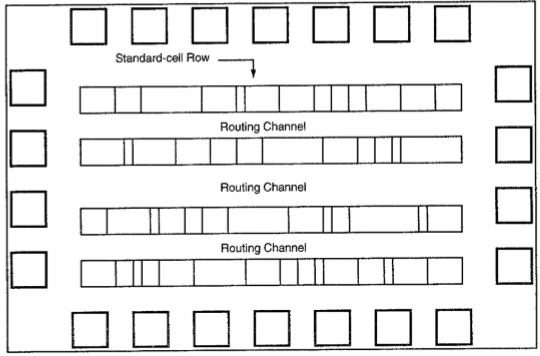

Für die automatische Platzierung der Zellen und das Routing wird jedes Zellenlayout mit einer festen Höhe entworfen, sodass mehrere Zellen nebeneinander begrenzt werden können, um Zeilen zu bilden. Die Strom- und Erdungsschienen verlaufen parallel zu den oberen und unteren Grenzen der Zelle. Damit teilen sich benachbarte Zellen einen gemeinsamen Leistungsbus und einen gemeinsamen Erdungsbus. Die folgende Abbildung ist ein Grundriss für das Design auf Basis von Standardzellen.

Volles kundenspezifisches Design

In einem vollständig benutzerdefinierten Design wird das gesamte Maskendesign ohne Verwendung einer Bibliothek neu erstellt. Die Entwicklungskosten dieses Designstils steigen. Daher wird das Konzept der Wiederverwendung von Konstruktionen immer bekannter, um die Konstruktionszykluszeit und die Entwicklungskosten zu reduzieren.

Das schwierigste vollständige benutzerdefinierte Design kann das Design einer Speicherzelle sein, sei es statisch oder dynamisch. Für das Logikchip-Design kann eine gute Verhandlung erzielt werden, indem eine Kombination verschiedener Designstile auf demselben Chip verwendet wird, dh Standardzellen, Datenpfadzellen undprogrammable logic arrays (PLAs).

Praktisch führt der Designer das vollständige benutzerdefinierte Layout durch, dh die Geometrie, Ausrichtung und Platzierung jedes Transistors. Die Designproduktivität ist normalerweise sehr gering. In der Regel einige zehn Transistoren pro Tag und Designer. Im digitalen CMOS VLSI wird aufgrund der hohen Arbeitskosten kaum ein vollständig kundenspezifisches Design verwendet. Diese Designstile umfassen das Design von Produkten mit hohem Volumen wie Speicherchips, Hochleistungsmikroprozessoren und FPGA.