Sirkuit Berurutan

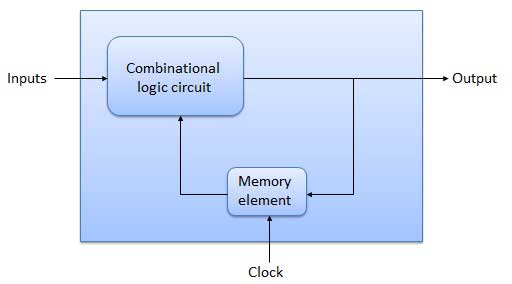

Sirkuit kombinasional tidak menggunakan memori apa pun. Oleh karena itu keadaan input sebelumnya tidak berpengaruh pada keadaan rangkaian saat ini. Tetapi rangkaian sekuensial memiliki memori sehingga keluaran dapat bervariasi berdasarkan masukan. Jenis sirkuit ini menggunakan input, output, clock, dan elemen memori sebelumnya.

Diagram blok

Flip Flop

Flip flop adalah rangkaian sekuensial yang umumnya mengambil sampel inputnya dan mengubah outputnya hanya pada waktu tertentu dan tidak terus menerus. Flip flop dikatakan sensitif terhadap tepi atau memicu tepi daripada memicu level seperti kait.

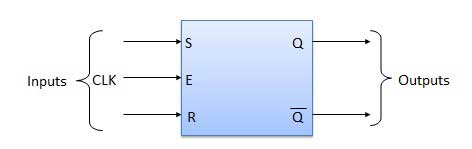

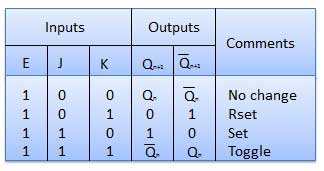

SR Flip Flop

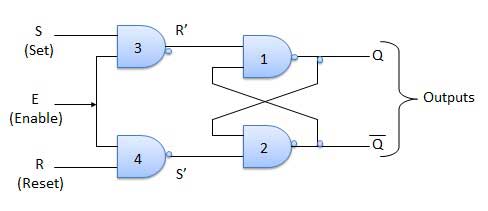

Ini pada dasarnya adalah kait SR menggunakan gerbang NAND dengan tambahan enablememasukkan. Ini juga disebut sebagai SR-FF yang dipicu level. Untuk ini, rangkaian keluaran akan berlangsung jika dan hanya jika masukan pengaktifan (E) diaktifkan. Singkatnya rangkaian ini akan beroperasi sebagai pengait SR jika E = 1 tetapi tidak ada perubahan pada keluaran jika E = 0.

Diagram Blok

Diagram Sirkuit

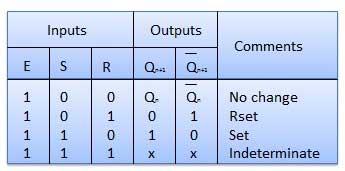

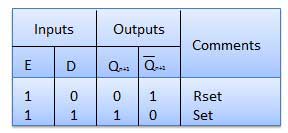

Meja kebenaran

Operasi

| SN | Kondisi | Operasi |

|---|---|---|

| 1 | S = R = 0 : No change | Jika S = R = 0 maka keluaran dari gerbang NAND 3 dan 4 dipaksa menjadi 1. Karenanya R 'dan S' keduanya akan sama dengan 1. Karena S 'dan R' adalah input dari kait SR dasar menggunakan gerbang NAND, tidak akan ada perubahan dalam status output. |

| 2 | S = 0, R = 1, E = 1 | Karena S = 0, keluaran NAND-3 yaitu R '= 1 dan E = 1 keluaran NAND-4 yaitu S' = 0. Maka Q n + 1 = 0 dan Q n + 1 bar = 1. Ini adalah kondisi reset. |

| 3 | S = 1, R = 0, E = 1 | Output dari NAND-3 yaitu R '= 0 dan output NAND-4 yaitu S' = 1. Oleh karena itu output dari kait SR NAND adalah Q n + 1 = 1 dan Q n + 1 bar = 0. Ini adalah kondisi reset. |

| 4 | S = 1, R = 1, E = 1 | Karena S = 1, R = 1 dan E = 1, output dari gerbang NAND 3 dan 4 keduanya adalah 0 yaitu S '= R' = 0. Oleh karena itu Race kondisi akan terjadi di kait NAND dasar. |

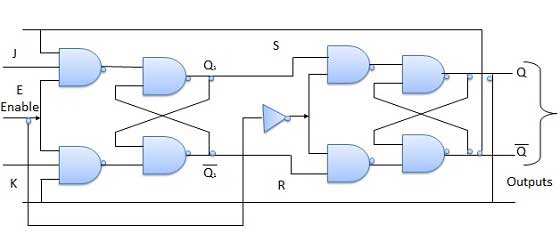

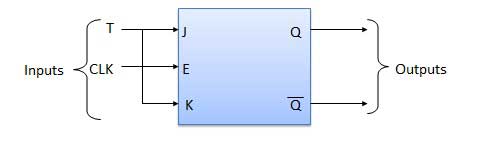

Tuan Budak JK Flip Flop

Master slave JK FF adalah kaskade dua SR FF dengan umpan balik dari keluaran kedua ke masukan pertama. Guru adalah tingkat positif yang dipicu. Tetapi karena kehadiran inverter di garis jam, budak akan merespons level negatif. Oleh karena itu ketika jam = 1 (level positif) master aktif dan budak tidak aktif. Sedangkan saat clock = 0 (level rendah) slave aktif dan master tidak aktif.

Diagram Sirkuit

Meja kebenaran

Operasi

| SN | Kondisi | Operasi |

|---|---|---|

| 1 | J = K = 0 (No change) | Ketika clock = 0, budak menjadi aktif dan master tidak aktif. Tetapi karena input S dan R tidak berubah, output slave juga tidak akan berubah. Oleh karena itu, keluaran tidak akan berubah jika J = K = 0. |

| 2 | J = 0 and K = 1 (Reset) | Jam = 1 - Master aktif, budak tidak aktif. Oleh karena itu keluaran dari master menjadi Q 1 = 0 dan Q 1 bar = 1. Artinya S = 0 dan R = 1. Jam = 0 - Budak aktif, master tidak aktif. Oleh karena itu, keluaran dari slave menjadi Q = 0 dan Q bar = 1. Lagi jam = 1 - Master aktif, budak tidak aktif. Oleh karena itu bahkan dengan keluaran yang diubah Q = 0 dan Q bar = 1 diumpankan kembali ke master, keluarannya akan menjadi Q1 = 0 dan Q1 bar = 1. Itu berarti S = 0 dan R = 1. Oleh karena itu dengan clock = 0 dan slave menjadi aktif, output slave akan tetap Q = 0 dan Q bar = 1. Jadi kita mendapatkan output yang stabil dari master slave. |

| 3 | J = 1 and K = 0 (Set) | Jam = 1 - Master aktif, budak tidak aktif. Oleh karena itu keluaran dari master menjadi Q 1 = 1 dan Q 1 bar = 0. Artinya S = 1 dan R = 0. Jam = 0 - Budak aktif, master tidak aktif. Oleh karena itu, keluaran dari slave menjadi Q = 1 dan Q bar = 0. Sekali lagi clock = 1 - maka dapat ditunjukkan bahwa output slave distabilkan ke Q = 1 dan Q bar = 0. |

| 4 | J = K = 1 (Toggle) | Jam = 1 - Master aktif, budak tidak aktif. Keluaran master akan diubah. Jadi S dan R juga akan dibalik. Jam = 0 - Budak aktif, master tidak aktif. Keluaran budak akan berubah. Output yang diubah ini dikembalikan ke input master. Tetapi karena clock = 0, master masih tidak aktif. Jadi itu tidak menanggapi keluaran yang diubah ini. Ini untuk menghindari beberapa toggling yang mengarah pada kondisi balapan mengelilingi. Master slave flip flop akan menghindari kondisi balapan di sekitar. |

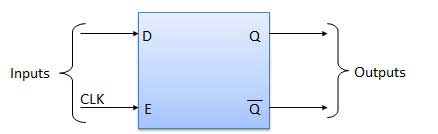

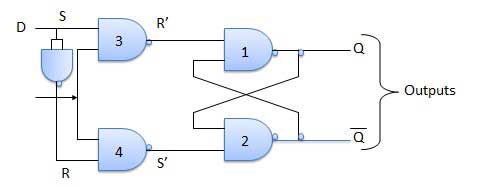

Penundaan Flip Flop / D Flip Flop

Delay Flip Flop atau D Flip Flop adalah kait SR berpagar sederhana dengan inverter NAND terhubung antara input S dan R. Ini hanya memiliki satu masukan. Data masukan muncul pada keluaran setelah beberapa waktu. Karena adanya delay data antara i / p dan o / p ini disebut delay flip flop. S dan R akan menjadi pelengkap satu sama lain karena inverter NAND. Maka S = R = 0 atau S = R = 1, kondisi input ini tidak akan pernah muncul. Masalah ini dapat dihindari dengan kondisi SR = 00 dan SR = 1.

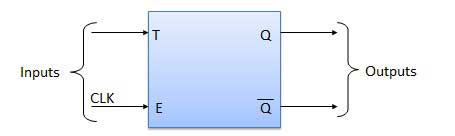

Diagram Blok

Diagram Sirkuit

Meja kebenaran

Operasi

| SN | Kondisi | Operasi |

|---|---|---|

| 1 | E = 0 | Latch dinonaktifkan. Karenanya tidak ada perubahan output. |

| 2 | E = 1 and D = 0 | Jika E = 1 dan D = 0 maka S = 0 dan R = 1. Oleh karena itu, terlepas dari keadaan sekarang, keadaan selanjutnya adalah Q n + 1 = 0 dan Q n + 1 bar = 1. Ini adalah kondisi reset. |

| 3 | E = 1 and D = 1 | Jika E = 1 dan D = 1, maka S = 1 dan R = 0. Ini akan mengatur latch dan Q n + 1 = 1 dan Q n + 1 bar = 0 terlepas dari keadaan saat ini. |

Toggle Flip Flop / T Flip Flop

Toggle flip flop pada dasarnya adalah JK flip flop dengan terminal J dan K yang terhubung secara permanen. Ini hanya memiliki masukan yang dilambangkan denganTseperti yang ditunjukkan pada Diagram Simbol. Simbol untuk T flip flop yang dipicu oleh tepi positif ditunjukkan pada Diagram Blok.

Diagram Simbol

Diagram Blok

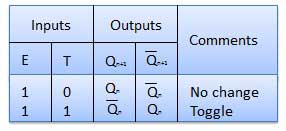

Meja kebenaran

Operasi

| SN | Kondisi | Operasi |

|---|---|---|

| 1 | T = 0, J = K = 0 | Output Q dan Q bar tidak akan berubah |

| 2 | T = 1, J = K = 1 | Output akan beralih sesuai dengan setiap tepi depan sinyal clock. |