Desain VLSI - MOS Inverter

Inverter benar-benar merupakan inti dari semua desain digital. Setelah operasi dan propertinya dipahami dengan jelas, merancang struktur yang lebih rumit seperti gerbang NAND, adder, pengganda, dan mikroprosesor sangat disederhanakan. Perilaku listrik dari rangkaian kompleks ini dapat hampir sepenuhnya diturunkan dengan mengekstrapolasi hasil yang diperoleh untuk inverter.

Analisis inverter dapat diperluas untuk menjelaskan perilaku gerbang yang lebih kompleks seperti NAND, NOR, atau XOR, yang pada gilirannya membentuk blok bangunan untuk modul seperti pengganda dan prosesor. Dalam bab ini, kami fokus pada satu inkarnasi tunggal gerbang inverter, yaitu inverter CMOS statis - atau singkatnya, inverter CMOS. Ini tentunya yang paling populer saat ini dan oleh karena itu perlu perhatian khusus kami.

Prinsip operasi

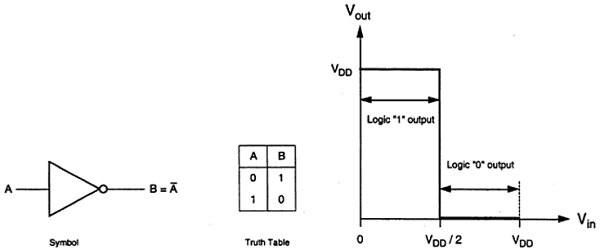

Simbol logika dan tabel kebenaran inverter ideal ditunjukkan pada gambar di bawah ini. Di sini A adalah input dan B adalah output terbalik yang diwakili oleh tegangan simpulnya. Dengan menggunakan logika positif, nilai Boolean dari logika 1 diwakili oleh V dd dan logika 0 diwakili oleh 0. V th adalah tegangan ambang inverter, yaitu V dd / 2, di mana V dd adalah tegangan output.

Output dialihkan dari 0 ke V dd ketika input kurang dari V th . Jadi, untuk 0 <V in <V th output sama dengan input logika 0 dan V th <V di <V dd sama dengan input logika 1 untuk inverter.

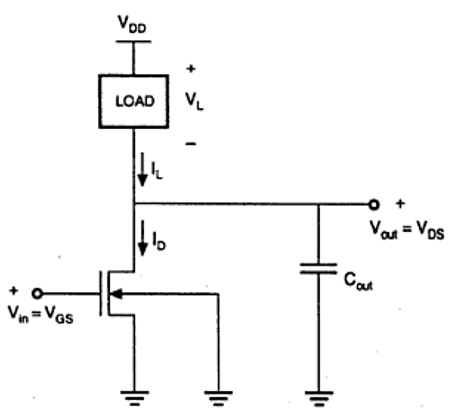

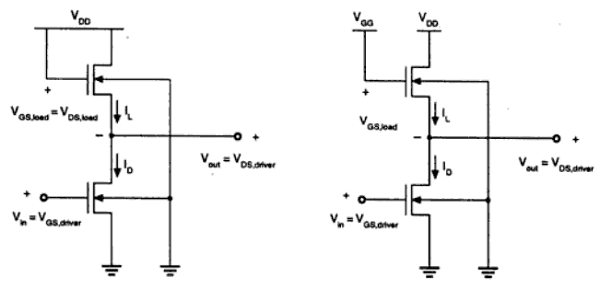

Karakteristik yang ditunjukkan pada gambar adalah ideal. Struktur rangkaian umum dari inverter nMOS ditunjukkan pada gambar di bawah ini.

Dari gambar yang diberikan, kita dapat melihat bahwa tegangan input inverter sama dengan tegangan gerbang ke sumber transistor nMOS dan tegangan keluaran inverter sama dengan tegangan drain ke sumber transistor nMOS. Sumber tegangan substrat nMOS juga disebut driver untuk transistor yang di-ground; jadi V SS = 0. Node keluaran dihubungkan dengan kapasitansi gabungan yang digunakan untuk VTC.

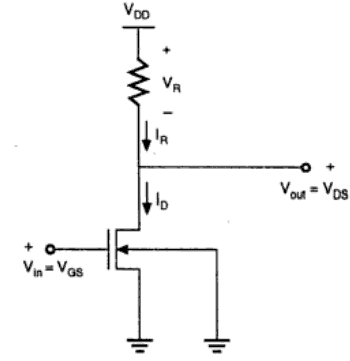

Inverter Beban Resistif

Struktur dasar inverter beban resistif ditunjukkan pada gambar di bawah ini. Di sini, tipe perangkat tambahan nMOS bertindak sebagai transistor driver. Beban terdiri dari linear resistor R sederhana L . Catu daya dari rangkaian tersebut adalah V DD dan arus drain I D adalah sama dengan arus beban I R .

Operasi Sirkuit

Ketika input transistor driver kurang dari tegangan ambang V TH (V dalam <V TH ), transistor driver berada di daerah cut-off dan tidak mengalirkan arus apapun. Jadi, penurunan tegangan pada resistor beban adalah NOL dan tegangan keluaran sama dengan V DD . Sekarang, ketika tegangan input meningkat lebih lanjut, transistor driver akan mulai mengalirkan arus bukan nol dan nMOS masuk ke wilayah saturasi.

Secara matematis,

$$ I_ {D} = \ frac {K_ {n}} {2} \ kiri [V_ {GS} -V_ {TO} \ kanan] ^ {2} $$

Meningkatkan tegangan input lebih lanjut, transistor driver akan masuk ke wilayah linier dan output dari transistor driver berkurang.

$$ I_ {D} = \ frac {K_ {n}} {2} 2 \ kiri [V_ {GS} -V_ {TO} \ kanan] V_ {DS} -V_ {DS} ^ {2} $$

VTC dari inverter beban resistif, ditunjukkan di bawah, menunjukkan mode operasi transistor driver dan titik tegangan.

Inverter dengan Beban MOSFET tipe N.

Keuntungan utama menggunakan MOSFET sebagai perangkat beban adalah area silikon yang ditempati oleh transistor lebih kecil dari area yang ditempati oleh beban resistif. Di sini, MOSFET adalah beban aktif dan inverter dengan beban aktif memberikan kinerja yang lebih baik daripada inverter dengan beban resistif.

Peningkatan Beban NMOS

Dua inverter dengan perangkat beban tipe peningkatan ditunjukkan pada gambar. Transistor beban dapat dioperasikan baik di wilayah saturasi atau di wilayah linier, tergantung pada tegangan bias yang diterapkan ke terminal gerbangnya. Inverter beban tambahan jenuh ditunjukkan pada gambar. (Sebuah). Hal ini membutuhkan suplai tegangan tunggal dan proses fabrikasi sederhana dan begitu V OH terbatas pada V DD - V T .

Inverter beban peningkatan linier ditunjukkan pada gambar. (b). Itu selalu beroperasi di wilayah linier; jadi level V OH sama dengan V DD .

Inverter beban linier memiliki margin kebisingan yang lebih tinggi dibandingkan dengan inverter peningkatan jenuh. Tapi, kelemahan dari inverter peningkatan linier adalah, ini membutuhkan dua catu daya terpisah dan kedua sirkuit menderita disipasi daya tinggi. Oleh karena itu, inverter tambahan tidak digunakan dalam aplikasi digital skala besar.

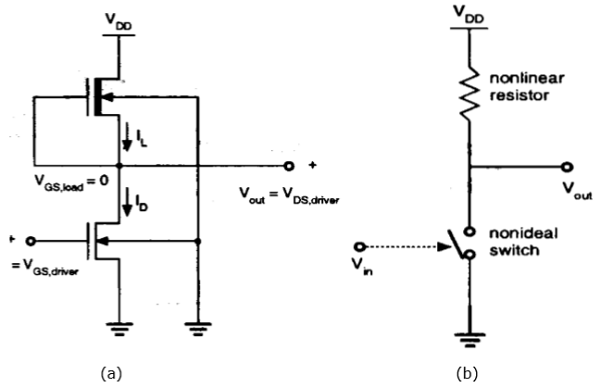

Beban Deplesi NMOS

Kelemahan dari enhancement load inverter dapat diatasi dengan menggunakan depletion load inverter. Dibandingkan dengan inverter beban tambahan, inverter beban deplesi memerlukan beberapa langkah fabrikasi lagi untuk implan saluran untuk menyesuaikan tegangan ambang beban.

Keuntungan dari inverter beban penipisan adalah - transisi VTC yang tajam, margin kebisingan yang lebih baik, catu daya tunggal, dan area tata letak keseluruhan yang lebih kecil.

Seperti yang ditunjukkan pada gambar, gerbang dan terminal sumber beban dihubungkan; Jadi, V GS = 0. Jadi, tegangan ambang beban adalah negatif. Karenanya,

$$ V_ {GS, load}> V_ {T, load} $$ terpenuhi

Oleh karena itu, perangkat beban selalu memiliki saluran konduksi terlepas dari level tegangan input dan output.

Ketika transistor beban berada di daerah saturasi, arus beban diberikan oleh

$$ I_ {D, load} = \ frac {K_ {n, load}} {2} \ left [-V_ {T, load} \ left (V_ {out} \ right) \ right] ^ {2} $ $

Ketika transistor beban berada di daerah linier, arus beban diberikan oleh

$$ I_ {D, muat} = \ frac {K_ {n, muat}} {2} \ kiri [2 \ kiri | V_ {T, muat} \ kiri (V_ {keluar} \ kanan) \ kanan |. \ Kiri (V_ {DD} -V_ {keluar} \ kanan) - \ kiri (V_ {DD} -V_ {keluar} \ kanan ) ^ {2} \ kanan] $$

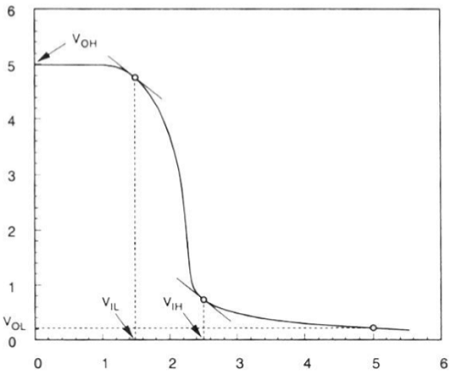

Karakteristik transfer tegangan inverter beban penipisan ditunjukkan pada gambar di bawah ini -

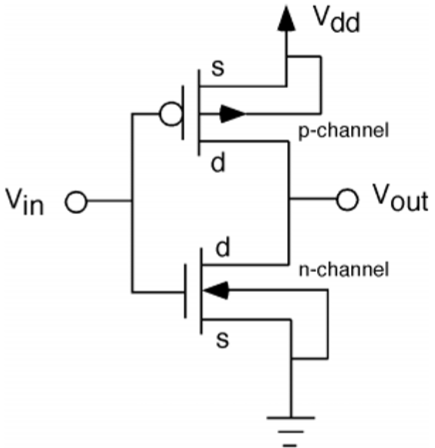

CMOS Inverter - Sirkuit, Operasi dan Deskripsi

Rangkaian inverter CMOS ditunjukkan pada gambar. Di sini, transistor nMOS dan pMOS bekerja sebagai transistor driver; ketika satu transistor ON, transistor lainnya OFF.

Konfigurasi ini disebut complementary MOS (CMOS). Input dihubungkan ke terminal gerbang kedua transistor sedemikian rupa sehingga keduanya dapat digerakkan langsung dengan tegangan input. Substrat nMOS disambungkan ke tanah dan substrat pMOS tersambung ke catu daya, V DD .

Jadi V SB = 0 untuk kedua transistor.

$$ V_ {GS, n} = V_ {in} $$

$$ V_ {DS, n} = V_ {out} $$

Dan,

$$ V_ {GS, p} = V_ {in} -V_ {DD} $$

$$ V_ {DS, p} = V_ {out} -V_ {DD} $$

Ketika masukan nMOS lebih kecil dari tegangan ambang (V dalam <V TO, n ), nMOS terputus dan pMOS berada dalam wilayah linier. Jadi, arus drain kedua transistor adalah nol.

$$ I_ {D, n} = I_ {D, p} = 0 $$

Oleh karena itu, tegangan keluaran V OH sama dengan tegangan suplai.

$$ V_ {keluar} = V_ {OH} = V_ {DD} $$

Ketika tegangan input lebih besar dari V DD + V TO, p , transistor pMOS berada di wilayah cutoff dan nMOS berada di wilayah linier, sehingga arus drain kedua transistor adalah nol.

$$ I_ {D, n} = I_ {D, p} = 0 $$

Oleh karena itu, tegangan keluaran V OL sama dengan nol.

$$ V_ {keluar} = V_ {OL} = 0 $$

NMOS beroperasi di wilayah saturasi jika V di > V TO dan jika kondisi berikut terpenuhi.

$$ V_ {DS, n} \ geq V_ {GS, n} -V_ {TO, n} $$

$$ V_ {keluar} \ geq V_ {dalam} -V_ {TO, n} $$

PMOS beroperasi di wilayah saturasi jika V di <V DD + V TO, p dan jika kondisi berikut terpenuhi.

$$ V_ {DS, p} \ leq V_ {GS, p} -V_ {TO, p} $$

$$ V_ {keluar} \ leq V_ {dalam} -V_ {TO, p} $$

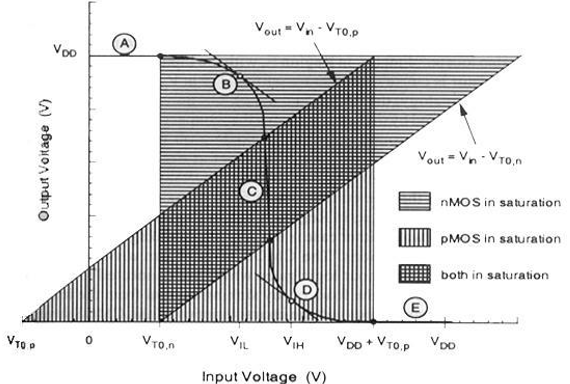

Untuk nilai tegangan input yang berbeda, daerah operasi terdaftar di bawah untuk kedua transistor.

| Wilayah | V in | V keluar | nMOS | pMOS |

|---|---|---|---|---|

| SEBUAH | <V TO, n | V OH | Memotong | Linear |

| B | V IL | Tinggi ≈ V OH | Kejenuhan | Linear |

| C | V th | V th | Kejenuhan | Kejenuhan |

| D | V IH | Rendah ≈ V OL | Linear | Kejenuhan |

| E | > (V DD + V TO, p ) | V OL | Linear | Memotong |

VTC CMOS ditunjukkan pada gambar di bawah ini -