Desain VLSI - Pengenalan VHDL

VHDL adalah singkatan dari bahasa deskripsi perangkat keras sirkuit terintegrasi berkecepatan sangat tinggi. Ini adalah bahasa pemrograman yang digunakan untuk memodelkan sistem digital dengan aliran data, gaya pemodelan perilaku dan struktural. Bahasa ini pertama kali diperkenalkan pada tahun 1981 untuk departemen Pertahanan (DoD) di bawah program VHSIC.

Menjelaskan Desain

Dalam VHDL, entitas digunakan untuk mendeskripsikan modul perangkat keras. Suatu entitas dapat dijelaskan menggunakan,

- Deklarasi entitas

- Architecture

- Configuration

- Deklarasi paket

- Isi paket

Mari kita lihat apa ini?

Deklarasi Entitas

Ini mendefinisikan nama, sinyal input output dan mode modul perangkat keras.

Syntax -

entity entity_name is

Port declaration;

end entity_name;Deklarasi entitas harus dimulai dengan 'entitas' dan diakhiri dengan kata kunci 'akhir'. Arahnya akan menjadi input, output atau inout.

| Di | Port bisa dibaca |

| Di luar | Port dapat ditulis |

| Masuk | Port dapat dibaca dan ditulis |

| Penyangga | Port dapat dibaca dan ditulis, hanya dapat memiliki satu sumber. |

Architecture -

Arsitektur dapat digambarkan dengan menggunakan struktur, aliran data, perilaku atau gaya campuran.

Syntax -

architecture architecture_name of entity_name

architecture_declarative_part;

begin

Statements;

end architecture_name;Di sini, kita harus menentukan nama entitas yang akan kita tuliskan badan arsitekturnya. Pernyataan arsitektur harus berada di dalam kata kunci 'begin' dan 'énd'. Bagian deklaratif arsitektur dapat berisi variabel, konstanta, atau deklarasi komponen.

Pemodelan Arus Data

Dalam gaya pemodelan ini, aliran data melalui entitas diekspresikan menggunakan sinyal konkuren (paralel). Pernyataan serentak di VHDL adalah WHEN dan GENERATE.

Selain itu, tugas yang hanya menggunakan operator (AND, NOT, +, *, sll, dll.) Juga dapat digunakan untuk membuat kode.

Terakhir, jenis tugas khusus, yang disebut BLOK, juga dapat digunakan dalam kode jenis ini.

Dalam kode bersamaan, berikut ini dapat digunakan -

- Operators

- Pernyataan WHEN (WHEN / ELSE atau WITH / SELECT / WHEN);

- Pernyataan GENERATE;

- Pernyataan BLOK

Pemodelan Perilaku

Dalam gaya pemodelan ini, perilaku entitas sebagai kumpulan pernyataan dijalankan secara berurutan dalam urutan yang ditentukan. Hanya pernyataan yang ditempatkan di dalam PROCESS, FUNCTION, atau PROCEDURE yang berurutan.

PROSES, FUNGSI, dan PROSEDUR adalah satu-satunya bagian kode yang dijalankan secara berurutan.

Namun, secara keseluruhan, salah satu blok ini masih bersamaan dengan pernyataan lain yang ditempatkan di luarnya.

Satu aspek penting dari kode perilaku adalah tidak terbatas pada logika sekuensial. Memang, dengan itu, kita bisa membangun rangkaian sekuensial maupun rangkaian kombinasional.

Pernyataan perilaku adalah IF, WAIT, CASE, dan LOOP. VARIABEL juga dibatasi dan hanya digunakan dalam kode berurutan. VARIABEL tidak pernah bisa mendunia, jadi nilainya tidak bisa disebarkan secara langsung.

Pemodelan Struktural

Dalam pemodelan ini, entitas digambarkan sebagai sekumpulan komponen yang saling berhubungan. Pernyataan instansiasi komponen adalah pernyataan bersamaan. Oleh karena itu, urutan pernyataan ini tidak penting. Gaya pemodelan struktural hanya menggambarkan interkoneksi komponen (dilihat sebagai kotak hitam), tanpa menyiratkan perilaku komponen itu sendiri atau entitas yang mereka wakili secara kolektif.

Dalam pemodelan struktural, badan arsitektur terdiri dari dua bagian - bagian deklaratif (sebelum kata kunci dimulai) dan bagian pernyataan (setelah kata kunci dimulai).

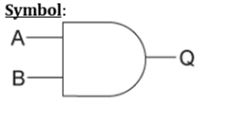

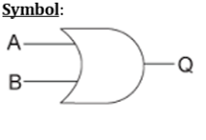

Operasi Logika - DAN GERBANG

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity and1 is

port(x,y:in bit ; z:out bit);

end and1;

architecture virat of and1 is

begin

z<=x and y;

end virat;Bentuk gelombang

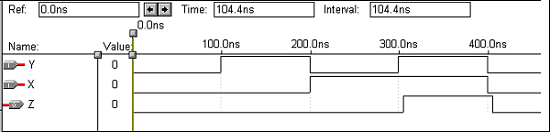

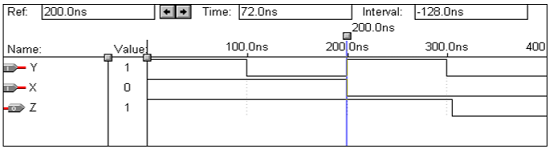

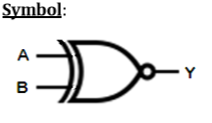

Operasi Logika - OR Gerbang

| X | Y | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity or1 is

port(x,y:in bit ; z:out bit);

end or1;

architecture virat of or1 is

begin

z<=x or y;

end virat;Bentuk gelombang

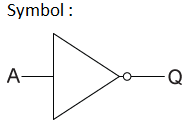

Operasi Logika - BUKAN Gerbang

| X | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity not1 is

port(x:in bit ; y:out bit);

end not1;

architecture virat of not1 is

begin

y<=not x;

end virat;Bentuk gelombang

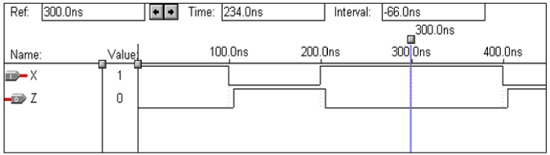

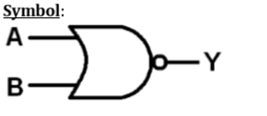

Operasi Logika - Gerbang NAND

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nand1 is

port(a,b:in bit ; c:out bit);

end nand1;

architecture virat of nand1 is

begin

c<=a nand b;

end virat;Bentuk gelombang

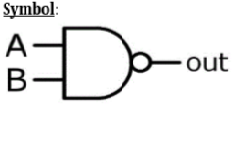

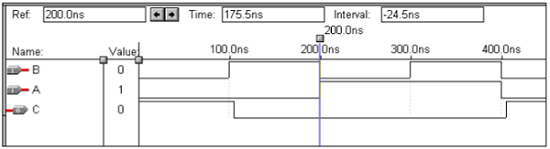

Operasi Logika - Gerbang NOR

| X | Y | z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity nor1 is

port(a,b:in bit ; c:out bit);

end nor1;

architecture virat of nor1 is

begin

c<=a nor b;

end virat;Bentuk gelombang

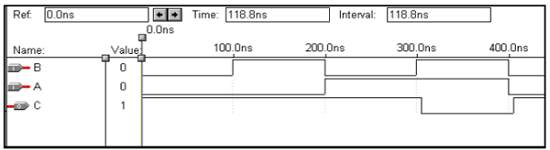

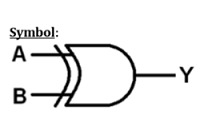

Operasi Logika - Gerbang XOR

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xor1 is

port(a,b:in bit ; c:out bit);

end xor1;

architecture virat of xor1 is

begin

c<=a xor b;

end virat;Bentuk gelombang

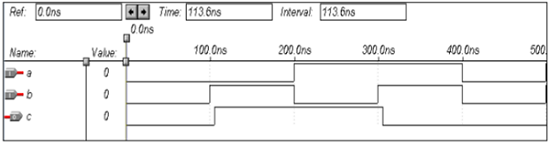

Operasi Logika - Gerbang X-NOR

| X | Y | Z |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

VHDL Code:

Library ieee;

use ieee.std_logic_1164.all;

entity xnor1 is

port(a,b:in bit ; c:out bit);

end xnor1;

architecture virat of xnor1 is

begin

c<=not(a xor b);

end virat;Bentuk gelombang