VLSI設計-デジタルシステム

超大規模集積回路(VLSI)は、 integrated circuit (IC)数千を組み合わせることによって transistorsシングルチップに。VLSIは1970年代に複雑になったときに始まりましたsemiconductor そして communication技術が開発されていました。ザ・microprocessor VLSIデバイスです。

VLSI技術が導入される前は、ほとんどのICは実行できる機能のセットが限られていました。アンelectronic circuit で構成されている可能性があります CPU, ROM, RAM およびその他 glue logic。VLSIを使用すると、IC設計者はこれらすべてを1つのチップに追加できます。

エレクトロニクス業界は、主に大規模な統合技術とシステム設計アプリケーションの急速な進歩により、過去数十年にわたって驚異的な成長を遂げてきました。超大規模集積回路(VLSI)設計の出現により、高性能コンピューティング、制御、電気通信、画像およびビデオ処理、および家庭用電化製品における集積回路(IC)のアプリケーションの数は非常に速いペースで増加しています。

高解像度、低ビットレートのビデオおよびセルラー通信などの現在の最先端技術は、エンドユーザーに驚異的な量のアプリケーション、処理能力、および移植性を提供します。この傾向は急速に拡大すると予想され、VLSI設計とシステム設計に非常に重要な影響を及ぼします。

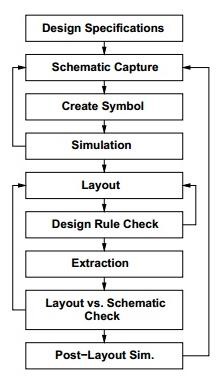

VLSI設計フロー

VLSIIC回路の設計フローを下図に示します。設計のさまざまなレベルに番号が付けられ、ブロックは設計フローのプロセスを示しています。

仕様が最初に来て、それらは設計されるデジタルIC回路の機能、インターフェース、およびアーキテクチャを抽象的に説明します。

次に、動作の説明が作成され、機能、パフォーマンス、特定の標準への準拠、およびその他の仕様の観点から設計が分析されます。

RTLの記述はHDLを使用して行われます。このRTL記述は、機能をテストするためにシミュレートされています。ここから先は、EDAツールの助けが必要です。

次に、RTL記述は、論理合成ツールを使用してゲートレベルのネットリストに変換されます。ゲートレベルのネットリストは、ゲートとそれらの間の接続に関する回路の説明であり、タイミング、電力、および面積の仕様を満たすように作成されています。

最後に、物理的なレイアウトが作成され、検証されてから製造に送られます。

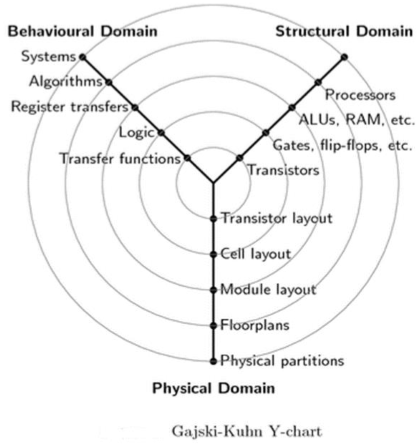

Yチャート

Gajski-Kuhn Yチャートは、半導体デバイスを設計する際の考慮事項を捉えたモデルです。

Gajski-Kuhn Yチャートの3つのドメインは、放射軸上にあります。各ドメインは、同心円状のリングを使用して、抽象化のレベルに分割できます。

トップレベル(外輪)では、チップのアーキテクチャを検討します。下位レベル(内輪)では、設計を次々と改良して、より詳細な実装にします。

動作記述から構造記述を作成することは、高位合成または論理合成のプロセスを通じて実現されます。

構造的な記述から物理的な記述を作成することは、レイアウト合成によって実現されます。

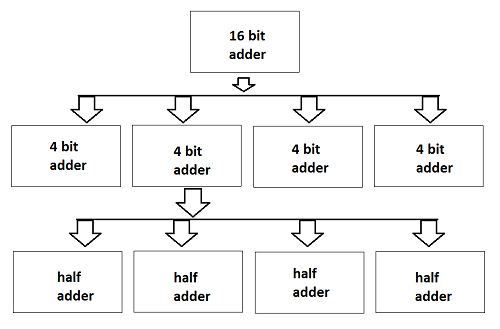

設計階層-構造

設計階層には、「分割統治」の原則が含まれます。最も単純なレベルに達するまで、タスクをより小さなタスクに分割することに他なりません。このプロセスは、設計の最後の進化が非常に単純になり、製造が容易になるため、最も適しています。

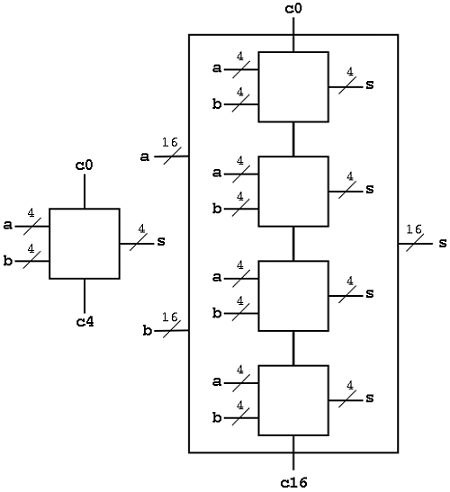

与えられたタスクを設計フロープロセスのドメイン(動作、構造、および幾何学的)に設計できます。これを理解するために、次の図に示すように、16ビット加算器を設計する例を見てみましょう。

ここでは、16ビット加算器のチップ全体が4ビット加算器の4つのモジュールに分割されています。さらに、4ビット加算器を1ビット加算器または半加算器に分割します。1ビットの加算は最も単純な設計プロセスであり、その内部回路もチップ上で簡単に製造できます。これで、最後の4つの加算器すべてを接続して、4ビット加算器を設計できます。次に進むと、16ビット加算器を設計できます。