VLSI設計-シーケンシャルMOS論理回路

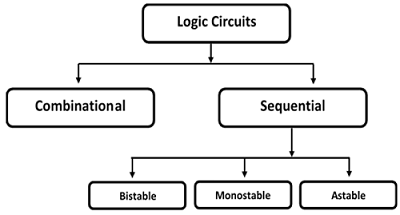

論理回路は、(a)組み合わせ回路と(b)順序回路の2つのカテゴリに分類されます。

組み合わせ回路では、出力は最新の入力の状態にのみ依存します。

シーケンシャル回路では、出力は最新の入力だけでなく、以前の入力の状態にも依存します。順序回路にはメモリ要素が含まれています。

順序回路には3つのタイプがあります-

Bistable−双安定回路には2つの安定した動作点があり、どちらの状態にもなります。例-メモリセル、ラッチ、フリップフロップ、およびレジスタ。

Monostable−単安定回路には、安定した動作点が1つしかなく、一時的に反対の状態に摂動された場合でも、時間内に安定した動作点に戻ります。例:タイマー、パルスジェネレータ。

Astable−回路には安定した動作点がなく、いくつかの状態間で発振します。例-リングオシレータ。

CMOS論理回路

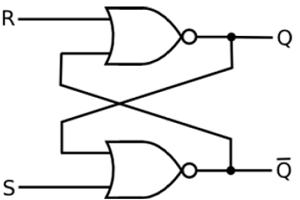

NORゲートに基づくSRラッチ

設定された入力(S)がロジックに等しい場合 "1" リセット入力はロジックと同じです "0." 次に、出力Qは強制的にロジック化されます "1"。$ \ overline {Q} $はロジックに強制されますが"0"。これは、以前の状態に関係なく、SRラッチが設定されることを意味します。

同様に、Sが「0」に等しく、Rがに等しい場合 "1" 次に、出力Qは強制されます "0" $ \ overline {Q} $は強制されますが "1"。これは、以前に保持されていた状態に関係なく、ラッチがリセットされることを意味します。最後に、入力SとRの両方がロジックに等しい場合"1" その後、両方の出力が強制的にロジック化されます "0" これは、Qと$ \ overline {Q} $の相補性と矛盾します。

したがって、この入力の組み合わせは、通常の操作では許可されていません。NORベースのSRラッチの真理値表を表に示します。

| S | R | Q | $ \ overline {Q} $ | 操作 |

|---|---|---|---|---|

| 0 | 0 | Q | $ \ overline {Q} $ | ホールド |

| 1 | 0 | 1 | 0 | セットする |

| 0 | 1 | 0 | 1 | リセット |

| 1 | 1 | 0 | 0 | 禁止されている |

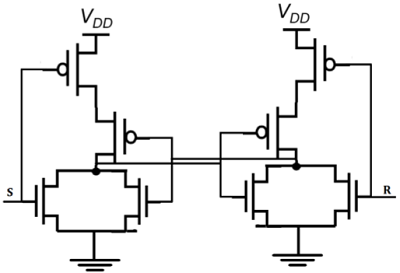

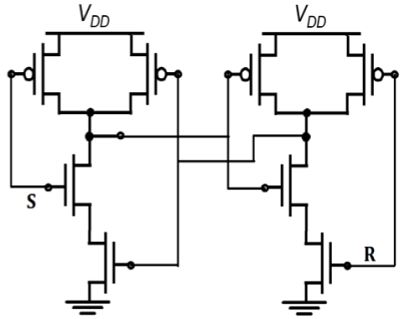

NORゲートに基づくCMOSSRラッチを下図に示します。

SはVに等しい場合OH及びRはVに等しいOL、M1とM2がオンになり、並列接続されたトランジスタの両方。ノード$ \ overline {Q} $の電圧は、論理的に低いレベルのV OL = 0を想定しています。

同時に、M3とM4の両方がどの論理ハイ電圧Vで結果、オフさOH RはVに等しい場合ノードQにおけるOH、SはVに等しいOL、M1及びM2はオフとM3とM4がオンになっています。

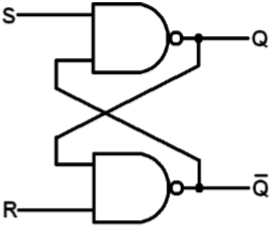

NANDゲートに基づくSRラッチ

NANDベースのSRラッチのブロック図とゲートレベルの回路図を図に示します。SおよびR入力端子の小さな円は、回路がアクティブな低入力信号に応答することを表しています。NANDベースのSRラッチの真理値表を表に示します。

| S | R | Q | Q ' | |

| 0 | 0 | NC | NC | 変化なし。ラッチは現在の状態のままでした。 |

| 1 | 0 | 1 | 0 | ラッチセット。 |

| 0 | 1 | 0 | 1 | ラッチリセット。 |

| 1 | 1 | 0 | 0 | 条件が無効です。 |

Sが0になると(R = 1の場合)、Qがハイになり、$ \ overline {Q} $がローになり、ラッチがセット状態になります。

S = 0 次にQ = 1 (R =の場合 1)

Rが0になると(S = 1の場合)、Qがハイになり、$ \ overline {Q} $がローになり、ラッチがリセットされます。

R = 0 次にQ = 1 (S =の場合 1)

ホールド状態では、SとRの両方がハイである必要があります。S = R = 0の場合、状態が不確定になるため、出力は許可されません。NANDゲートに基づくCMOSSRラッチを図に示します。

NANDゲートに基づく空乏負荷nMOSSRラッチを図に示します。操作は、CMOS NANDSRラッチの操作と同様です。CMOS回路の実装は、静的消費電力が低く、ノイズマージンが高くなっています。

CMOS論理回路

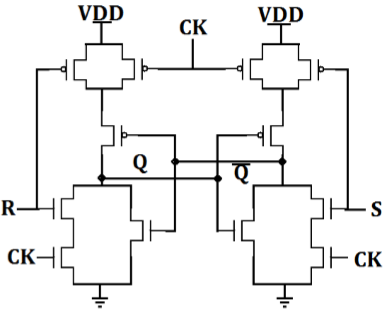

クロックドSRラッチ

この図は、クロックが追加されたNORベースのSRラッチを示しています。ラッチは、CLKがハイの場合にのみ入力SとRに応答します。

CLKがローの場合、ラッチは現在の状態を保持します。Qが状態を変化させることを観察します-

- 正のCLK中にSがハイになったとき。

- CLKロー時間中にS&Rが変化した後のCLKの立ち上がりエッジ。

- CLKがハイのときのSの正のグリッチ

- 正のCLK中にRがハイになったとき。

クロックドNORベースのSRラッチのCMOSAOI実装を図に示します。必要なトランジスタは12個だけであることに注意してください。

CLKがローの場合、NツリーNの2つの直列端子が開いており、ツリーPの2つの並列トランジスタがオンになっているため、メモリセルの状態が保持されます。

クロックがハイの場合、回路は入力SとRに応答するNORベースのCMOSラッチになります。

Clocked SR Latch based on NAND Gate

回路は4つのNANDゲートで実装されています。この回路がCMOSで実装されている場合、16個のトランジスタが必要です。

- ラッチは、CLKがハイの場合にのみSまたはRに応答します。

- 入力信号とCLK信号の両方がアクティブハイの場合、つまり、CLK = "1" S = "1"およびR = "0"の場合、ラッチ出力Qが設定されます。

- 同様に、CLK = "1"、S = "0"の場合、ラッチはリセットされます。

CLKがローの場合、ラッチは現在の状態を保持します。

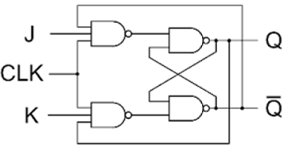

クロックドJKラッチ

上の図は、NANDゲートに基づくクロック付きJKラッチを示しています。SRラッチの欠点は、SとRの両方がハイの場合、その出力状態が不確定になることです。JKラッチは、出力から入力へのフィードバックを使用してこの問題を排除し、真理値表のすべての入力状態が許容されるようにします。J = K = 0の場合、ラッチは現在の状態を保持します。

J = 1およびK = 0の場合、ラッチは次の正方向のクロックエッジ、つまりQ = 1、$ \ overline {Q} $ = 0に設定されます。

J = 0およびK = 1の場合、ラッチは次の正方向のクロックエッジ、つまりQ = 1および$ \ overline {Q} $ = 0でリセットされます。

J = K = 1の場合、ラッチは次の正方向のクロックエッジでトグルします

クロックドJKラッチの動作は、表に示されている真理値表に要約されています。

J |

K |

Q |

$ \ overline {Q} $ | S |

R |

Q |

$ \ overline {Q} $ | Operation |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | ホールド |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | リセット |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | セットする |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | トグル |

| 1 | 0 | 1 | 0 | 0 | 1 |

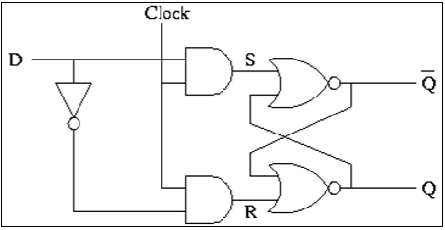

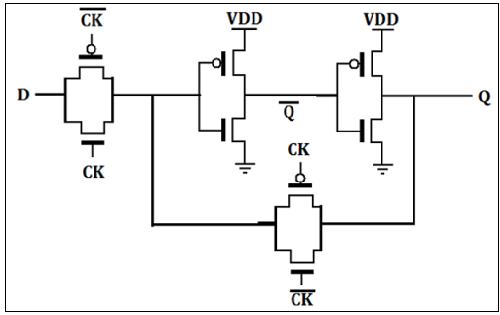

CMOSDラッチの実装

Dラッチは通常、図に示すようにトランスミッションゲート(TG)スイッチで実装されます。入力TGはCLKでアクティブになり、ラッチフィードバックループTGはCLKでアクティブになります。入力Dは、CLKがハイのときに受け入れられます。CLKがローになると、入力が開回路になり、ラッチは前のデータDで設定されます。